лаба 4

.docxФедеральное агентство связи

Ордена трудового красного знамени

Федеральное государственное образовательное

Бюджетное

Учреждение высшего профессионального образования

Московский Технический Университет связи и информатики

Кафедра МКИТ

Лабораторная работа №4 по дисциплине «Вычислительная техника»

«Сумматоры»

Выполнила

Студентка группы БСТ1904

Пантелеева К.А.

Проверил:

асс. Каф. Джабраилов Х.А.

Москва 2020г.

Оглавление

1 Цель работы 3

2.1 Краткие теоретические сведения 3

2.2 Схема сумматора 4

2.3 Временная диаграмма 4

Список использованных источников 5

1 Цель работы

Изучить схемы сумматоров и принципы их работы. Построить трёхразрядный сумматор на элементах «сложение по модулю два»

2 Ход работы

2.1 Краткие теоретические сведения

Сумматором называется функциональный блок аппаратных средств вычислительной техники, предназначенный для сложения двух n-разрядных слов (чисел). Операция вычитания в сумматоре выполняется сложением слов в обратном или дополнительном коде. Операции умножения и деления выполняются многократным сложением и сдвигом.

Сумматор является частью арифметико-логического устройства, функция сумматора обозначается буквами SM или ∑.

Сумматор, в общем случае, состоит из функциональных узлов – одноразрядных сумматоров, выполняющих все действия по сложению значений одноименных разрядов двух чисел (операндов).

Сумматоры классифицируются по следующим признакам: способу сложения (параллельные, последовательные и параллельно-последовательные); числу входов(полусумматоры, одноразрядные и многоразрядные сумматоры);организации хранения результата сложения (комбинационные, накапливающие, комбинированные); организации переноса между разрядами — с последовательным, сквозным, параллельным или комбинированным переносом; системе счисления (позиционные , т.е. двоичные, двоично-десятичные, троичные) и непозиционные, например, в системе остаточных классов); разрядности (длине) операндов (от 4 до 64 и более); способу представления отрицательных чисел (в обратном или дополнительном кодах, а также в их модификациях); времени сложения (синхронные, асинхронные).

2.2 Схема сумматора

На рисунке 1 представлена схема трёхразрядного сумматора на элементах «сложение по модулю два», построенная в программе Multisim.

Рисунок 1 – Сумматор

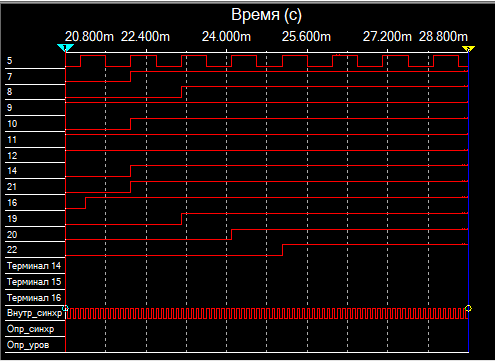

2.3 Временная диаграмма

На рисунке 2 представленная временная диаграмма работы построенного сумматора.

Рисунок 2 - Временная диаграмма

Список использованных источников

1) ГОСТ 7.32-2017 СИБИД. Отчет о научно-исследовательской работе. Структура и правила оформления (с Поправкой)

2) ГОСТ 7.82-2001 СИБИД. Библиографическая запись. Библиографическое описание электронных ресурсов. Общие требования и правила составления.