- •Программируемые логические матрицы Программируемая матричная логика Базовые матричные кристаллы

- •Программируемые логические матрицы

- •Схемотехника ПЛМ

- •Программируемые логические матрицы

- •Программируемая матричная логика (ПМЛ)

- •Базовые матричные кристаллы

- •Классификация БМК

- •Структуры БМК

- •Структуры БМК

- •Вариант базовой ячейки БМК на КМДП-транзисторах

- •БМК с расширенными функциями

- •Параметры БМК

- •Области применения СБИС программируемой логики

- •Виды программирования СБИС ПЛ

- •Виды программирования СБИС ПЛ

- •Программируемые вентильные матрицы (FPGA)

- •Воспроизведение функции логическим блоком

- •Системы межсоединений FPGA

- •Система межсоединений FPGA

- •Система межсоединений FPGA

- •СБИС типа «Система на кристалле»

- •Структура СБИС «Система на кристалле»

Виды программирования СБИС ПЛ

•Перемычки типа antifuse

•ЛИПЗ МОП – транзисторы с двойным затвором

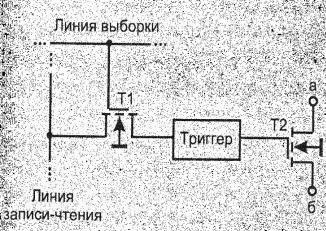

•Ключевые транзисторы, управляемые триггерами памяти конфигурации

1) Программирование с помощью перемычек antifuse является однократным. Перемычка образована трехслойным диэлектриком с чередованием слоев «оксид-нитрид-оксид». Программирующий импульс тока пробивает перемычку и создает проводящий канал из поликремния между электродами (один электрод поликемниевый, другой – диффузионная область n+).

Диэлектрик ONO – Oxid-Nitrid-Oxid

МИЭМ НИУ ВШЭ. Сафонов С.Н.

Виды программирования СБИС ПЛ

2) Программирование ЛИПЗ МОП–транзисторами используются в СБИС ПЛ так же как в ЗУ EPROM (с УФ стиранием). Стирание старой конфигурации осуществляется УФ-излучением в течение десятков минут при извлечении СБИС из системы.

Использование в СБИС ПЛ запоминающих элементов EEPROM не требует извлечения СБИС из системы и занимает единицы миллисекунд.

3) Программирование ключевыми транзисторами, управляемыми триггерами памяти конфигурации. Ключевой транзистор Т2 замыкает или размыкает участок aб базовой ячейки в зависимости от состояния триггера. При программировании на линию выборки подается высокий потенциал и транзистор Т1 включается. С линии записи-чтения подается сигнал установки триггера в «0» или «1». В рабочем режиме транзистор Т1 заперт, триггер сохраняет состояние.

При выключении питания информация теряется, поэтому при включении питания требуется процесс программирования (аналогичен загрузке системы).

МИЭМ НИУ ВШЭ. Сафонов С.Н.

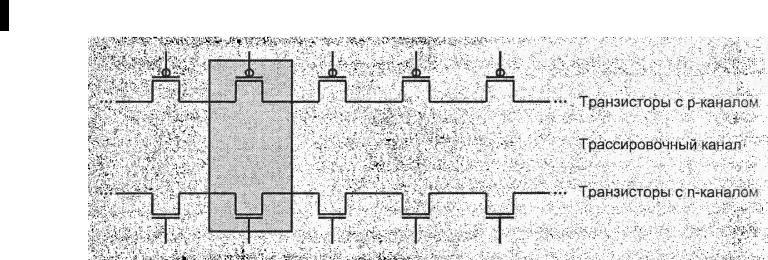

Программируемые вентильные матрицы (FPGA)

FPGA топологически сходны с БМК. Во внутренней области размещены регулярно расположенные идентичные конфигурируемые логические блоки (КЛБ), между которыми проходят трассировочные каналы, на периферии кристалла расположены блоки ввода/вывода.

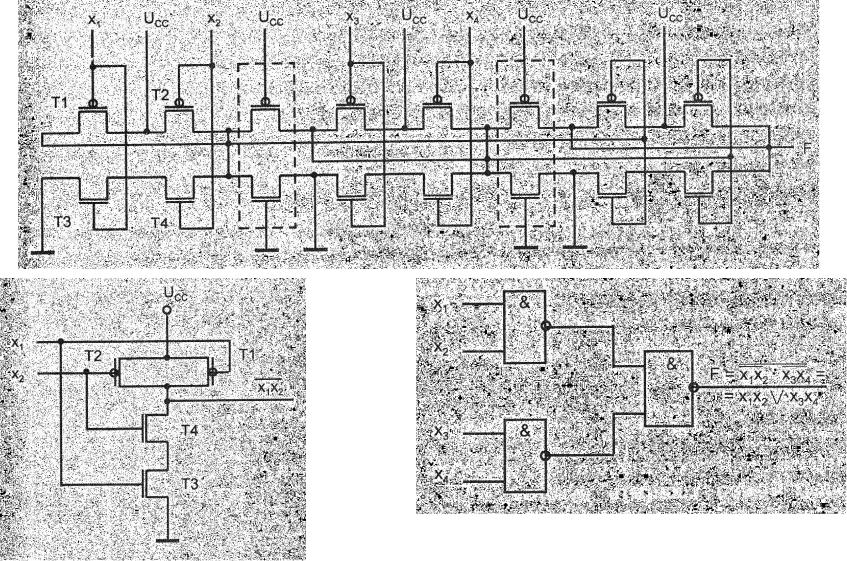

В качестве КЛБ используются:

•Транзисторные пары, вентили И-НЕ, ИЛИ-НЕ

•Логические модули на основе мультиплексоров

•Логические модули на основе программируемых ПЗУ

Схема логического блока

Соединение транзисторов логического блока в проектируемую схему осуществляется с помощью программируемых перемычек, как показано на следующем слайде.

МИЭМ НИУ ВШЭ. Сафонов С.Н.

Воспроизведение функции логическим блоком

МИЭМ НИУ ВШЭ. Сафонов С.Н.