2416

.pdf

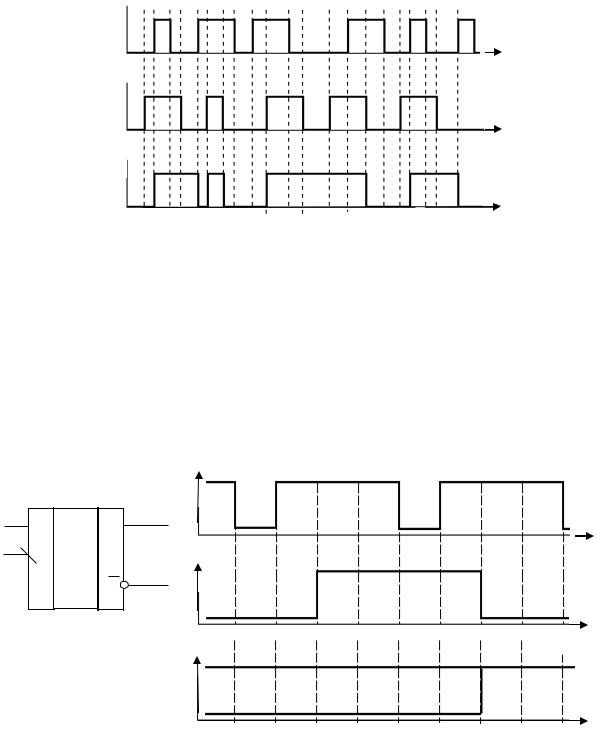

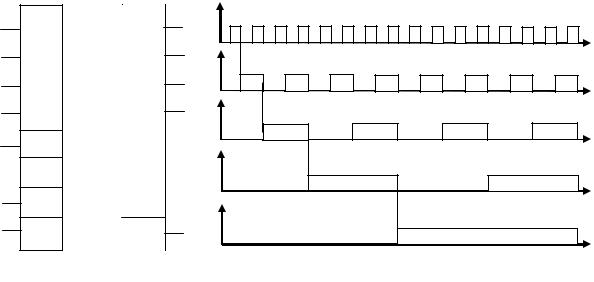

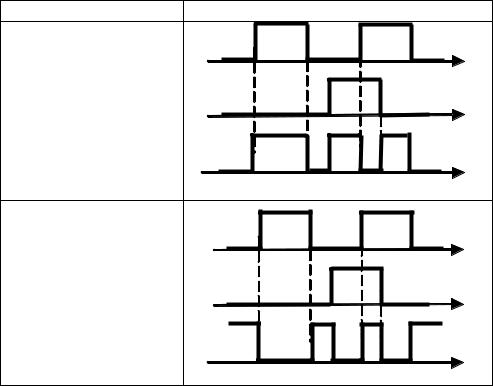

У D-триггеров с потенциальным управлением информация со входа D переписывается на выход Q в течение времени, при котором синхросигнал активен С=1. При пассивном синхросигнале триггер не чувствителен к изменениям информационного сигнала.

C

t

D

t

Q

t

Рис. 10.59. Временная диаграмма D-триггера со статическим управлением

Схемное обозначение и таблица истинности, поясняющая алгоритм функционирования D-триггера, приведены в табл. 10.4.

Временная диаграмма D-триггера со статическим управлением приведена на рис. 10.59.

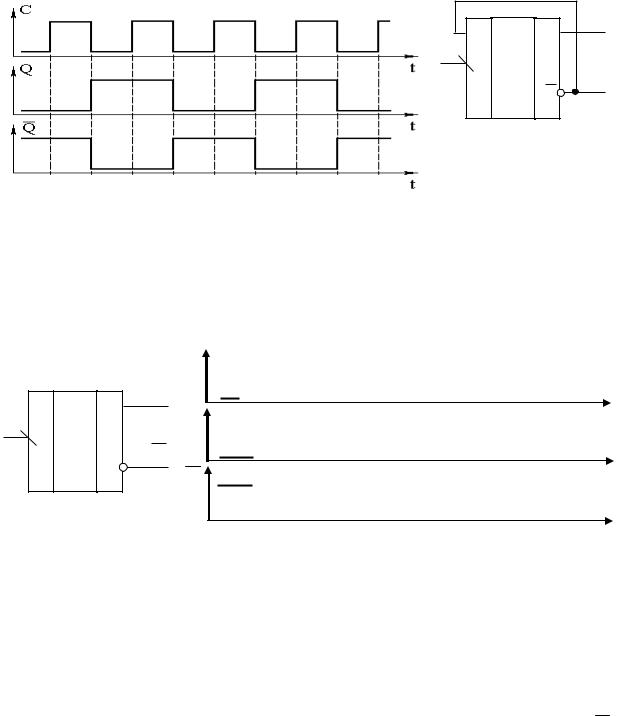

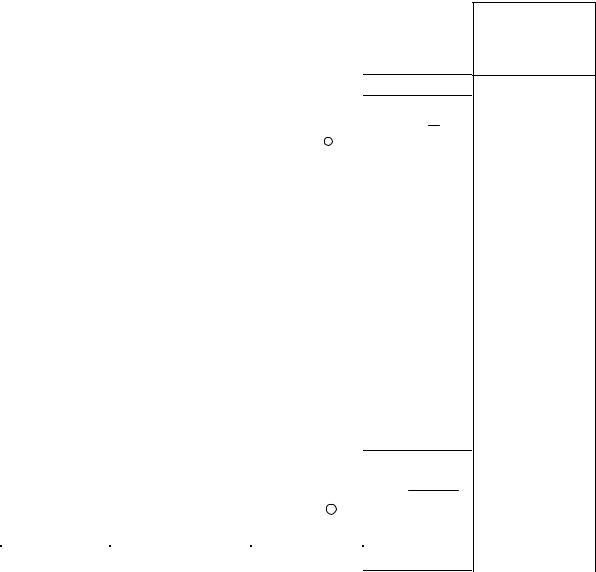

В триггерах с динамическим управлением информация записывается (передается на выход Q) по фронту или спаду сигнала синхронизации на входе С.

|

|

|

D |

D |

ТТ |

Q |

t |

C |

|

|

C |

|

|

Q |

|

|

|

|

|

|

|

|

t |

Q

t

Рис. 10.60. Схемное обозначение и временная диаграмма D-триггера с динамическим управлением по спаду сигнала синхронизации

280

Временная диаграмма D-триггера с динамическим управлением |

|||

по спаду сигнала синхронизации приведена на рис. 10.60. |

|

||

Т-триггер |

|

|

|

Т-триггер – это устройство с двумя ус- |

|

|

|

тойчивыми состояниями и одним счетным |

D ТТ |

Q |

|

(информационным) входом Т. Счётным он на- |

|||

C |

|

||

зывается потому, что он подсчитывает коли- |

|

||

чество импульсов, поступивших на его вход. |

|

Q |

|

Триггер переключается каждый раз в |

|

|

|

противоположное состояние по фронту или |

Рис. 10.61. Т-триггер |

||

по спаду управляющего сигнала на входе Т. |

на базе D-триггера |

||

Т-триггер может быть выполнен на основе D- |

|

|

|

триггера с динамическим управлением путем соединения инверсного |

|||

выхода со входом D (рис. 10.61). Счетный триггер из D-триггера с по- |

|||

тенциальным управлением получить нельзя. |

|

|

|

Т-триггеры используются при построении схем различных счёт- |

|||

чиков, поэтому в составе больших интегральных схем различного на- |

|||

значения обычно есть готовые модули этих триггеров. |

|

||

|

T |

|

Q |

t |

|

ТТ |

Q |

|

Т |

||

t |

||

Q |

||

|

||

|

Q |

|

|

t |

Рис. 10.62. Схемное обозначение Т-триггера, работающего по спаду синхронизирующего сигнала, и его временная диаграмма

Схемное обозначение Т-триггера, работающего по спаду синхронизирующего сигнала, и его временная диаграмма приведены на рис. 10.62.

JK-триггер

JK-триггер имеет два выхода: прямой Q и инверсный Q .

JK-триггер имеет пять входов: R – асинхронный вход установки в состояние «0» (Q=0); S – асинхронный вход установки в состояние «1»

281

(Q=1); К – синхронизируемый вход установки в состояние «0» (Q=0); J – синхронизируемый вход установки в состояние «1» (Q=1); С – синхронизирующий вход.

Асинхронные входы R и S работают так же, как в RS-триггере, независимо от сигналов на остальных входах: режим «S=1, R=0» – режим записи «1»; режим «S=0 и R=1» – режим записи «0»; режим «S=R=0» – режим хранения информации. Не допускается одновременно наличие на входах R и S активных сигналов «S=R=1».

При S=R=0 логика работы входов J, K и C такова: если на входе J логическая 1, а на входе K – логический 0, то по спаду синхроимпульса на входе C триггер установится в состояние «1». Если на входе J – логический 0, а на входе K – логическая 1, то по спаду синхроимпульса на входе C триггер установится в состояние «0». В случае, когда и на входах J и K логические нули, то независимо от сигнала на входе C состояние триггера не меняется. И последний режим работы, когда на входах J и K логические единицы, JK-триггер работает в режиме делителя частоты сигнала на входе С. Это означает, что по заднему фронту каждого тактового импульса состояние триггера меняется на противоположное.

Таблица 10.5

Схемное обозначение и таблица истинности JK-триггера

|

|

|

Схемное |

|

|

|

|

|

|

Входы |

|

Состояние |

Примечание |

||||||

|

|

|

обозначение |

|

|

|

|

|

|

|

|

|

|

выходов |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

С |

K |

|

J |

Q(t) |

Q(t+1) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

* |

|

* |

0 |

0 |

Режим хранения информации |

|

|

|

S |

|

TT |

|

Q |

0 |

|

* |

|

* |

1 |

1 |

|||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

0 |

0 |

0 |

Режим хранения информации |

|

|

|

J |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

1 |

|

0 |

|

0 |

1 |

1 |

||||||

|

|

|

K |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

Режим установки единицы J=1 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

Q |

1 |

|

0 |

|

1 |

1 |

1 |

||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

R |

|

|

|

|

|

|

|

|

1 |

|

1 |

|

0 |

0 |

0 |

Режим записи нуля K=1 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

1 |

|

1 |

|

0 |

1 |

0 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

1 |

0 |

1 |

Счетный режим триггера J=K=1 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Примечания: 1. * – любое состояние входа.

2. Таблица справедлива при R=S=0.

282

Схемное обозначение и таблица истинности JK-триггера приведены в табл. 10.5.

Из таблицы видно, что при J=1 и K=0 триггер по тактовому импульсу устанавливается в состояние 1 (Q=1); при J=0 и К=1 триггер по тактовому импульсу устанавливается в состояние «0» (Q=0); при J=K=0 триггер хранит ранее принятую информацию независимо от сигнала на синхронизирующем входе С; при J=K=1 состояние выхода Q триггера с каждым импульсом на синхронизирующем входе С изменяется на противоположное. Триггер становится делителем частоты на 2.

C |

t |

|

J

t

K

t

Q |

t |

|

Q

t

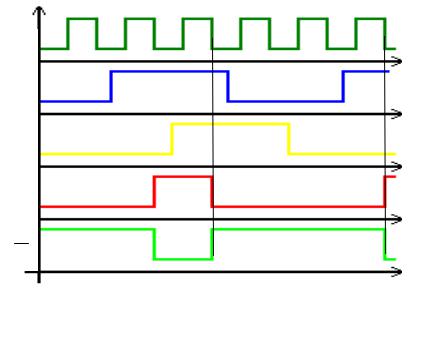

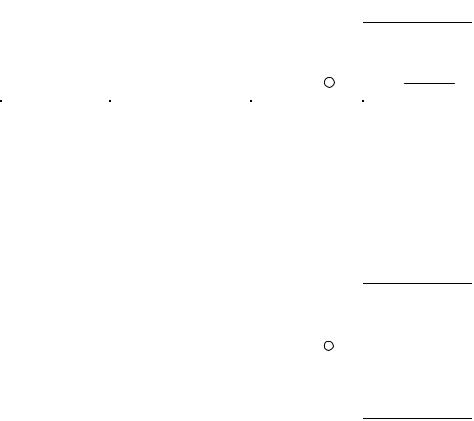

Рис. 10.63. Временная диаграмма JK-триггера при R=S=0

На рис. 10.63 приведена временная диаграмма JK-триггера, иллюстрирующая переключение триггера по спаду синхронизирующего сигнала в зависимости от состояния входов J и K.

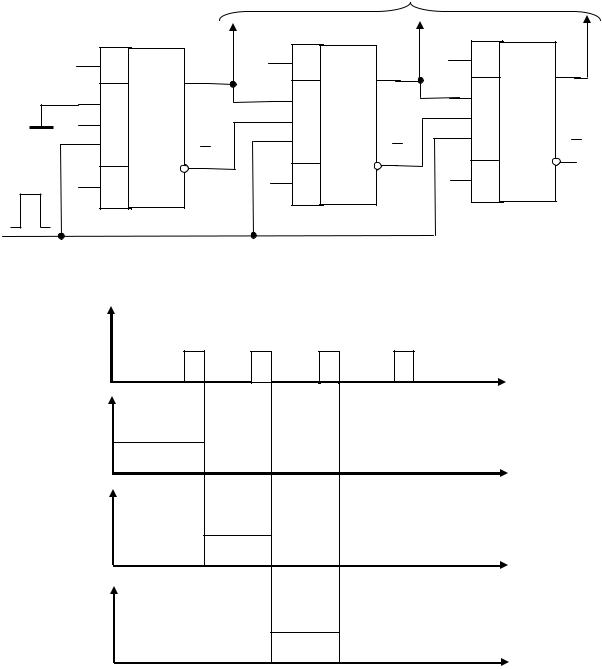

10.19.4. Регистры

Регистрами называются устройства для приема, хранения, передачи и преобразования информации, представленной обычно в двоичной системе счисления. На рис. 10.64 приведена схема трехразрядного регистра сдвига на JK-триггерах. Предварительно подачей сигналов на установочные входы R и S все триггеры установлены в нулевое состояние (Q1=Q2=Q3=0).

283

|

|

Выход |

|

|

S TT1 |

S |

TT2 Q |

S TT3 Q3 |

|

|

Q1 |

2 |

|

|

J |

J |

|

J |

|

+ K |

K |

|

K |

|

C |

C |

Q2 |

C |

Q3 |

Q1 |

R |

|||

R |

R |

|

|

|

Рис. 10.64. Регистр сдвига на JK-триггерах

C

Q1 t

t

Q2

t

Q3

Рис. 10.65. Временная диаграмма регистра сдвига t

Установим триггер ТТ1 в состояние Q1=1. При этом состояние регистра определится совокупностью значений Q1Q2Q3=100. Под действием первого импульса синхронизации С состояние триггера изменится на Q1Q2Q3=010 (рис. 10.65), под действием второго импульса синхронизации – на Q1Q2Q3=001 и т.д. Таким образом, под действием каждого импульса синхронизации происходит сдвиг двоичного числа на один разряд.

284

|

|

|

|

|

|

|

|

|

|

4 |

Окончание табл. 10.6 |

|||||||

1 |

2 |

|

|

|

3 |

|

|

|

|

|

5 |

|

||||||

|

Отрицание |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X1 |

X2 |

Y |

|

|

|

X1 |

& |

Y |

|

|

|

|

|

|

0 |

0 |

1 |

||||

|

логического |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

И-НЕ |

|

|

X2 |

|

|

|

|

|

|

|

|

0 |

1 |

1 |

||||

умножения, |

|

|

|

|

|

|

|

Y = X1 X 2 |

||||||||||

|

штрих |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Шеффера |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Исклю- |

Сложение по |

|

|

X1 |

|

|

|

|

|

|

|

|

|

|

|

X1 |

X2 |

Y |

|

|

=1 |

Y |

|

|

|

|

|

|

0 |

0 |

0 |

||||||

чающее |

модулю 2, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

X2 |

|

|

Y = X1 |

X 2 |

0 |

1 |

1 |

|||||||||

ИЛИ |

неравнознач- |

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

1 |

0 |

1 |

||||||||||

|

|

|

|

|

|

|

|

|||||||||||

|

ность |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Исклю- |

Эквивалент- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X1 |

X2 |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

X1 |

|

=1 |

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

||

чающее |

ность, |

|

|

|

Y |

Y = X1 |

Х2 |

|||||||||||

|

|

|

|

|

|

|

|

|||||||||||

|

|

X2 |

|

|

0 |

1 |

0 |

|||||||||||

ИЛИ-НЕ |

равнозначность |

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

||||||

|

|

|

|

|

|

|

|

|

|

X |

Х |

|||||||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

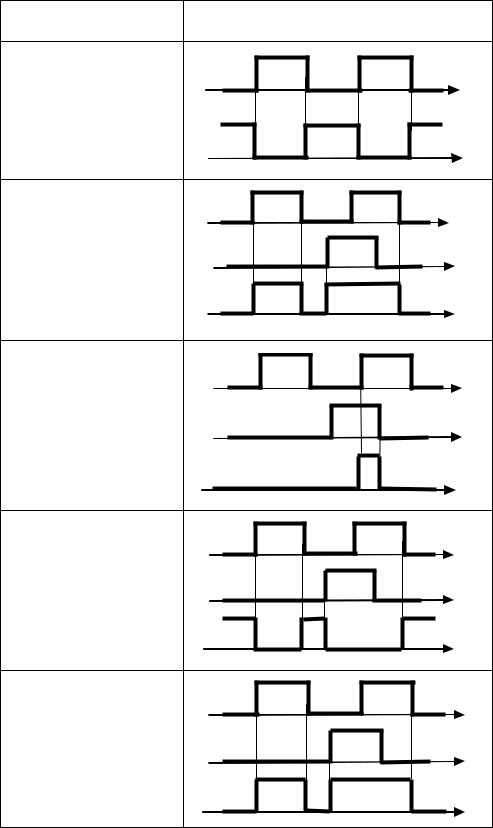

Логические элементы выполняют, как правило, в виде интегральных микросхем, каждый корпус которых может содержать несколько логических элементов. Логические элементы могут работать в режимах положительной и отрицательной логики. В режиме положительной логики логической единице соответствует высокий уровень напряжения, а логическому нулю – низкий уровень напряжения. В режиме отрицательной логики логической единице соответствует низкий уровень напряжения, а логическому нулю – высокий. Временные диаграммы логических элементов приведены в табл. 10.7.

Для контактно-релейных схем в режиме положительной логики логической единице соответствует замкнутый контакт ключа или реле, а логическому нулю – разомкнутый. Светящийся индикатор (лампочка, светодиод) соответствует логической единице, а несветящийся

– логическому нулю.

Как правило, паспортное обозначение логического элемента соответствует функции, реализуемой положительной логикой. Логическая функция может быть задана таблицей, которая называется таблицей истинности. Число строк в таблице – это число возможных наборов значений аргументов. Оно равно 2n, где n – число переменных.

287

Таблица 10.7

Временные диаграммы логических элементов

Логический элемент |

Временная диаграмма |

1 |

2 |

X |

t |

НЕ |

Y |

t |

|

X1 |

t |

X2 |

t |

ИЛИ |

|

Y |

t |

X1 |

t |

И |

X2 |

t |

|

|

|

|

Y |

t |

X1 |

t |

ИЛИ-НЕ |

X2 |

t |

|

Y |

t |

X1 |

t |

X2 |

t |

И-НЕ |

|

Y |

t |

288

|

|

Окончание табл. 10.7 |

1 |

|

2 |

|

X1 |

t |

Исключающее |

X2 |

t |

ИЛИ |

|

|

|

Y |

t |

X1 |

t |

Исключающее |

X2 |

t |

ИЛИ-НЕ |

Y |

t |

Логические элементы представляют собой комбинационные схемы. В комбинационных схемах состояние на выходе в данный момент времени однозначно определяется состояниями на входах в тот же момент времени.

На базе логических элементов построены такие устройства, как шифраторы, дешифраторы, мультиплексоры, демультиплексоры, сумматоры.

Шифратор (кодер) преобразует сигнал на одном из его входов в n-разрядное двоичное число. При появлении сигнала логической единицы на одном из десяти входов на четырех выходах шифратора будет присутствовать соответствующее двоичное число.

Дешифратор (декодер) преобразует код, поступающий на его n- входов, в сигнал логической единицы только на одном из его выходов. Дешифратор n-разрядного двоичного числа имеет 2n выходов.

Различные типы дешифраторов применяются в схемах цифровой индикации информации. Особенно широко применяются дешифраторы, преобразующие информацию в код для семисегментных индикаторов.

Условные обозначения и таблицы истинности шифратора и дешифратора приведены соответственно в табл. 10.8 и 10.9.

289

C

C