Практическое занятие №4 БАЗОВЫЕ ЭЛЕМЕНТЫ ТТЛ- И КМОП-ЛОГИКИ

Цели занятия: изучение особенностей элементной базы ТТЛлогики и КМОП-логики, анализ их возможностей, достоинств и недос-

татков. |

|

|

|

С |

|

|

|

Краткие теоретические сведения |

|

|

|

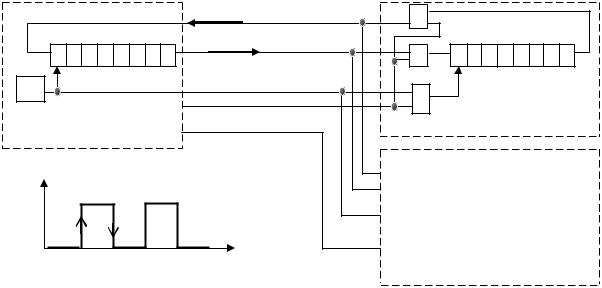

Для построен я базового элемента в ТТЛ-логике используются |

|||

биполярные транз сторы, а в КМОП-логике – полевые МОП- |

|||

времени |

р |

R |

|

транз сторы. Транз сторы здесь работают в ключевом режиме, то есть |

|||

большую часть |

находятся либо в состоянии отсечки (разомкну- |

||

тое состоян е контактов ключа), либо в состоянии насыщения (замкнутое состоян е). Чем короче переходный режим транзисторного ключа

(время на замыкан е размыкание), тем выше его быстродействие.

В замкнутомбАсостоянии потребляемая мощность ключа Pз I2R, где ток I в цепи транзистора имеет некоторое постоянное максимальное значение, а сопротивлениеДтранзистора R 0. Но тогда и Pз 0.

В разомкнутом состоянии потребляемая мощность ключа P U2 ,

где напряжен е U между контактами имеет некоторое постоянное максимальное значение, а сопротивление транзистора R . Но тогда

Следовательно, транзисторный ключ потребляет мощность в основном в переходных режимах, и чем выше его быстродействие, тем ниже будет его энергопотребление.

Интегральная схема, реализующая базовый элемент -НЕ ( ЛИНЕ), может быть собрана на транзисторныхИключах с высоким быстродействием. При подключении к ней нестандартной нагрузки может возникнуть несоответствие ее логических уровней с логическими уровнями подключаемой цифровой схемы. Низкий уровень сигнала в цифровых схемах воспринимается как логический нуль, а высокий – как логическая единица. Эти уровни в различных цифровых интегральных схемах могут быть разными, что препятствует их соединению в единое цифровое устройство.

Любая нагрузка, отличная от цифровых интегральных схем, для конкретной цифровой схемы является нестандартной нагрузкой. Так, нестандартной нагрузкой являются: светодиоды, элементы индикации, управляющие обмотки реле, схемы управления приводами. Для обеспечения возможности подключения такой нагрузки к цифровой инте-

22

гральной схеме необходимо, чтобы эта схема могла формировать тре- |

||||||||

буемые для этой нагрузки логические уровни. |

|

|

||||||

Базовый элемент ТТЛ-логики (И-НЕ) |

|

|

||||||

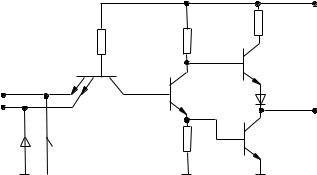

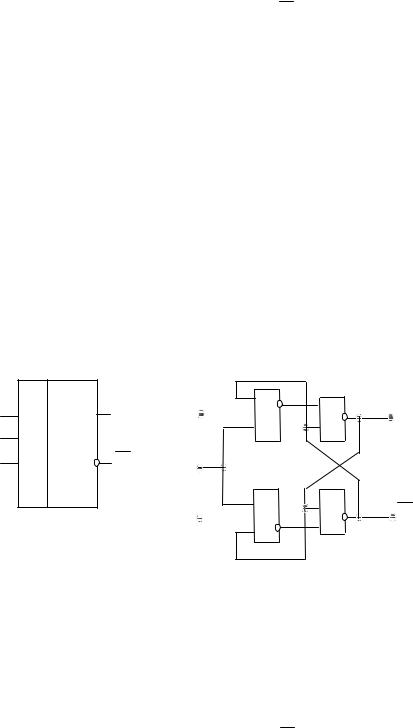

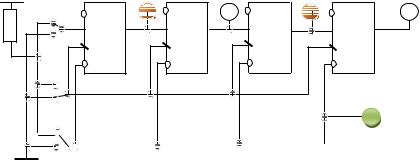

В стандартном логическом элементе ТТЛ (рис. 1.11) формируются |

||||||||

активные логические уровни. |

|

|

|

|

||||

С |

|

|

|

|

|

+5В |

||

|

|

R1 |

R2 |

|

R4 |

|||

|

|

VT3 |

||||||

|

|

VT1 |

|

|||||

Uвх1 |

|

VT2 |

|

VD3 |

||||

|

|

|

|

|||||

Uвх2 |

|

|

|

|

Uвых |

|||

VD1 |

VD2 |

R3 |

VT4 |

|||||

|

|

|||||||

|

|

|

|

|||||

|

|

|

|

|

||||

|

|

. 1.11. Базовый элемент ТТЛ (И-НЕ) |

||||||

Рис |

|

|

|

|

||||

Н зк й уровень соответствует насыщенному (открытому) транзи- |

||||||||

стору VT4, при этом транзистор VT3 находится в отсечке (закрыт), и |

||||||||

схема формирует выходное напряжение низкого уровня, соответствую- |

||||||||

щее напряжению насыщения транзистора VT4 |

|

|

||||||

|

|

Uвых |

U4н 0,2 В, |

|

(1.17) |

|||

где U4н напряжение на транзисторе VT4 в режиме насыщения, при- |

||||||||

мерно соответствует 0,2 В. |

|

|

|

|

||||

Высокий уровень на выходе схемы формируется при открытом |

||||||||

бА |

|

|

||||||

транзисторе VT3 и закрытом VT4, в данном случае выходное напряже- |

||||||||

ние соответствует |

|

|

|

|

|

|||

|

|

Uвых |

Eп IнR4 Ud3 U3н , |

|

(1.18) |

|||

где Eп – напряжение питания (+5 В); IН |

– ток нагрузки, зависящий от |

|||||||

суммарного |

входного |

сопротивленияДподключаемых элементов; |

||||||

Ud3 – напряжение на прямосмещенном диоде VD3 (можно считать, что |

||||||||

оно не зависит от тока и приблизительно составляет 0,7 В для кремние- |

||||||||

вых диодов); U3н – напряжение на транзисторе VT3 в режиме насыще- |

||||||||

ния, примерно соответствует 0,2 В. |

И |

|||||||

|

|

|

|

|

||||

Напряжение высокого уровня для элементов ТТЛ находится в |

||||||||

пределах 2,4…4 В и снижается по мере увеличения тока нагрузки. Здесь |

||||||||

диоды VD1 и VD2 ограничивают напряжение входа (Uвх1 и Uвх2) в отри- |

||||||||

цательных областях, а в положительных областях они заперты, и роли |

||||||||

не играют. |

|

|

|

|

|

|

|

|

Многоэмиттерный транзистор VT1 (в данном случае он имеет два |

||||||||

эмиттерных входа) переключится в инверсный режим, если на обоих его |

||||||||

входах будет высокий уровень напряжения (x1 x2 |

1). В этом режиме |

|||||||

|

|

|

|

23 |

|

|

|

|

он своим коллекторным током откроет транзисторный ключ VT2, через который потечет ток, часть которого потечет по базовой цепи транзистора VT4 и откроет его. Через замкнутый ключ VT4 произойдет быстрый разряд потенциала клеммы выхода (рассасывание заряда паразитной емкости). В это же время транзистор VT3 будет закрыт, так как при открытом ключе VT2 напряжение на базе VT3 упадет. В этом случае

Uвых 0,4В (y 0).

При подаче хотя бы на один из входов сигнала низкого уровня

(x1 0л бо x2 |

0) транзистор VT1 переключается в режим насыщения. |

|

Его коллекторный ток понижает напряжение на базе транзистора VT2 и |

||

закрывает его |

|

транзистор VT4, а открытый транзистор VT3 в этом |

случае будет работать в режиме эмиттерного повторителя, обеспечивая |

||

С |

|

|

передачу на выход напряжения высокого уровня Uвых 2,4В (y 1). Так м о разом, рассмотренная схема (рис. 1.11) реализует функ-

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(см. |

|

|

|

. 1.1) y15 x1 |

x2 x1x2 – штрих Шеффера или И-НЕ. |

||||||||||||||||||||||||||||||

цию |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

Интегральная схема с выходом типа «открытый коллектор» |

|||||||||||||||||||||||||||||||||||

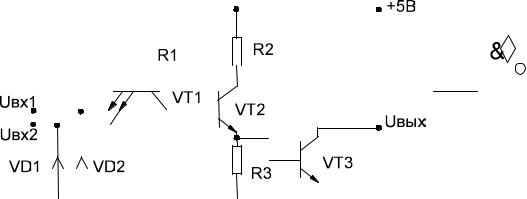

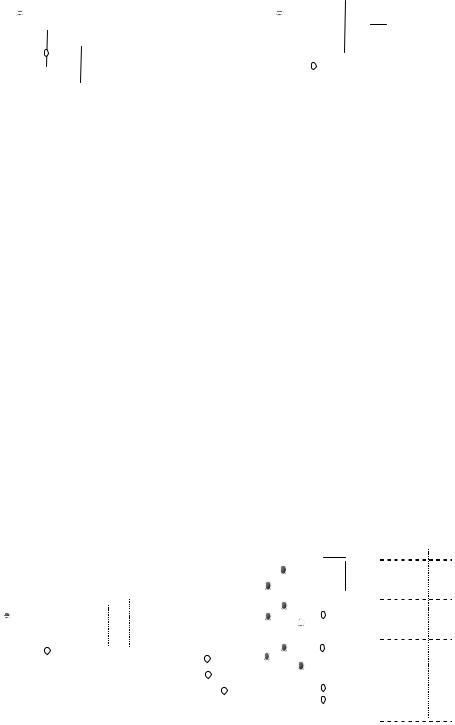

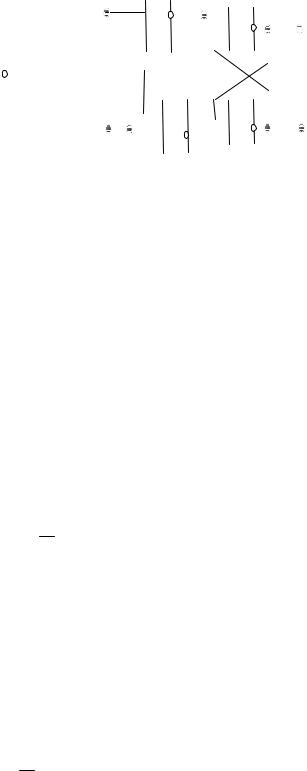

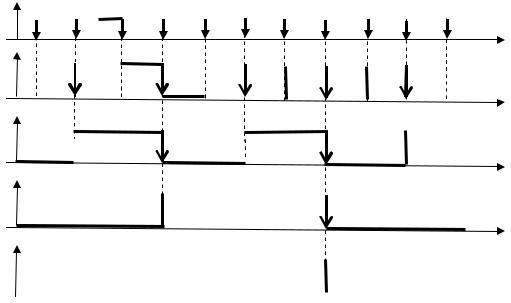

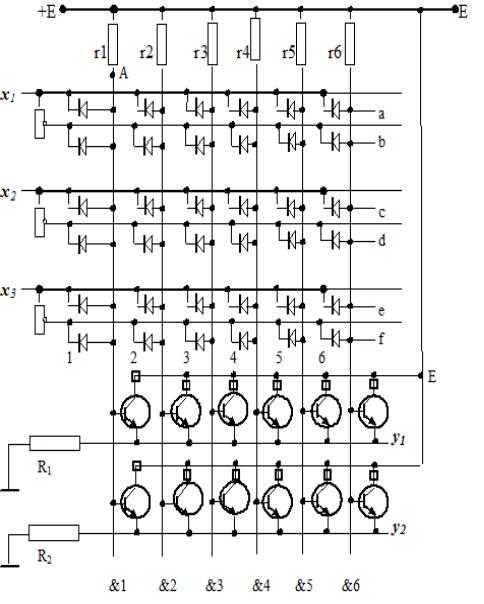

На р с. 1.12 приводится простейшая схема элементов типа «от- |

|||||||||||||||||||||||||||||||||||

крытый коллектор». |

|||||||||||||||||||||||||||||||||||

|

табл |

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

А |

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Д |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 1.12. Логический элемент типа «открытый коллектор» |

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

И |

|||||||||||

Как видно из схемы, здесь отсутствует верхний транзистор составного инвертора, подключенного к питанию (VT3 на рис. 1.11). Выходной вывод схемы идет непосредственно от неподключенного к другим элементам коллектора VT3 (здесь и далее имеется в виду рис. 1.12), то есть открытого коллектора, отсюда и название типа выхода. Выходной каскад схемы, состоящий из одного транзистора VT3, может находиться в двух состояниях: транзистор VT3 открыт (на выходе формируется низкий уровень, так же как при активном выходе); транзистор закрыт, выход находится в состоянии отключения (обрыва). Выходы типа «открытый коллектор» также называют пассивными, поскольку они не

24

формируют активного напряжения высокого уровня. Цифровые микросхемы, имеющие подобные выходы, помечаются специальным значком

– ромбом, подчеркнутым снизу (рис. 1.12).

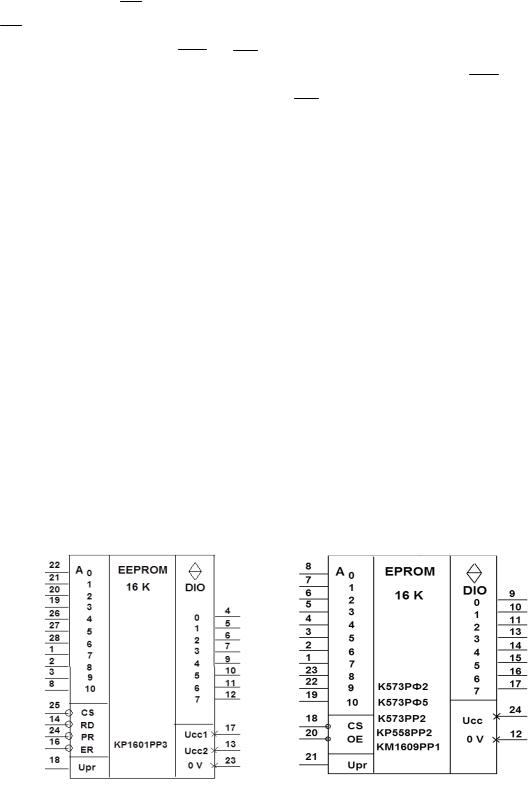

Выходы типа «открытый коллектор» могут иметь наряду с логическими элементами регистры, дешифраторы, ПЗУ. Основное назначение таких микросхем: реализация монтажных (проводных) функций и подключение нестандартной нагрузки. При желании использовать выход

типа «открытый коллектор» как активный следует подключить внешний |

||||||||||||

резистор между данным выходом и напряжением питания, обеспечив |

||||||||||||

форм рован е акт вного уровня (рис. 1.13). |

||||||||||||

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Р с. 1.13. Использование пассивного выхода как активного |

|||||||||||

иЗдесь нео ход мо учитывать, что такой элемент будет проигры- |

||||||||||||

вать обычному акт вному элементу в быстродействии, поскольку будет |

||||||||||||

иметь |

по сравнению с ним величину фронта перехода с низко- |

|||||||||||

го уровня к высокому (t01) из-за того, что суммарная емкость нагрузки |

||||||||||||

большую

будет заряжаться черезАдостаточно большое внешнее сопротивление R. Монтажные функции реализуются непосредственным соединени-

ем проводников, идущих от различных элементов. На рис. 1.14 приво-

дится схема, реализующая функциюД«монтажного И», выходы несколь-

ких элементов соединены в одной точке (точка A), данная точка подключается к плюсу источника питания через сопротивление R. Следует напомнить, что непосредственное соединение обычных (активных) вы-

ходов недопустимо.

И

И

Рис. 1.14. «Монтажное «И»

25

Наличие низкого уровня на выходе хотя бы одного элемента приводит к формированию низкого уровня на выходе всей схемы. Возвращаясь к рис. 1.12, можно увидеть, что при таком включении выходные транзисторы VT3 всех схем оказываются включенными параллельно

(между коллектором и эмиттером) и достаточно, чтобы открылся только один из них для формирования низкого уровня на выходе всей схемы.

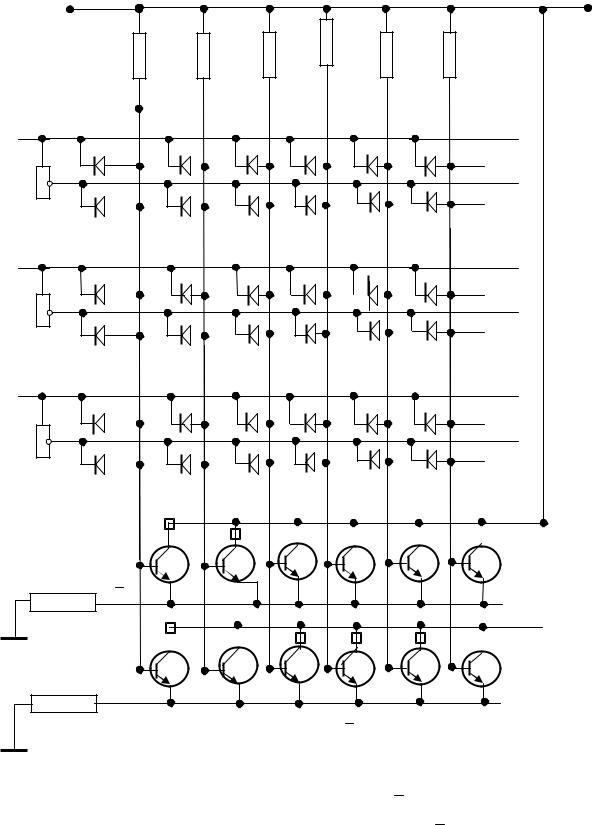

Сваться в качестве ключей следующих видов: МОП-ключ с активной (резисторной) нагрузкой; МОП-ключ с динамической (МОПтранз сторной) нагрузкой; КМОП-инвертор; БиКМОП-ключ.

Комплементарные металл-оксид полупроводники. КМОП-лог ка

Полевые транз сторы с изолированным затвором могут использо-

резисторнагрузкой. В схеме такого ключа в качестве динамической нагрузки ис-

Недостатком МОП-ключа с активной нагрузкой является то, что зан мает много места на кристалле и на нем рассеивается

большая мощность. Этого недостатка нет у МОП-ключа с динамической

пользуется МОП-транзистор с таким же типом канала, что и у МОП-ключа.

рабочем Общим недостаткомАо оих рассмотренных МОП-ключей является

то, что в состоянии через них протекает постоянная составляющая тока, пропорциональная сопротивлению нагрузки. Но при последовательном включении нескольких ключей этот ток для схемы ключа в целом не нужен, так как входной ток у МОП-транзисторов равен нулю, а для их переключения требуется лишь перезарядить входную емкость. Следовательно, здесь происходит бесполезное потребление

мощности. Этот недостаток устраняется в КМОП-инверторе. |

|

|||||||||||||||||||||||||

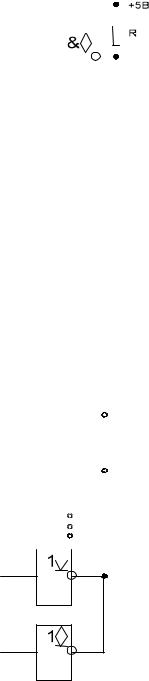

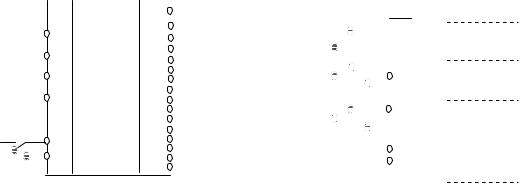

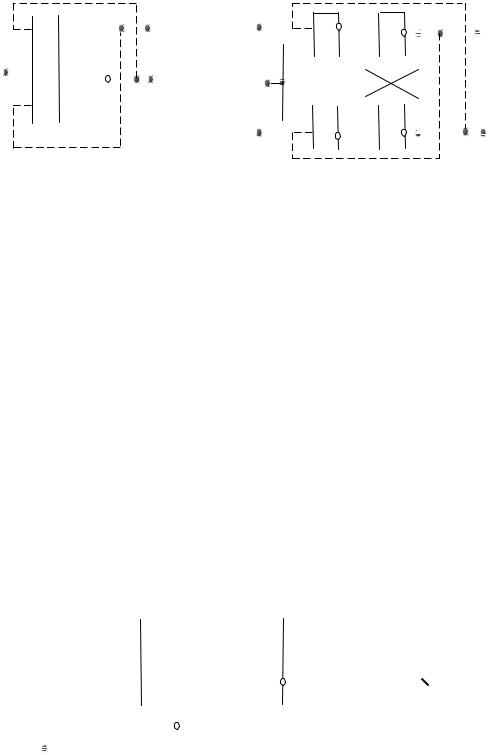

|

Схема |

КМОП-инвертора |

|

|

– |

это |

соединение |

двух |

||||||||||||||||||

МОП-транзисторов с каналами разной проводимости. Транзистор VT1 |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Д |

|

||||||||||

имеет n-канал, а VT2 – p-канал (см. рис. 1.15). |

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

Eп |

|

|

|

|

|

|

Eп |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VT1 |

|

|

|

VT2 |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

VT2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

И |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Eз |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y15 |

|

|

|

|

VT3 |

VT1 Uвых |

x1 |

Uвых |

|

VT4 |

|

|

x2 |

|

|

|

|

Рис. 1.15. КМОП-инвертор |

Рис. 1.16. Базовый элемент КМОП (И-НЕ) |

|

26

Эту пару транзисторов называют комплементарной (дополняющей). Отсюда и аббревиатура КМОП. Здесь стоки транзисторов VT1 и VT2 объединены в один вывод, который является выходом ключа. Затворы также объединены и образуют вход ключа. Исток транзистора VT2 соединен с шиной питания (+Eп), а исток транзистора VT1 заземлен. Выходное напряжение Uвых снимается с транзистора VT1.

Режим транзисторов подбирается таким образом, чтобы даже в переходных процессах не было моментов, когда оба транзистора открыты. Для этого напряжение питания инвертора выбирается из условия

значение |

Eп |

U01 |

|

U02 |

, |

(1.17) |

|

|

|

|

|

|

|

где U01,U02 пороговые напряжения транзисторов VT1 и VT2 соответ- |

||||||

Сственно. Обычное |

для порогового напряжения U0 0,2Еп . |

|||||

Если на затворе высокий уровень сигнала (Ез > 2,4 В), то транзистор VT1 открыт, а VT2 – закрыт, и напряжение Uвых будет иметь низкий уровень. При н зком уровне входного сигнала картина изменится на прот воположную, напряжение Uвых будет иметь высокий уровень. Следовательно, данная схема реализует логическую функцию инверсии

транзисторыбАVT1 и VT2 закрыты, а n-канальные VT3 и VT4 открыты. Тогда на выходе этой схемы удет низкий уровень напряжения, то есть y 0. При x1 x2 0 все эти транзисторы поменяют свои состояния на противоположные, при которых y 1.

На рис. 1.16 приведена интегральная схема, собранная на

КМОП-инверторе. Нетрудно видеть, что при x1 x2 1 p-канальные

Д ключи VT1 и VT2 соединены параллельноИ. Транзистор VT3 при этом

При x1 1и x2 0 транзистор VT1 открыт, поэтому участок цепи Eп VT1 y замкнут, несмотря на разомкнутый ключ VT2, так как

будет закрыт, а ключ VT4 открыт, но, так как ключи VT3 и VT4 соеди-

нены последовательно, то цепь заземления выхода схемы все равно будет разорвана. Поэтому y 1.

При x1 0и x2 1 лишь поменяются своими состояниями ключи VT1 и VT2, а также VT3 и VT4, но результат тот же – y 1. Таким образом, согласно вычисленной выше таблицы истинности, данная логическая функция (см. табл. 1.1) y15 x1 x2 x1x2 – штрих Шеффера или И-НЕ.

У биполярных транзисторов способность отдавать ток в нагрузку значительно выше, чем у МОП-транзистора. Желание избавиться от этого недостатка КМОП-логики привело к появлению БиКМОП-логики. На рис. 1.17 представлена простейшая схема БиКМОП-инвертора.

27

+Eп |

|

|

|

|

а |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

x Ез |

VT2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

VT3 |

y |

б |

|||

|

|

|

|

|||||||||

|

|

|

|

|||||||||

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

VT1 |

|

|

|

|

|

|

|

VT4 |

Uвых |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

||||||||

Р с. 1.17. Б КМОП-инвертор |

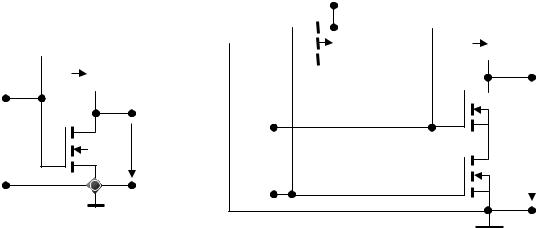

Рис. 1.18. Микросхемы И-НЕ |

|||||||||||

С |

МОП-транзистор VT1 закрыт, поэтому в базовой |

|||||||||||

Здесь при |

x 0 |

|||||||||||

цепи б полярного транзистора VT4 тока нет и он закрыт, а транзисторы |

||||||||||||

VT2 VT3 открыты. Поэтому y 1, а ток в цепи нагрузки такого инвер- |

||||||||||||

лениятора будет в β раз с льнее тока в цепи нагрузки КМОП-инвертора, где β

логическойбединицы у них меньше, а уровень логического нуля больше. Поэтому БиКМОП-логика не нашла такого широкого применения, как

– коэфф ц ент ус по току биполярного транзистора VT3. Однако Б КМОП-инверторы имеют меньшее быстродействие и их

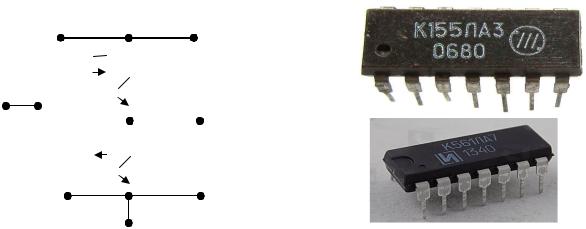

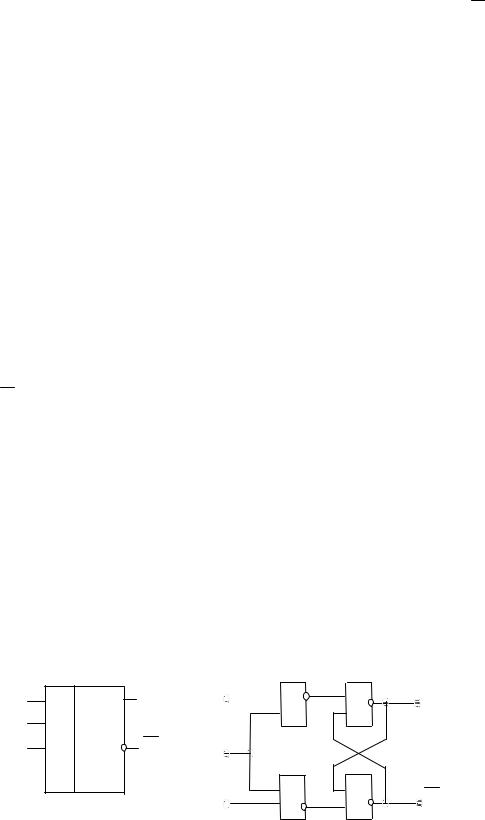

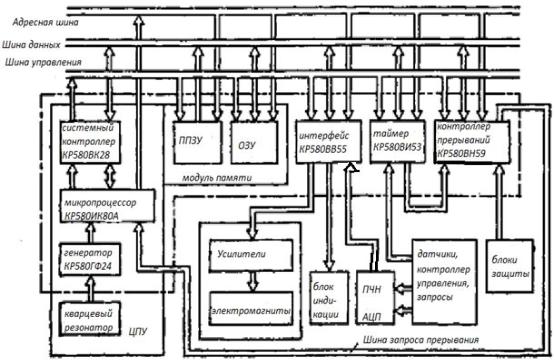

ТТЛ-логика и КМОПЛА-логика. Электронная отечественная промышленность выпускает стандартные микросхемы по четыре логических элемента И-НЕ в каждой. В микросхеме К155 3 (рис. 1.18,а) И-НЕ элементы собраны по интегральной схеме ТТЛ-логики (рис. 1.11), а в микросхеме К561ЛА7 (рис. 1.18,б) И-НЕ элементы собраны по схеме КМОП-логики (рис. 1.16).

помехозащищённость хуже, чем у КМОП-инвертора, так как уровень

|

Контрольные вопросы и задания |

|

1. |

Д |

|

Как потребляемая мощность транзисторного ключа связана с его |

||

|

быстродействием? |

|

2. |

Какая нагрузка для цифровой интегральной схемы является не- |

|

|

стандартной? |

|

3. |

Какие транзисторные ключи используются в транзисторно- |

|

|

транзисторной логике (ТТЛ)? |

И |

|

|

|

4. |

Что представляет собой выход «открытый коллектор»? |

|

5. |

Для каких целей используются интегральные схемы с выходом |

|

|

типа «открытый коллектор»? |

|

6. |

Начертите схему логического элемента И-НЕ в ТТЛ-логике и |

|

|

объясните, как эта схема работает. |

|

7. |

Назовите стандартную отечественную микросхему, реализую- |

|

|

щую базовый элемент И-НЕ в ТТЛ-логике. |

|

|

28 |

|

8.Перечислите виды ключей на МОП-транзисторах. Отметьте их достоинства и недостатки.

9.Какие два МОП-транзистора образуют комплементарную пару? 10.Начертите схему КМОП-инвертора и объясните, как эта схема

|

работает. |

11. |

Чему равен входной ток в МОП-транзисторе? |

С |

|

12. |

Начертите схему логического элемента И-НЕ в КМОП-логике |

|

и объясните, как эта схема работает. |

13. |

Назов те стандартную отечественную микросхему, реализую- |

щую базовый элемент И-НЕ в КМОП-логике. ки14.Нап ш те условие, при котором в схеме элемента И-НЕ в

КМОП-лог ке (рис. 1.16) транзиторные ключи VT1 и VT2 одновременно не могут ыть открытыми.

15.В чем пр нц пиальная разница в свойствах БикМОП-логики и КМОПб-лог ?

16.Начерт те схему БикМОП-инвертора и объясните, как эта схема ра отает.

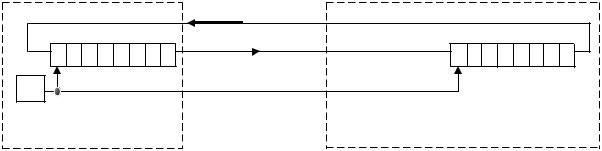

АПрактическое занятие №5

ШИФРАТОРЫ, ДЕШИФР ТОРЫ, МУЛЬТИПЛЕКСОРЫ, ДЕМУЛЬТИПЛЕКСОРЫ

памяти, применяемых в микропроцессорных системах в качестве коммутационных устройств; усвоение методики их построения из базовых логических элементов.

Цели занятия: закреплениеДзнаний о логических автоматах без

Краткие теоретические сведения |

И |

|

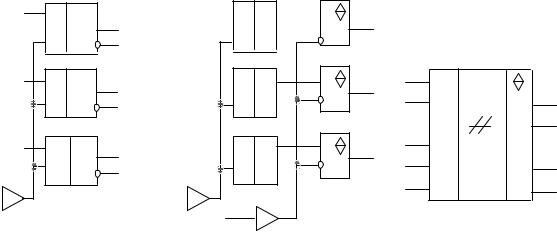

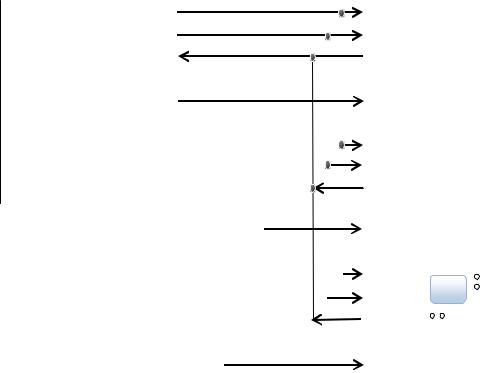

Шифратором называется КЛУ (логический автомат без памяти) с n

выходами и 2n входами. В частности, при n = 3 шифратор на схеме может быть представлен таким обозначением (рис. 1.19).

Шифратор номер входа, на который подается сигнал, преобразует в двоичный код. Например, сигнал, поступивший на вход d6, даст на выходе код 110 (q2 = 1, q1 = 1, q0 = 0), что соответствует числу 6 в двоичной системе счисления. Аналогично при d3 = 1 на выходе будет про-

читано q2 = 0, q1 = 1, q0= 1, а при d0 = 1 получим q2 = 0, q1 = 0, q0= 0.

Дешифратор – это КЛУ с n входами и 2n выходами. Он осуществляет действие, обратное шифратору – выставляет логическую единицу на тот вывод, номер которого в виде двоичного кода поступил на его вход. При n = 2 (рис. 1.20) дешифратор, имеющий на входе d1 = 1 и d0 = 1, выдаст на выходе q3 = 1, q2 = 0, q1 = 0, q0= 0, то есть только выход q3

29

будет иметь логическую единицу, так как двоичный код 11 соответствует числу 3.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

б |

||||

|

|

d7 |

CD |

|

|

|

|

|

d1 |

DC |

|

|

|

|

|

d3 |

|

MX |

|

|

|

|

|

|

DMX |

q7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

d6 |

|

|

|

|

|

|

d0 |

|

q3 |

|

|

|

|

d2 |

|

|

q |

|

|

|

|

d |

|

q6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

d5 |

|

|

|

|

|

|

|

|

q2 |

|

|

|

|

d1 |

|

|

|

|

|

|

|

|

|

q5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

d4 |

|

|

|

|

|

|

|

|

q1 |

|

|

|

|

d0 |

|

|

|

|

|

|

|

|

|

q4` |

|

|

|

|

d3 |

|

q2 |

|

|

|

|

|

|

q0 |

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

q3 |

|

|

|

|

d2 |

|

q1 |

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

a2 |

|

q2 |

|

|

|

|

d1 |

|

q0 |

|

|

Р с. 1.20. Дешифратор |

|

|

|

|

|

|

|

|

a1 |

|

q1 |

|

|

||||||||

|

|

d0 |

|

|

|

|

|

|

|

(n = 2) |

|

|

|

S |

|

|

|

|

|

|

|

a0 |

|

q0 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Рис |

Рис. 1.21. КЛУ: |

а – мультиплексор (n = 2); |

||||||||||||||||||||||||||

|

|

. 1.19. Ш фратор |

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

(n = 3) |

|

|

|

|

|

|

|

|

|

|

|

|

б – демультиплексор (n = 3) |

||||||||||||

Ш фратор номер входа, на который подается сигнал, преобразует в дво чный код. Например, сигнал, поступивший на вход d6, даст на выходе код 110 (q2 = 1, q1 = 1, q0 = 0), что соответствует числу 6 в дво-

ичной с стеме сч сления. налогично при d3 = 1 на выходе будет про-

читано q2 = 0, q1 = 1, q0= 1, а при d0 = 1 получим q2 = 0, q1 = 0, q0= 0.

будет иметьбАлогическую единицу, так как двоичный код 11 соответствует числу 3.

Дешифратор – это КЛУ с n входами и 2n выходами. Он осуществ-

ляет действие, о ратное шифратору – выставляет логическую единицу

на тот вывод, номер которого в виде двоичного кода поступил на его

вход. При n = 2 (рис. 1.20) дешифратор, имеющий на входе d1 = 1 и d0 = 1, выдаст на выходе q3 = 1, q2 =Д0, q1 = 0, q0= 0, то есть только выход q3

Мультиплексор – это КЛУ, предназначенное для поочередной пе-

редачи на один выход одного из 2n входных сигналов, где n – число адресных входов. Такую передачу называют мультиплексированиемИ.

Число информационных (мультиплексированных) входов называ-

ется количеством каналов мультиплексора, а количество адресных входов – числом его разрядов. Такое КЛУ коммутирует один из информационных входов с единственным выходом, а номер коммутируемого входа определяется адресными входами.

Число разрядов мультиплексоров, входящих в стандартные серии, от 1 до 4. На рис. 1.21,а представлено обозначение двухразрядного мультиплексора. При поступлении на его адресные входы, например, кода 11 (a1 = 1, a0 = 1) с выходом коммутируется информационный вход d3, а при коде 10 – вход d2 и т.д.

Демультиплексор – это КЛУ с одним информационным входом, n адресными входами и 2n выходами (рис. 21,б). Единственный информационный вход d здесь коммутируется с одним из выходов, номер кото-

30

рого соответствует двоичному коду, набранному на адресных входах. Например, при коде 101 на адресных входах (a2 = 1, a1 = 1, a0 = 1) вход d коммутируется с выходом q5, при коде 011 – с выходом q3 и т.д.

Примеры на построение схем шифраторов |

|

Шифратор с одним выходом (n = 1) – это простой провод, соеди- |

|

С |

с единственным в данном случае выходом q0, а вход d0 |

няющий вход d1 |

|

соединения с q0 |

не имеет. Поэтому, когда поступает сигнал на вход d0, |

q0 = 0, а при поступлении сигнала на вход d1 – q0 = 1. Однако здесь есть одно осложнен е. При отсутствии какого-либо сигнала q0 также равно

при |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

нулю, как |

|

с гнале d0. Эти разные ситуации следует различать. По- |

|||||||||||||||||||||||

этому схема такого ш фратора станет немного сложнее (рис. 1.22,а). |

|||||||||||||||||||||||||

d1 |

n = 1 q0 |

d3 |

|

|

|

n = 2 |

q1 |

|

|

|

|

|

n = 3 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

d7 |

|

К555ИВ1 |

P |

|

|

||||||||||

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

d2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

1 |

|

|

d1 |

|

|

|

|

|

1 |

|

q0 |

|

|

|

|

|

|

q1 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||

d0 |

|

|

|

|

G |

d0 |

|

|

|

|

|

|

|

G |

|

|

|

d0 |

|

|

q0 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

б |

|

|

|

E |

|

|

G |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

Рис. 1.22. Схемы шифраторов: а – |

n = 1; б – n = 2 |

|

|

|

|

|

|

||||||||||||||||||

|

|

|

Рис. 1.23. Приоритетный |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

шифратор |

|||||||

|

|

|

|

|

|

|

|

|

|

|

Д |

||||||||||||||

Здесь при отсутствии входных сигналов (d0 = |

|

d1 =0) схема ИЛИ |

|||||||||||||||||||||||

даст на выходебАG = 0, а при G = 1 выход q0 = d1. |

|

|

|

|

|

||||||||||||||||||||

На рис. 1.22,б дана схема шифратора с двумя выходами (n = 2). Эта схема собрана уже на трех КЛУ типа ИЛИ. Логика ее работы сле-

дующая. При d3 |

= 1 на выходах всех трех |

|

будут единицы: G = 1, |

|

|

ИЛИ |

|

что означает поступление сигнала, q1 = 1, q0 |

= 1, что означает двоичный |

||

код на выходе 11, то есть число 3 в двоичной системе счисления. При d2 = 1 на выходе будет код 10, так как в этом случае q0 = 0, поскольку 0 0 = 0. Аналогично при d1 = 1 на выходе будет код 01, а при d0 = 1 – код 00.

Недостатком такого шифратора является то, что при одновременном поступлении на его вход не одного, а сразу нескольких сигналов на выходе может образоваться ошибочный код. Например, если на вход шифратора (см. рис. 1.22,б) подать одновременно d2 = 1 и d1 = 1, то на выходе будет код 11. Этот недостаток устраняется в приоритетном шифраторе, в котором при одновременной подаче на вход нескольких сигналов им воспринимается лишь сигнал с входа с большим номером.

Чтобы сделать рассмотренный шифратор (см. рис. 1.22,б) приоритетным необходимо при поступлении сигнала d2 = 1 заблокировать вход

31

d1. Такую блокировку можно осуществить с использованием микросхем И и НЕ (рис. 1.24,а).

d2 |

|

|

|

|

|

|

|

|

|

|

а |

d2 |

|

|

|

|

|

|

|

|

|

б |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

q0 |

|

|

|

|

|

|

|

|

|

|

q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

1 |

|

||

d1 |

|

|

|

|

|

& |

|

|

|

|

d1 |

|

|

|

|

& |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Рис. 1.24. Схемы блокировки сигналов с меньшим номером |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

в приоритетных шифраторах |

|

|

|

||||||||||

Чтобы уменьш ть число КЛУ в электронных схемах, элемент НЕ |

|||||||||||||||||||||||

и |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

часто заменяют нверсным входом в последующем элементе. Инверс- |

|||||||||||||||||||||||

Сные входы выходы обозначают на схемах белыми кружочками (по- |

|||||||||||||||||||||||

добно выходам элементов НЕ, И-НЕ, ИЛИ-НЕ). На рис. 1.24,б пред- |

|||||||||||||||||||||||

ставлена та же схема |

локировки сигнала d1 |

сигналом d2, в которой ис- |

|||||||||||||||||||||

бА |

|

|

|

||||||||||||||||||||

пользуется элемент И с инверсным входом.

Электронная промышленность выпускает стандартные микросхемы пр ор тетных ш фраторов типа К555ИВ1 (рис. 1.23). Они, в отличие от рассмотренных, имеют инверсные выводы (входы и выходы), и есть дополнительный вход E, локирующий все входные сигналы, и дополнительный выходной сигнал P – сигнал переноса в следующую такую же схему для каскадирования. Это позволяет на базе микросхемы К555ИВ1 собирать шифраторы с любым числом выходов.

|

|

|

|

|

|

|

|

|

Д |

||||||||||||||

Примеры на построение схем дешифраторов |

|

|

|

|

|||||||||||||||||||

Дешифратор с одним входом (n = 1) можно получить, используя |

|||||||||||||||||||||||

лишь один элемент НЕ (рис. 1.25,а). |

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

|

d1 d0 б |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

И |

|||||

|

|

|

|

|

|

|

|

|

|

|

d1 |

|

|

|

|

|

|

& |

|

|

q3 |

1 |

1 |

d0 |

|

|

|

|

|

q1 |

d0 |

|

|

|

d0 |

|

|

|

|

|

|

|

|

|

q2 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

& |

|

|

1 |

0 |

|||

|

|

|

|

|

|

q0 |

0 |

|

c1 |

|

|

|

|

|

|

|

|

|

|

q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

& |

|

|

0 |

1 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

c0 |

|

|

|

|

|

|

|

|

|

|

|

q0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Рис. 1.25. Схемы дешифраторов: а – с одним входом (n = 1); б – с двумя входами (n = 2)

Здесь при d0 = 0 сигнал поступит на выход q0, а при d0 = 0 – на q1. На рис. 1.25,б представлена схема дешифратора с двумя входами и четырьмя выходами (n = 2, 2n = 22 = 4). Ее особенность в том, что в ней имеются два управляющих сигнала c0 и c1, каждый из которых блокиру-

32

ет все выходы этой схемы. Стандартная микросхема ТТЛ логики К155ИД4 отличается от рассмотренной (рис. 1.25,б) лишь тем, что все ее выходы инверсные.

Примеры на построение схем мультиплексоров |

|

|

|||||||||||||||||

Мультиплексор с одним адресным входом (n = 1 – в этом случае у |

|||||||||||||||||||

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

него будет 2n = 21 = 2 информационных входов d0 и d1) можно получить, |

|||||||||||||||||||

используя следующую простую схему (рис. 1.26,а). |

|

|

|||||||||||||||||

a0 |

|

|

|

а |

|

|

a1 |

|

|

|

|

|

|

|

б |

|

|

||

и |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

d1 |

|

& |

|

|

|

|

a0 |

|

|

|

|

|

& |

|

|

|

|

|

|

d0 |

|

& |

|

1 |

|

q |

d3 |

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

d2 |

|

|

|

|

|

|

|

|

|

1 |

|

q |

|

бА |

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

d1 |

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d0 |

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 1.26. Схемы мультиплексоров: а – с одним адресным входом a0 (n = 1); |

|||||||||||||||||||

|

|

|

– с двумя адресными входами a0 |

и a1 (n = 2) |

|

|

|||||||||||||

Здесь при a0 = 0 с выходом коммутируется информационный вход

и, наконец, при a1a0 = 11 – входДd3. По тому же принципу можно построить мультиплексор с любым числом разрядовИn. Стандартная микросхема ТТЛ логики К155КП1 представляет собой четырехразрядный

d0, а при a0 = 1 – вход d1.

При построении мультиплексора с двумя входами используется та

же идея (рис. 1.26,б). При адресе a1a0 = 00 с выходом q коммутируется

информационный вход d0, при a1a0 = 01 – вход d1, при a1a0 = 10 – вход d2

мультиплексор, обеспечивающий мультиплексирование 24 = 16 информационных входов с выходом q.

Примеры на построение схем демультиплексоров

Демультиплексор легко получается из дешифратора. Достаточно добавить к дешифратору информационный вход d и соединить его со всеми конъюнкциями (И-элементами). Например, для дешифратора (см. рис. 1.25,б) таким способом получается демультиплексор, представленный на рис. 1.27,б. Как видно из данной схемы, при адресе a1a0 = 00 с входом d коммутируется выход q0, при a1a0 = 01 – выход q1, при a1a0 = 10 – выход q2 и, наконец, при a1a0 = 11 – выход q3.

33

Таким образом, в интегральном исполнении электронные схемы дешифратора и демультиплексора совпадают. Данное обстоятельство широко используется на практике. Например, есть такая стандартная интегральная схема К155ИД3, выполненная на базе ТТЛ логики

(рис. 1.27,а).

|

|

|

|

|

|

|

|

a3 |

|

|

q15 |

|

|

а |

a1 |

|

|

|

|

|

|

|

|

|

|

q3 |

a1 a0 б |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

DC |

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

1 |

1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

a2 |

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

a1 |

|

|

q9 |

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

q2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

и |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

d |

|

|

|

|

|

|

|

|

|

|

q1 |

0 |

1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

||||

|

|

|

|

|

& |

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Сd S1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

K |

|

|

|

|

|

|

|

S0 |

|

q0 |

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

q0 |

0 |

0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

Р с. 1.27. Схемы демультиплексоров: а – К155ИД3 (n = 4); |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

– с двумя входами (n = 2) |

|

|

|

|

|

|

||||||||

|

В этой |

нтегральной схеме все выводы инверсные. Если переклю- |

|||||||||||||||||||||||||||

чатель K включен на землю, то данная схема работает как дешифратор с |

|||||||||||||||||||||||||||||

четырьмя адресными входами, а при подключении с помощью этого |

|||||||||||||||||||||||||||||

ключа информационного входа d эта схема работает как четырехраз- |

|||||||||||||||||||||||||||||

рядный демультиплексор. |

Д |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

Контрольные вопросы и задания |

|

|

||||||||||||||||

1. |

КакоебАКЛУ называется шифратором? Как он работает? |

||||||||||||||||||||||||||||

2. |

Какое КЛУ называется дешифратором? Как он работает? |

||||||||||||||||||||||||||||

3. |

Какое КЛУ называется мультиплексором? Как он работает? |

||||||||||||||||||||||||||||

4. |

Какое КЛУ называется демультиплексором? Как он работает? |

||||||||||||||||||||||||||||

5. |

|

|

|

|

|

|

|

|

|

|

|

|

|

И |

|||||||||||||||

Начертите электронную схему простого шифратора с тремя вы- |

|||||||||||||||||||||||||||||

|

|

|

|

|

ходами (n = 3). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

6. |

Начертите электронную схему приоритетного шифратора с тре- |

||||||||||||||||||||||||||||

|

|

|

|

|

мя выходами (n = 3). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

7. |

Что представляет собой микросхема К555 |

В1 и для чего она |

|||||||||||||||||||||||||||

|

|

|

|

|

используется? |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

8. |

|

Начертите электронную схему дешифратора с тремя адресными |

|||||||||||||||||||||||||||

|

|

|

|

|

входами (n = 3). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

9. |

Что представляет собой микросхема К155 |

Д4 и для чего она |

|||||||||||||||||||||||||||

|

|

|

|

|

используется? |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

10.Начертите схему трехразрядного мультиплексора (n = 3).

11.Что представляет собой микросхема К155КП1 и для чего она используется?

12.Начертите схему трехразрядного мультиплексора (n = 3).

34

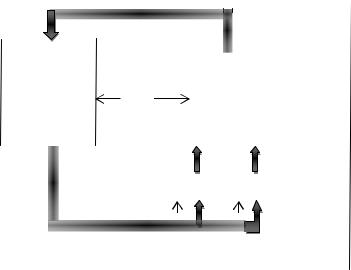

Практическое занятие №6 УММАТОРЫ. ИХ СХЕМЫ НА ЭЛЕМЕНТАХ И-ИЛИ-НЕ

Цели занятия: изучение принципов работы суммирующих цифровых схем; построение многоразрядных сумматоров, работающих в

двоичном коде. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

Кратк |

е теоретические сведения |

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

называются КЛУ, реализующие арифметическую |

||||||||||||||||||||

Соперац ю сложен я в двоичной системе счисления. |

|

|

|

|

|

|

||||||||||||||||||||||||

|

Элементарной суммирующей схемой является одноразрядный по- |

|||||||||||||||||||||||||||||

лусумматор, который по состоянию двух битов A и B формирует бит |

||||||||||||||||||||||||||||||

суммы S |

|

|

|

т переноса P. О означение одноразрядного полусуммато- |

||||||||||||||||||||||||||

ра представлено на р |

с. 1.28,а. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

умматорами |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A B C P S |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

HS |

|

|

|

|

|

A B P S |

|

A |

|

|

|

|

|

|

& |

P 0 0 0 0 0 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

A |

|

|

|

|

P |

|

|

|

0 0 0 0 |

B |

|

|

|

|

|

|

|

|

|

|

|

0 1 0 0 1 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

0 1 0 1 |

|

|

|

|

|

|

|

|

|

|

|

1 0 |

0 0 1 |

||||||

|

|

|

|

|

|

|

б |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

в |

|

|

|

|

||||||||||

|

|

B |

|

|

|

|

S |

|

|

|

1 0 0 1 |

|

|

|

|

|

|

|

|

=1 |

1 1 0 1 0 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

1 1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

а |

|

|

|

|

|

б |

|

|

|

|

A |

SM |

P |

|

|

|

0 |

1 |

1 1 |

0 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

Рис. 1.28. Одноразрядный полусумматор: |

|

|

B |

|

|

|

|

|

|

1 |

0 |

1 1 |

0 |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

А |

|

|

|

|

г |

|

|

1 1 1 д |

|||||||||||||

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

S |

|

1 |

1 |

|||||||||||||

а – обозначение; б – таблица истинности; |

|

|

|

|

|

|||||||||||||||||||||||||

в – схема |

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 1.29. Одноразрядный сумматор: |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

г – обозначение; д – таблица истинности |

||||||||||||||||

|

При сложении содержимогоДбитов A и B может произойти пере- |

|||||||||||||||||||||||||||||

полнение бита результата сложения S. В этом случае в бит P заносится |

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

И |

||||||||||||

единица. Зависимость выходных битов P и S от входных битов A и B задана таблицей истинности (рис. 1.28,б). Это таблица задает две логические функции P и S от булевых переменных A и B. Составим по данной

таблице д.н.ф. этих функций: |

|

||||||||

|

|

P A&B AB, |

(1.18) |

||||||

S ( |

|

&B) (A& |

|

) |

|

|

|

|

|

A |

B |

AB AB |

. |

(1.19) |

|||||

С учетом (1.5) из (1.19) следует |

|

||||||||

|

|

S A B. |

(1.20) |

||||||

Таким образом, схему одноразрядного полусумматора можно собрать с использованием двух логических элементов: конъюнкции & и сложения по модулю 2 =1 (см. рис. 1.29,в).

35

Полный сумматор имеет уже три входа (рис. 1.29,г). Третий входной бит C здесь является входным переносом выходного бита P от другого сумматора. В полном сумматоре его выходы P и S являются логическими функциями уже от трех булевых переменных: A, B и C. Его таблица истинности представлена на рис. 1.29,д.

Построим д.н.ф. этих функций по данной таблице. Получим фор- |

|||||||||||||||||

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

мулу для определения значения бита P |

(1.21) |

||||||||||||||||

P ABC |

ABC ABC ABC AB BC AC. |

||||||||||||||||

Здесь совершенная д.н.ф. преобразована в сокращенную с помо- |

|||||||||||||||||

щью булевой алгебры. Аналогично значение бита S будет |

|

||||||||||||||||

три |

|

|

|

|

|

|

|

|

|

|

|

|

(1.22) |

||||

|

S ABC ABC A BC ABC. |

||||||||||||||||

В данном случае для построения полного сумматора потребуется лог ческ х элемента И с двумя входами, что следует из (1.21), плюс четыре элемента И – с тремя входами (как прямыми, так и инверсными), что следует з (1.22), и еще два элемента ИЛИ – один согласно (1.21) с тремя входами, а другой с четырьмя – согласно (1.22). И это несмотря

на упрощен я с помощью улевой алгебры.

Сделаем так е прео разования. Вычислим из (1.21) инверсию выходного переноса

|

P AB BC AC (A B)(B C)(A C) |

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||

|

( |

|

|

|

|

|

|

|

|

|

|

|

)( |

|

|

|

|

|

|

) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

B |

A |

C |

B |

C |

A |

C |

A |

B |

BC AC . |

|

|

|

|

||||||||||||||||||||||||||||||||||||||

Используя этот результат, вычислим выражение |

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Д |

|

|

|

|

|||||||||||||||||||||||||||||||||

(A B C)P (A B C)(A B B C AC) AB C A BC ABC . |

||||||||||||||||||||||||||||||||||||||||||||||||||||

ТогдабАиз (1.21) получается следующее выражение для разряда |

||||||||||||||||||||||||||||||||||||||||||||||||||||

суммы: |

|

|

|

|

|

S (A B C)P ABC. |

(1.23) |

|||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||

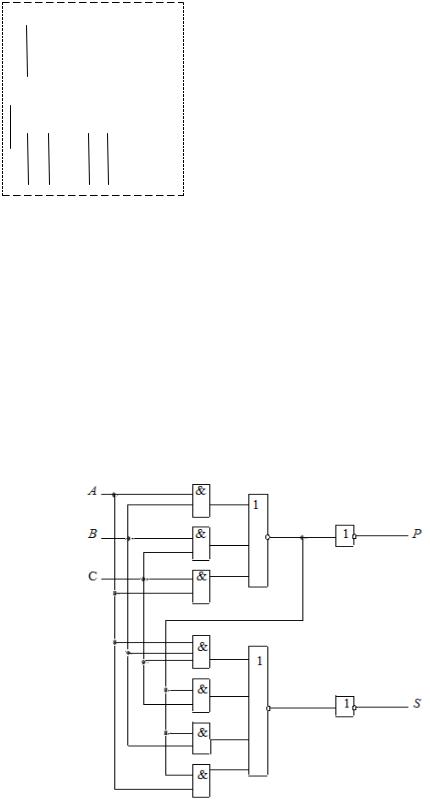

Используя выражения (1.21) и (1.23), можно реализовать однораз- |

||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

И |

||||||||||||||||||||||||||

рядный полный сумматор на базе двухступенчатой схемы. Первая ступень такой схемы обеспечит формирование сигнала P по формуле (1.21). Для этого потребуется 3 элемента И с двумя входами и один элемент ИЛИ с тремя входами. Вторая ступень сформирует сигнал S. Для данной реализации согласно (1.23) потребуется элемент НЕ для инверсии сигнала P, элемент ИЛИ с тремя входами, элемент с двумя входами, элемент И с тремя входами и еще элемент ЛИ с двумя входами. Итого на реализацию такого всего лишь одноразрядного сумматора с двухступенчатой схемой потребуется 9 КЛУ.

Однако можно поступить и более простым способом. Используя два полусумматора и комбинационную логическую схему ИЛИ, можно собрать следующую схему (рис. 1.30).

36

|

|

|

|

|

|

|

|

|

|

SM |

|

|

|

|

|

|

|

x2 |

|

|

A |

SM |

P |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

A |

|

|

A |

HS |

P |

|

|

|

|

|

|

|

|

|

|

|

|

|

y2 |

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

B |

|

|

B |

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

S |

|

|

|

|

|

s2 |

S = X + Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X(x2, x1, x0) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

SM |

P |

|

|

|

|

||||||||||||

Схема |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

P |

|

|

|

|

y1 |

|

|

B |

|

|

|

|

|

|

|

|

|

|

+ Y(y2, y1, y0) |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|