- •1.1. Этапы управления производственными процессами

- •1.2. Классификация систем телемеханики

- •2.2. Квантование

- •2.3. Кодирование

- •2.3.1. Основные понятия

- •2.3.2. Цифровые коды

- •2.3.3. Простые двоичные коды

- •2.3.4. Оптимальные коды

- •2.3.5. Корректирующие коды

- •2.4. Методы модуляции

- •2.5. Достоверность передачи информации

- •2.6. Организация каналов связи для передачи информации

- •3. СОСТАВ ТЕЛЕМЕХАНИЧЕСКИХ УСТРОЙСТВ

- •3.1. Основные элементы, узлы и схемы телемеханики

- •3.3. Сельсины

- •3.4. Дешифраторы, шифраторы, триггеры и счетчики

- •3.5. Регистры, распределители и коммутаторы

- •4. ОСНОВНЫЕ ПРИНЦИПЫ ТЕЛЕМЕХАНИКИ

- •4.1. Передача и прием телемеханических сигналов

- •4.2. Телеуправление и телесигнализация

- •4.3. Телеизмерение

- •4.4. Представление информации в системах телемеханики

- •Библиографический список

Желательно, чтобы Хп было как можно меньше.

Основная погрешность преобразования – это максимальная разность между фактическим значением выходного сигнала Хвых ф и его номинальным значением Хвых н, выраженная в процентах от разности предельных значений выходного сигнала Хвых max и Хвых min:

СибАДХвыхф Хвыхн 100%. И(3.2.7) Хвыхmax Xвыхmin

нам ческ й режим работы датчика характеризуется кривой динам ческого процесса, которая отражает характер изменения выходного с гнала в функции времени при скачкообразном изменении сигнала на входе (р с. 3.2.4).

Хвх

t

Хвых

t

t0

Рис. 3.2.4. Временные диаграммы динамического режима датчика

3.3. Сельсины

Сельсин – это миниатюрная электрическая машина, сходная с трехфазным синхронным генератором или двигателем.

Конструктивное исполнение сельсинов может быть различным. Обычно ротор имеет однофазную обмотку, а статор – трехфазную (три обмотки, расположенные в пространстве друг относительно друга под углом 120°).

84

Схема включения сельсинной пары в индикаторном режиме при- |

|||

ведена на рис. 3.3.1. |

|

||

|

ельсины всегда работают в паре. Один из сельсинов называется |

||

сельсином-датчиком СД, а другой – сельсином-приемником СП. Угол |

|||

поворота ротора СД преобразуется в электрический сигнал, который |

|||

передается по проводам (на любое расстояние) и воспринимается СП. |

|||

Поступивший сигнал преобразуется в такое же угловое перемещение |

|||

ротора |

П. В с стемах автоматики сельсинные пары применяются в |

||

двух основных реж мах: индикаторном и трансформаторном. |

|||

|

|

~110 В |

|

|

|

СД |

СП |

|

|

Рис. 3.3.1. Индикаторный режим работы сельсинной пары |

|

|

Роторы обоих сельсинов подключены к источнику переменного |

||

тока, трехфазные статорные обмотки, включенные по схеме «звез- |

|||

да», соединены между собой. |

|

||

|

Однофазный переменный ток ротора создает в магнитной цепи |

||

каждого сельсина переменный магнитный поток, который индуциру- |

|||

ет в обмотках статора ЭДС. При одинаковых положениях роторов |

|||

СД |

СП ЭДС в каждой фазе СД уравновешивается соответствующей |

||

ЭДС СП. Поэтому ток в обмотках статора отсутствует. При повороте |

|||

ротора СД ЭДС в обмотках статора СД изменяются, в результате че- |

|||

го нарушается равновесие с ЭДС обмоток статора СП. Под действи- |

|||

СибАДИ |

|||

ем разности ЭДС в цепи статоров протекают уравнительные токи. |

|||

|

Взаимодействие этих токов с магнитным потоком создает на ва- |

||

лах СД и СП синхронизирующий момент, стремящийся свести угол |

|||

рассогласования θ=αСД–αСП к нулю. Однако этот момент мал и прак- |

|||

тически достаточен лишь для перемещения стрелок или других ука- |

|||

зательных устройств, поэтому индикаторный режим применяется |

|||

обычно в системах контроля. |

|

||

85

В зависимости от величины θ сельсины делятся на 4 класса точ- |

|||

ности, каждый из которых определяется по максимально возможной |

|||

средней ошибке |

1 2 , |

|

|

|

|

(3.3.1) |

|

|

|

2 |

|

где θ1 и θ2 – абсолютные значения максимальных ошибок, получен- |

|||

ные при вращен |

ротора СД по и против часовой стрелки. |

||

ельс нная пара рассматривается как безынерционное устройст- |

|||

во. Погрешность сельсинов обычно не превышает десятых долей |

|||

градуса. Главными пр чинами возникающих погрешностей являются |

|||

дефекты |

зготовлен я: электрическая |

магнитная асимметрия, не- |

|

точная центровка, элл птичность ротора и т.д. |

|||

хема включен я сельсинной пары в трансформаторном режи- |

|||

ме приведена на р с. 3.3.2. |

|

||

|

|

|

N |

~110 В |

V |

|

|

|

|

СД |

СП |

Рис. 3.3.2. Трансформаторный режим работы сельсинной пары |

|||

Отличие трансформаторного режима от индикаторного в том, что |

|||

СибАДИ |

|||

однофазная обмотка ротора СП подключается не к источнику пита- |

|||

ния, а ко входу усилителя (т.е. является выходной). На лабораторном |

|||

стенде ротор СП заторможен, а в схемах следящих систем ротор ме- |

|||

ханически жестко связан с валом исполнительного двигателя. Такая |

|||

схема применяется для передачи движения на исполнительные уст- |

|||

ройства, нагруженные большими моментами. |

|||

86

Выходное напряжение будет равно нулю при разности углов поворота 90°, так как результирующий магнитный поток в этом случае не будет пересекать витки ротора СП. Это положение принимается за нулевое. Любое рассогласование сопровождается появлением напряжения на выходе, причем выходное напряжение является функ-

цией синуса угла рассогласования: |

|

СибАДИ |

|

uвых=k sinθ, |

(3.3.2) |

где k=1 В/град. |

|

Для достаточно малых углов |

|

uвых=k θ. |

(3.3.3) |

Эти выражен я отражают не только зависимость величины выходного напряжен я от угла рассогласования, но и зависимость фазы этого напряжен я от знака рассогласования. При изменении знака рассогласован я фаза выходного напряжения меняется на 180°.

Трансформаторный режим работы сельсинов широко применяется в следящих системах, предназначенных для синхронного вращения двух валов, механически между собой не связанных. Один из валов является входным (например, вал стрелкового прицела) и обычно требует для своего перемещения небольших усилий, другой – выходным (например, вал, связанный с самолетной пушкой), для его перемещения, как правило, необходимы значительные усилия.

3.4. Дешифраторы, шифраторы, триггеры и счетчики

На базе логических элементов построены такие устройства, как шифраторы, дешифраторы. Условное обозначение таблица истинности шифратора приведены в табл. 3.4.1.

Шифратор (кодер) преобразует сигнал на одном из его входов в n-разрядное двоичное число. При появлении сигнала логической единицы на одном из десяти входов на четырех выходах шифратора будет присутствовать соответствующее двоичное число.

Дешифратор (декодер) преобразует код, поступающий на его n-входов, в сигнал логической единицы только на одном из его выходов. Условное обозначение и таблица истинности дешифратора приведены в табл. 3.4.2.

87

Таблица 3.4.1

Условное обозначение и таблица истинности шифратора

Условное обозначение |

«1» на |

|

Выходы |

|

||

шифратора |

входе |

1 |

2 |

4 |

8 |

|

|

|

0 |

0 |

0 |

0 |

0 |

СибАДИ |

||||||

0 |

CD |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

2 |

0 |

0 |

1 |

0 |

2 |

3 |

0 |

0 |

1 |

1 |

|

3 |

2 |

|||||

4 |

4 |

4 |

0 |

1 |

0 |

0 |

5 |

5 |

0 |

1 |

0 |

1 |

|

6 |

8 |

6 |

0 |

1 |

1 |

0 |

7 |

|

7 |

0 |

1 |

1 |

1 |

8 |

|

|||||

9 |

|

8 |

1 |

0 |

0 |

0 |

|

|

9 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 3.4.2 |

|

Условное о означение |

та лица истинности дешифратора |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Условное обозначение |

|

|

Входы |

|

«1» на |

||||||||||

|

|

|

|

дешифратора |

|

1 |

2 |

4 |

8 |

выходе |

|||||

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

DC |

0 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

0 |

0 |

1 |

0 |

2 |

||||||||||

|

|

|

|

|

|

1 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

1 |

|

2 |

|

|

|

|

0 |

0 |

1 |

1 |

3 |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

0 |

1 |

0 |

0 |

4 |

||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

4 |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

1 |

5 |

||||

|

|

4 |

|

5 |

|

|

|

|

|||||||

|

|

||||||||||||||

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

8 |

|

6 |

|

|

|

|

0 |

1 |

1 |

0 |

6 |

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

||||||||||

|

|

7 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

0 |

1 |

1 |

1 |

7 |

|||||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

8 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

8 |

||||

|

|

|

|

|

|

9 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Дешифратор n-разрядного двоичного числа имеет 2n выходов. Различные типы дешифраторов применяются в схемах цифровой индикации информации. Особенно широко применяются дешифраторы, преобразующие информацию в код для семисегментных индикаторов.

88

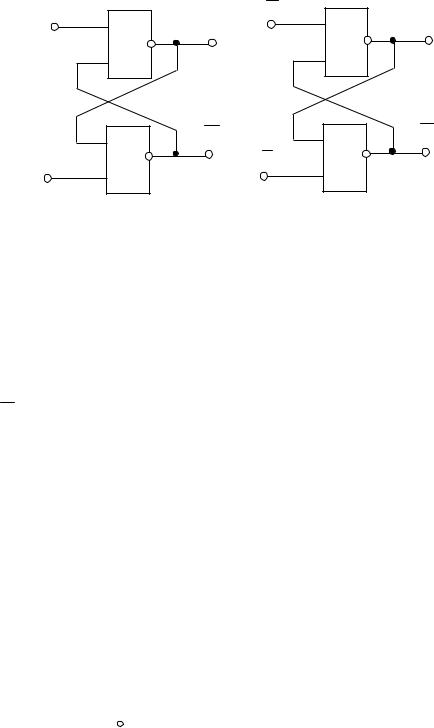

RS-триггер. Простейший RS-триггер можно реализовать на логических элементах ИЛИ-НЕ и И-НЕ, как показано на рис. 3.4.1.

R |

Q |

R |

Q |

1 |

& |

||

СибАДИ |

|||

1 |

Q |

& |

Q |

S |

|

S |

|

а) |

|

б) |

|

Р с. 3.4.1. RS-триггер, реализованный на |

|

||

лог ческ х элементах ИЛИ-НЕ (а) и И-НЕ (б) |

|

||

Ас нхронный RS-триггер имеет два информационных входа: R и S. Входы S R названы по первым буквам английских слов set – установка и reset – с рос. При S=1 и R=0 на выходах триггера появляются сигналы: на прямом выходе Q=1, на инверсном Q =0. При S=0 и R=1 выходные сигналы триггера принимают противоположные состояния (Q=0; Q =1). Этот триггер не имеет тактового входа. Условное обозначение и таблица истинности RS-триггера приведены в табл. 3.4.3.

Таблица 3.4.3

Схемное обозначение

таблица истинности асинхронного RS-триггера

|

|

Схемное |

Входные |

|

Состояние |

|||||||

|

обозначение |

сигналы |

|

|

выхода |

|||||||

|

|

|

|

|

|

|

R |

|

S |

Q(t) |

|

Q(t+1) |

|

|

|

|

|

Q |

0 |

|

0 |

0 |

|

0 |

|

|

|

|

T |

|

|

|||||||

|

|

R |

|

|

0 |

|

0 |

1 |

|

1 |

||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

Q |

0 |

|

1 |

0 |

|

1 |

|

|

|

S |

|

|

0 |

|

1 |

1 |

|

1 |

||

|

|

|

|

|

|

1 |

|

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

1 |

|

0 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

1 |

|

1 |

0 |

|

Не |

|

|

|

|

|

|

|

1 |

|

1 |

1 |

|

определено |

89

RS-триггер не допускает одновременного наличия на входах ак- |

||||||

тивных сигналов S=1; R=1. В этом случае не выполняется условие его |

||||||

функционирования, поскольку на выходах Q и Q логические уровни |

||||||

перестают быть взаимно инверсными, состояние выхода оказывается |

||||||

неопределенным. Данные комбинации считаются запрещенными. |

||||||

Режим S=1; R=0 называют режимом записи 1, так как Q(t+1)=1; |

||||||

режим S=0 и R=1 – режимом записи 0, так как Q(t+1)=0; режим S=0; |

||||||

R=0 – реж мом хранен я информации, так как информация на выходе |

||||||

остается не зменной. |

|

|

|

|||

Временная д аграмма асинхронного RS-триггера изображена на |

||||||

рис. 3.4.2. |

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

t |

S |

|

|

|

|

|

|

Q |

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

Рис. 3.4.2. Временная диаграмма |

|

||

|

|

|

асинхронного RS-триггера |

|

||

Синхронный RS-триггер отличается от асинхронного наличием |

||||||

входа С для синхронизирующих тактовых импульсов. Переключение |

||||||

этого триггера под действием сигналов на входах R и S происходит |

||||||

только при появлении высокого уровня на тактовом входе С, что хо- |

||||||

рошо видно на временной диаграмме. |

|

|

||||

Схемное |

обозначение |

временная |

диаграмма |

синхронного |

||

RS-триггера приведены на рис. 3.4.3. |

|

|

||||

СибАДИC |

||||||

|

R |

ТТ |

Q |

|

|

t |

|

S |

|

t |

|||

|

C |

|

|

|

||

|

|

Q |

R |

|

t |

|

|

S |

|

|

Q |

|

t |

Рис. 3.4.3. Схемное обозначение и временная диаграмма |

||||||

|

|

|

синхронного RS-триггера |

|

||

90

D-триггер. Условное обозначение и таблица истинности D- триггера приведены в табл. 3.4.4.

Таблица 3.4.4

хемное обозначение и таблица истинности D-триггера с потенциальным управлением

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

СибАДИ |

|

|

||||||||||||

|

|

|

Схемное |

Входные |

Состояние |

|

|

|||||||

|

|

обозначен е |

сигналы |

выхода |

Примечание |

|

||||||||

|

|

|

|

|

|

|

|

|

С |

D |

Q(t) |

Q(t+1) |

|

|

|

|

|

D |

T |

Q |

0 |

0 |

0 |

0 |

Хранение |

|

|||

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

Q |

1 |

0 |

0 |

0 |

Запись «0» |

|

|||

|

|

|

C |

|

|

|

|

|

1 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

Запись «1» |

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

|

|

D-тр ггер (тр ггер задержки) – это устройство с двумя устойчивыми состояниями и двумя входами: информационным входом D переключения триггера в состояние, соответствующее логическому уровню на этом входе, и синхронизирующим входом С. Этот триггер может быть только синхронным. D-триггеры могут быть с потенциальным и динамическим управлением.

У D-триггеров с потенциальным управлением информация со входа D переписывается на выход Q в течение времени, при котором синхросигнал активен: =1. При пассивном синхросигнале триггер не чувствителен к изменениям информационного сигнала (рис. 3.4.4).

C

t

D

t

Q

t

Рис. 3.4.4. Временная диаграмма D-триггера со статическим управлением

91

В триггерах с динамическим управлением информация записыва- |

||||

ется (передается на выход Q) по фронту или спаду сигнала синхрони- |

||||

зации на входе С. |

|

|

||

Временная диаграмма D-триггера с динамическим управлением |

||||

по спаду сигнала синхронизации приведена на рис. 3.4.5. |

||||

|

|

D |

|

|

D ТТ |

Q |

|

t |

|

C |

|

C |

|

|

|

Q |

|

||

|

|

|

||

|

|

|

t |

|

|

|

Q |

|

|

|

|

|

t |

|

Рис. 3.4.5. Схемное о означение и временная диаграмма D-триггера |

||||

с динамическим управлением по спаду сигнала синхронизации |

||||

|

|

Т-триггер. Т-триггер – это устройство с |

||

D ТТ |

Q |

двумя устойчивым |

состояниями и одним |

|

счетным (информационным) входом Т. Счёт- |

||||

C |

|

|||

|

ным он называется потому, что подсчитывает |

|||

|

Q |

количество импульсов, поступивших на его |

||

|

|

вход. |

|

|

Рис. 3.4.6. Т-триггер |

Триггер переключается каждый раз в про- |

|||

на базе D-триггера |

тивоположное состояние по фронту или по |

|||

|

|

спаду управляющего |

сигнала на входе Т. |

|

Т-триггер может быть выполнен на основе D-триггера с |

||||

динамическим управлением путем соединения инверсного выхода со |

||||

входом D (рис. 3.4.6). Счетный триггер из D-триггера с |

||||

СибАДИ |

||||

потенциальным управ-лением получить нельзя. |

||||

Т-триггеры используются при построении схем различных счёт- |

||||

чиков, поэтому в составе больших интегральных схем различного на- |

||||

значения обычно есть готовые модули этих триггеров. |

||||

Схемное обозначение Т-триггера, работающего по спаду синхро- |

||||

низирующего сигнала, и его временная диаграмма приведены на |

||||

рис. 3.4.7. |

|

|

|

|

|

|

92 |

|

|

|

|

|

T |

|

|

|

|

|

|

|

|

ТТ |

|

Q |

|

|

|

|

|

|

|

|

t |

|

|

Q |

|

|

|

|

|

|

|

|

|

Т |

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

Р с. 3.4.7. Схемное обозначение Т-триггера, работающего по спаду |

|||||||||||

|

с нхрон з рующего сигнала, и его временная диаграмма |

||||||||||

JK-тр ггер. |

Условное |

|

о означение |

и |

таблица |

истинности |

|||||

JK-триггера пр |

ведены в та л. 3.4.5. |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

Таблица 3.4.5 |

|

Схемное о означение и та лица истинности JK-триггера |

||||||||||

Схемное |

|

Входы |

|

Состояние |

|

|

|

|

|||

обозначение |

|

|

выходов |

|

|

Примечание |

|||||

|

|

|

|

|

|

||||||

|

|

|

|

K |

J |

Q(t) Q(t+1) |

|

|

|

|

|

S |

TT |

Q |

0 |

* |

* |

0 |

0 |

Режим хранения информации |

|||

0 |

* |

* |

1 |

1 |

|

|

|

|

|||

J |

|

|

1 |

0 |

0 |

0 |

0 |

Режим хранения информации |

|||

K |

|

|

1 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

1 |

0 |

1 |

0 |

1 |

|

|

|

|

|

C |

|

Q |

Режим установки единицы J=1 |

||||||||

|

|

1 |

0 |

1 |

1 |

1 |

|

|

|

|

|

R |

|

|

1 |

1 |

0 |

0 |

0 |

Режим записи нуля K=1 |

|||

|

|

|

1 |

1 |

0 |

1 |

0 |

||||

|

|

|

|

|

|

|

|||||

|

|

|

1 |

1 |

1 |

0 |

1 |

Счетный режим триггера J=K=1 |

|||

|

|

|

1 |

1 |

1 |

1 |

0 |

|

|

|

|

Примечания: 1. * – любое состояние входа. |

|

|

|

|

|||||||

|

|

2. Таблица справедлива при R=S=0. |

|

|

|||||||

СибАДИ |

|||||||||||

JK-триггер имеет два |

выхода: прямой Q и инверсный Q . |

||||||||||

JK-триггер имеет пять входов: R – асинхронный вход установки в со- |

|||||||||||

стояние 0 (Q=0); |

S – |

асинхронный |

вход |

установки |

в состояние |

||||||

1 (Q=1); К – синхронизируемый вход установки в состояние 0 (Q=0); |

|||||||||||

J – синхронизируемый вход установки в состояние 1 (Q=1); С – син- |

|||||||||||

хронизирующий вход. |

|

|

|

|

|

|

|

|

|||

93

Асинхронные входы R и S работают так же, как в RS-триггере, независимо от сигналов на остальных входах: режим S=1; R=0 – режим записи 1; режим S=0 и R=1 – режим записи 0; режим S=R=0 – режим хранения информации. Не допускается одновременное наличие на входах R и S активных сигналов S=R=1.

При S=R=0 логика работы входов J, K и C такова: если на входе СJ логическаяи1, абАДИна входе K – логический 0, то по спаду синхроимпульса на входе C тр ггер установится в состояние 1. Если на входе J – лог ческ й 0, а на входе K – логическая 1, то по спаду синхроимпульса на входе C тр ггер установится в состояние 0. В случае, когда и на входах J K лог ческие нули, то независимо от сигнала на входе C состоян е тр ггера не меняется. И последний режим работы, когда на входах J K лог ческие единицы, JK-триггер работает в режиме делителя частоты с гнала на входе С. Это означает, что по заднему фронту каждого тактового импульса состояние триггера меняется на

противоположное.

Из табл. 3.4.5 ст нности JK-триггера видно, что при J=1 и K=0 триггер по тактовому мпульсу устанавливается в состояние 1 (Q=1). При J=0 и К=1 триггер по тактовому импульсу устанавливается в состояние 0 (Q=0); при J=K=0 триггер хранит ранее принятую информацию независимо от сигнала на синхронизирующем входе С; при J=K=1 состояние выхода Q триггера с каждым импульсом на синхронизирующем входе изменяется на противоположное. Триггер становится делителем частоты на 2.

C

t

J

t

K

t

Q

t

Q

t

Рис. 3.4.8. Временная диаграмма JK-триггера при R=S=0

94

На рис. 3.4.8 приведена временная диаграмма JK-триггера, иллю- |

||||

стрирующая переключение триггера по спаду синхронизирующего |

||||

сигнала в зависимости от состояния входов J и K. |

||||

четчики. На рис. 3.4.9 приведены условное обозначение четы- |

||||

рехразрядного двоичного счетчика и его временная диаграмма. |

||||

Т2 |

1 |

C |

|

|

|

|

|||

D0 |

|

t |

||

D1 |

2 |

1 |

||

D2 |

4 |

2 |

t |

|

D3 |

8 |

|||

|

||||

V |

|

4 |

t |

|

C |

|

|||

|

|

|||

|

|

|

||

R |

|

8 |

t |

|

PI |

Р |

|

||

|

t |

|||

а |

|

|

||

|

|

б |

||

Рис. 3.4.9. Условное о означение четырехразрядного двоичного счетчика (а) |

||||

|

|

и его временная диаграмма (б) |

||

Входы D0–D3 |

называются информационными входами и служат |

|||

для записи в счетчик какого-либо двоичного состояния. Это состоя- |

||||

ние отобразится на его выходах и от него будет производиться начало |

||||

отсчета. Другими словами, это входы предварительной установки. |

||||

Вход V разрешения предустановки служит для разрешения записи ко- |

||||

да по входам D0–D3. Предварительная запись в счетчик производится |

||||

при подаче сигнала разрешения записи на вход V в момент прихода |

||||

импульса на тактовый (счетный) вход |

. Знак «\» на входе С означает, |

|||

что счетчик срабатывает по спаду импульса. Знак «/» на входе С оз- |

||||

начает, что счетчик срабатывает по фронту импульса. |

||||

Вход R служит для обнуления счетчика, т. е. при подаче импуль- |

||||

СибАДИса на этот вход на всех выходах счетчика устанавливается логический |

||||

ноль. Вход PI называется входом переноса. Выход P называется вы- |

||||

ходом переноса. На этом выходе формируется сигнал при переполне- |

||||

нии счетчика (когда на всех выходах устанавливаются логические |

||||

единицы). Этот сигнал обычно подается на вход переноса следующе- |

||||

го счетчика. На выходах 1,2,4,8 формируется двоичный код, соответ- |

||||

ствующий числу поступивших на вход счетчика импульсов. Как вид- |

||||

95