anton

.docМИНИСТЕРСТВО оБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

Московский государственный институт электроники и математики

МИЭМ НИУ ВШЭ

Кафедра «Электроника и электротехника»

КУРСОВАЯ РАБОТА

на тему

«N-МОП транзистор. Схема ИЛИ-НЕ»

по дисциплине «Электроника»

Вариант №112

|

Выполнил: студент группы С–21 Макаренко А. М. |

Руководитель: Харитонов И.А. ______________ |

Москва 2014

1. Исходные данные для проектирования

-

Вариант №112

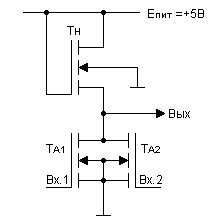

ИЛИ – НЕ схема на n – МОП транзисторах

Минимальный размер: 5 мкм

Толщина окисла: 60 нм

2. Принцип работы схемы

Для логических схем на n - МОП транзисторах уровень логического нуля приблизительно равен нулю, а уровень логической единицы ― меньше чем EПИТ.

Затвор и сток нагрузочного транзистора подключены к питанию, в любой момент времени выполняется неравенство UЗИ – UПОР < UСИ, поэтому нагрузочный транзистор всегда открыт и работает как резистор.

Если

на хотя бы один активный транзистор

подается напряжение, равное

![]() ,

то

он оказывается открыт и ток уходит в

землю. На выходе формируется уровень

напряжения, соответствующий

,

то

он оказывается открыт и ток уходит в

землю. На выходе формируется уровень

напряжения, соответствующий

![]() (порядка

0.1– 0.3 В).

(порядка

0.1– 0.3 В).

Если

на оба активных транзистора подано

напряжение

![]() ,

то они оба заперты, выход отключается

от земли и на нем устанавливается

напряжение

,

то они оба заперты, выход отключается

от земли и на нем устанавливается

напряжение

![]() .

Стоит

заметить, что уровень

.

Стоит

заметить, что уровень

![]() на выходном электроде всегда меньше,

чем EПИТ

вследствие влияния нагрузочного

транзистора.

на выходном электроде всегда меньше,

чем EПИТ

вследствие влияния нагрузочного

транзистора.

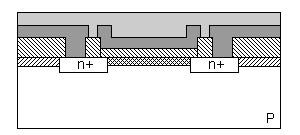

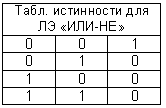

3. Технология изготовления МОП – транзистора

В этом пункте опишем технологический процесс производства n – канального МОП – транзистора с алюминиевым затвором.

|

|

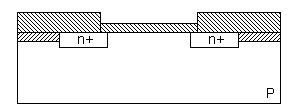

1)

Получение исходной подложки р-типа

со структурой (100) ( |

|

|

2) Выращивание толстого защитного слоя окисла |

|

|

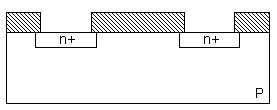

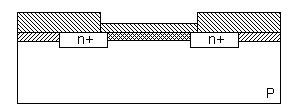

3) Фотолитография для вскрытия областей истока и стока n+-типа |

|

|

4) n+ - диффузия |

|

|

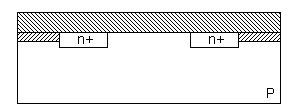

5) выращивание окисла |

|

|

6) Фотолитография для р - ограничителей канала |

|

|

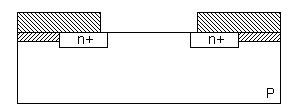

7) Диффузия или внедрение ионов р - типа |

|

|

8)

рост

окисла ( |

|

|

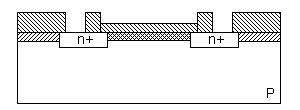

9) Фотолитография для тонких слоев окисла под затворы, и вскрытие окон под выводы.

|

|

|

10)

Термическое

выращивание тонкого слоя окисла под

затворами ( |

|

|

11) Ионное внедрение бора для регулировки UЗИпор n – МОП - приборов. Отжиг для активации внедренных ионов и восстановления повреждений кристаллической решетки |

|

|

12) Фотолитография для вскрытия окон под контакты истока и стока |

|

|

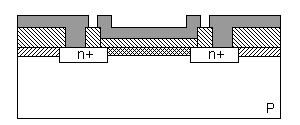

13) Осаждение парообразного алюминия |

|

|

14) Фотолитография для формирования рисунка металлической разводки и контактных площадок |

|

|

15) Нанесение низкотемпературного пиролитического стекла |

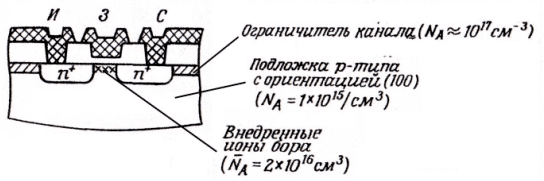

4. Топология и структура МОП – транзисторов в разрезе

В схеме, исследуемой в данном курсовом проекте присутствует два типа МОП – транзисторов: активный и нагрузочный. Основной отличительной особенностью активных транзисторов является короткий и широкий канал, тогда как у нагрузочных транзисторов он длинный и узкий.

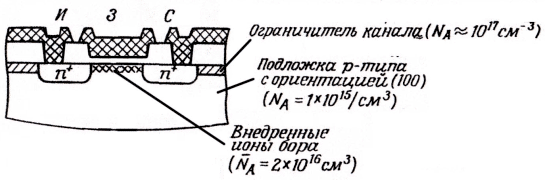

Структура активного МОП – транзистора в разрезе:

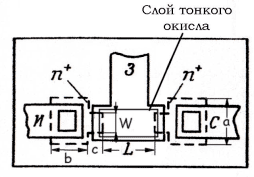

Топология активного МОП – транзистора:

Структура нагрузочного МОП – транзистора в разрезе:

Топология нагрузочного МОП – транзистора:

5. Расчет параметров схемы

Для определения параметров n – канальных МОП – транзисторов, рассматриваемых в данном курсовом проекте, воспользуемся выражениями, приведенными в книге У. Тилла и Дж. Лаксона «Интегральные схемы. Материалы, приборы, изготовление».

В первую очередь найдем пороговое напряжение на затворе UЗИ.ПОР и пороговое напряжение на окружающем окисле UП.ПОР

![]() - пороговое

напряжение на затворе, где:

- пороговое

напряжение на затворе, где:

Uf – потенциал Ферми, UД – падение напряжение на слое окисла,

USS – поверхн. заряд на границе раздела Si – SiO2 для кремния структуры 100,

UW – напряжение работы выхода

![]() - потенциал

Ферми, где:

- потенциал

Ферми, где:

![]() -

постоянная Больцмана

-

постоянная Больцмана

![]() -

температура транзистора

-

температура транзистора

![]() - заряд

электрона

- заряд

электрона

![]() -

концентрация носителей в кремнии

-

концентрация носителей в кремнии

![]() -

концентрация ионов, имплантированных

в канал

-

концентрация ионов, имплантированных

в канал

подставим данные значения в уравнение, получим:

![]()

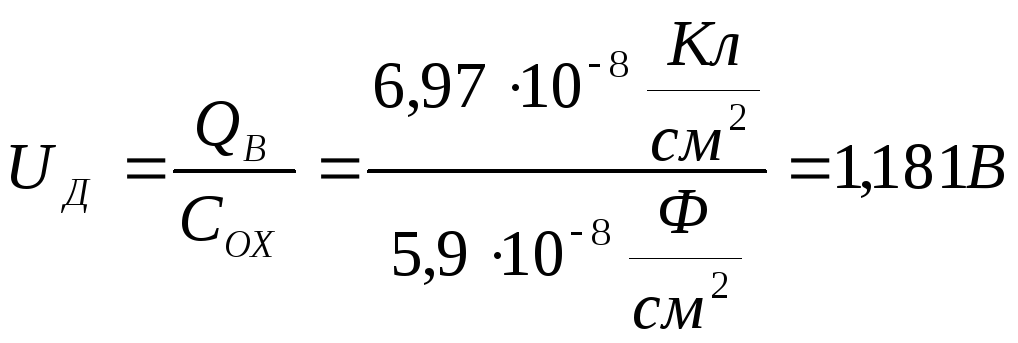

![]() -

падение

напряжения на слое окисла, где:

-

падение

напряжения на слое окисла, где:

![]() -

заряд приповерхностного слоя кремния

-

заряд приповерхностного слоя кремния

![]()

![]() -

диэлектрическая проницаемость вакуума

-

диэлектрическая проницаемость вакуума

![]() -

диэлектрическая проницаемость кремния

-

диэлектрическая проницаемость кремния

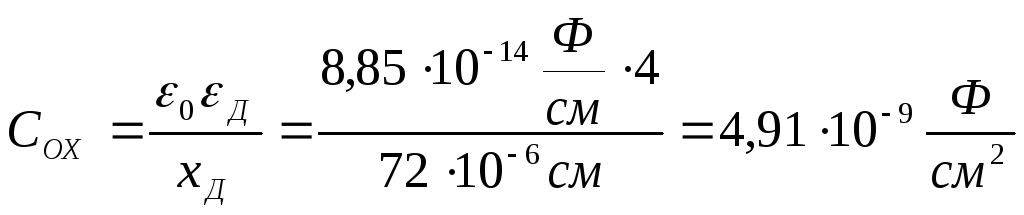

![]() -

удельная емкость подзатворного

диэлектрика,

где:

-

удельная емкость подзатворного

диэлектрика,

где:

![]() -

диэлектрическая проницаемость оксида

кремния SiO2

-

диэлектрическая проницаемость оксида

кремния SiO2

![]() -

толщина

слоя тонкого окисла

-

толщина

слоя тонкого окисла

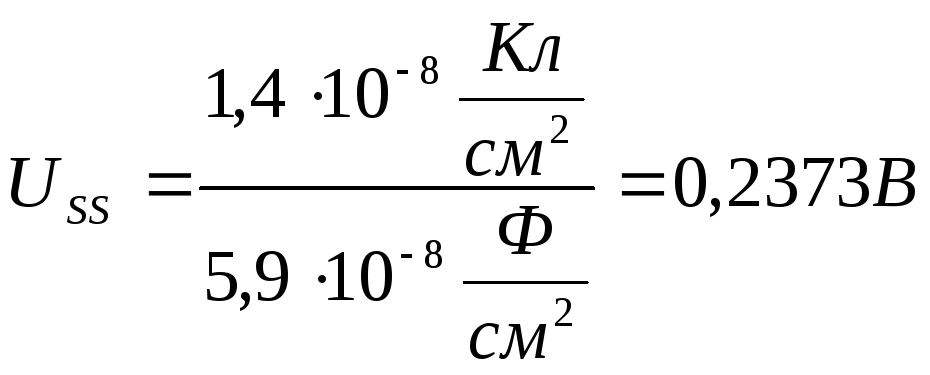

![]() -напряжение,

компенсирующее поверхностный заряд,

где

-напряжение,

компенсирующее поверхностный заряд,

где

![]() -

поверхностный заряд на границе раздела

Si

– SiO2

-

поверхностный заряд на границе раздела

Si

– SiO2

![]() -

напряжение

работы выхода (пост. для данного вещества),

где

-

напряжение

работы выхода (пост. для данного вещества),

где

![]() ― работа

выхода из металла в зону проводимости

Si.

― работа

выхода из металла в зону проводимости

Si.

![]() ―

работа

выхода из

металла в SiO2

―

работа

выхода из

металла в SiO2

![]() ―

работа

выхода из

кремния в SiO2

―

работа

выхода из

кремния в SiO2

![]()

Окончательно получаем:

![]()

Толщина толстого слоя окисла: 0.72 мкм

Концентрация ионов, ограничителей канала: NA = 1017 атомов/см3

![]()

![]() -

заряд приповерхностного слоя окисла

-

заряд приповерхностного слоя окисла

![]()

![]()

![]()

![]()

![]()

![]()

Таким образом, ограничитель канала не будет проводящим, пока к алюминию на окружающем окисле не будет приложено напряжение в 28,75В.

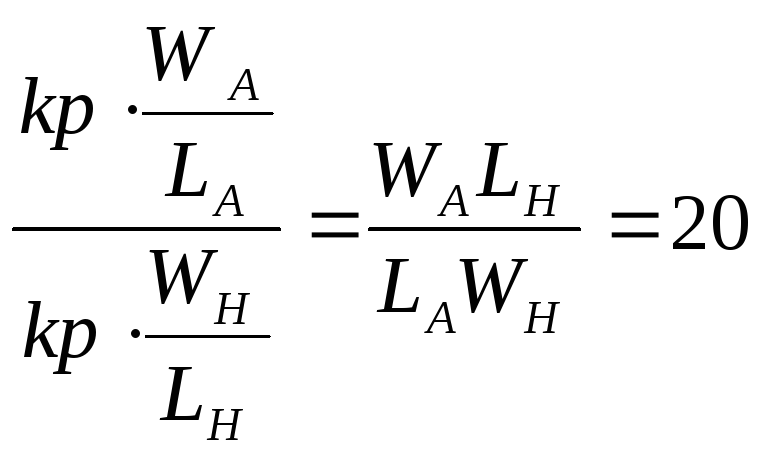

Условие помехоустойчивости требует соотношения между крутизнами активного и нагрузочного транзисторов 20:1, т.е.

![]() ,

раскроем это выражение:

,

раскроем это выражение:

,

где

,

где

![]()

Для достижения этого, LAWH должно быть минимальным. Так как минимальный размер 5 мкм, то для ширины и длины канала необходимо взять по 10 мкм.

![]()

Для получения WALH необходимо взять оптимальное соотношение, при котором WA и LH – минимальны:

![]()

Тогда крутизны транзисторов будут следующими:

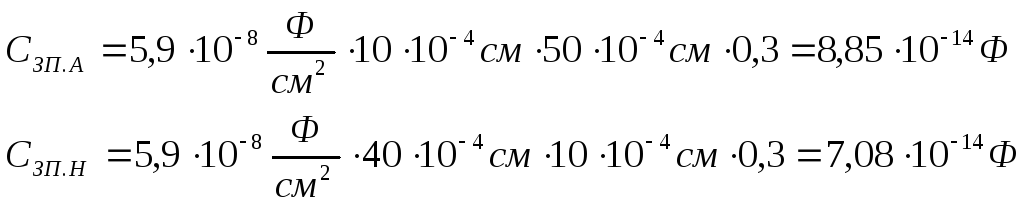

6. Расчет емкостей

1) Найдем емкости перекрытия каналов. Так как область перекрытия со стороны стока и истока одинакова, то и емкости будут одинаковы:

![]() ,где:

,где:

![]() -

удельная емкость подзатворного

диэлектрика

-

удельная емкость подзатворного

диэлектрика

![]() -

ширина области перекрытия

-

ширина области перекрытия

![]() -

длина области перекрытия, равная ширине

канала

-

длина области перекрытия, равная ширине

канала

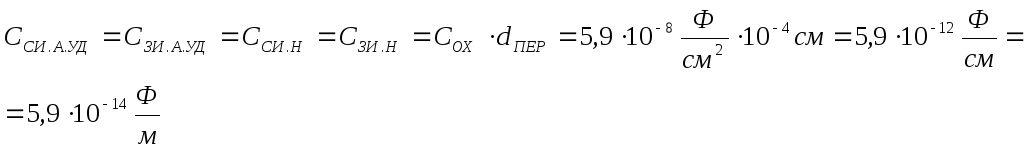

![]()

Аналогично для нагрузочного транзистора:

![]()

Поскольку ряд дальнейших расчетов мы будем выполнять в программе P-Spice, то придется учесть ее специфику и вывести величины удельных емкостей на длину перекрытия, обозначаемые CGSO и CGDO

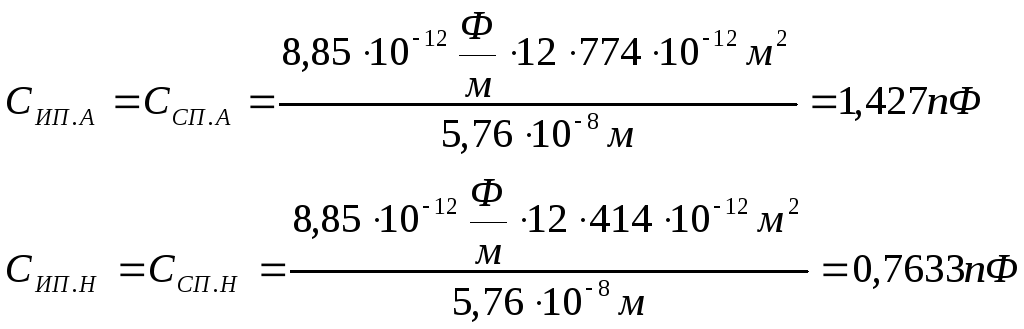

2) Найдем емкости p-n переходов. Емкость p-n перехода исток – подложка и сток – подложка:

![]() ,

где

,

где

![]() -

диэлектрическая проницаемость в вакууме

-

диэлектрическая проницаемость в вакууме

![]() -

диэлектрическая проницаемость кремния

-

диэлектрическая проницаемость кремния

![]() -

площадь донной части перехода сток –

подложка и исток – подложка

-

площадь донной части перехода сток –

подложка и исток – подложка

![]() -

ширина ОПЗ

-

ширина ОПЗ

В соответствии с топологией активного и нагрузочного транзисторов, описанных выше, получим следующие выражения:

![]()

Определим значение WPN из следующего выражения:

![]() ,

где

,

где

![]() -

заряд электрона

-

заряд электрона

![]() -

концентрация имплантированных в канал

ионов

-

концентрация имплантированных в канал

ионов

![]() -

напряжение на p

– n

переходе

-

напряжение на p

– n

переходе

Подставим полученное значение:

Определим емкость затвор – подложка:

![]()

![]()

где η – коэффициент влияния подложки

Суммарная емкость:

![]()

7. Расчеты в P - Spice

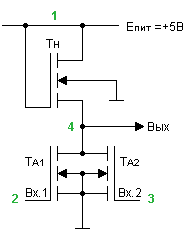

Перед проведением расчетов пронумеруем узлы схемы и обозначим элементы:

Текст программы для получения передаточной характеристики схемы

Kurs n-MOS transistors

Vpit 1 0 5V

Vin1 2 0 0V

Vin2 3 0 0V

MPs 1 1 4 0 nmosn

MA1 4 2 0 0 nmosa

MA2 4 3 0 0 nmosa

MP2 1 1 5 0 nmosn

MA3 5 4 0 0 nmosa

MA4 5 1 0 0 nmosa

.model nmosn nmos(level=3 Vto=0.698 Uo=450 Tox=60n W=10n L=40n CBS=0.7633pF+CBD=0.7633pF CGDO=5.9e-14 CGSO=5.9e-14 lambda=0.05 kp=26.55)

.model nmosa nmos(level=3 Vto=0.698 Uo=450 Tox=60n W=50n L=10n CBS=1.427pF +CBD=1.427pF CGDO=5.9e-14 CGSO=5.9e-14 lambda=0.05 kp=26.55)

.op

.DC Vin1 0 5 0.01

.print DC v(4)

.probe

.end

Текст программы для получения переходной характеристики схемы

Kurs n-MOS transistors

Vpit 1 0 5V

Vin1 2 0 pulse(0.218 5 10u 10u 20u 150u 323u)

Vin2 3 0 0V

MPs 1 1 4 0 nmosn

MA1 4 2 0 0 nmosa

MA2 4 3 0 0 nmosa

C1 4 0 15pF

.model nmosn nmos(level=3 Vto=0.69 Uo=450 Tox=60n W=10n L=40n CBS=0.7633pF+CBD=0.7633pF CGDO=5.9e-12 CGSO=5.9e-12 lambda=0.05 kp=26.55)

.model nmosa nmos(level=3 Vto=0.69 Uo=450 Tox=60n W=50n L=10n CBS=1.427pF+CBD=1.427pF CGDO=5.9e-12 CGSO=5.9e-12 lambda=0.05 kp=26.55)

.op

.tran 0.1u 400u

.print tran v(4) v(2) i(vpit)

.probe

.end

Передаточная характеристика схемы

Уровни логического нуля (U0) и единицы (U1):

(U0) = 0.2V

(U1) = 4.3V

∆Uлог = (U1)- (U0) = 4.1V

(Uc гр) = 2.8V

Помехоустойчивость по положительным и отрицательным помехам

(Uпом +)= (Uc гр) - (U0) = 2.6V

(Uпом -)= (U1) - (Uc гр) = 1.5V

Порог переключения:

(Uп)=( (U0) + (U1))/2 = 2.25V

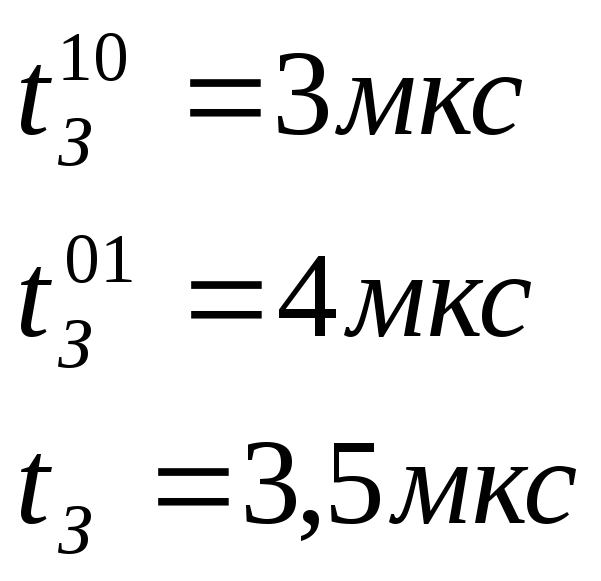

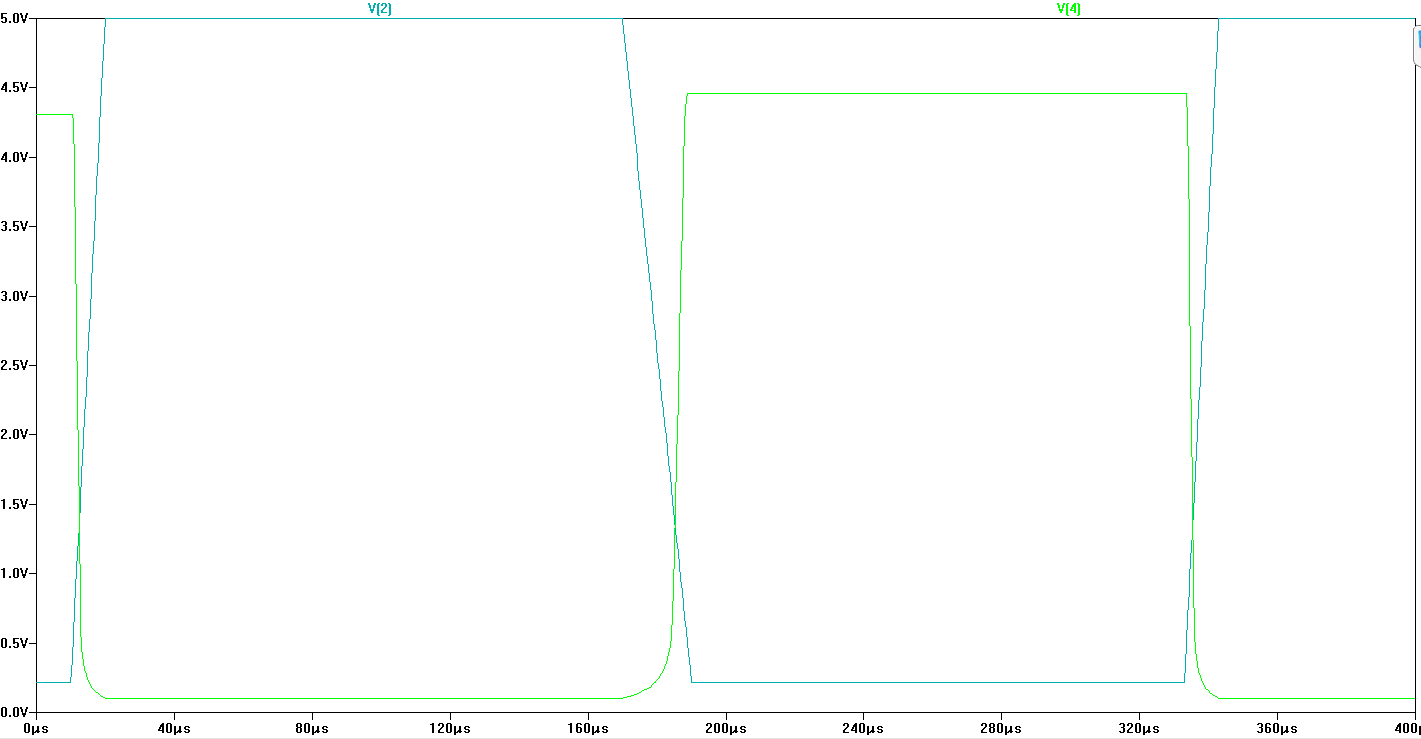

Переходная характеристика схемы

|

|

|

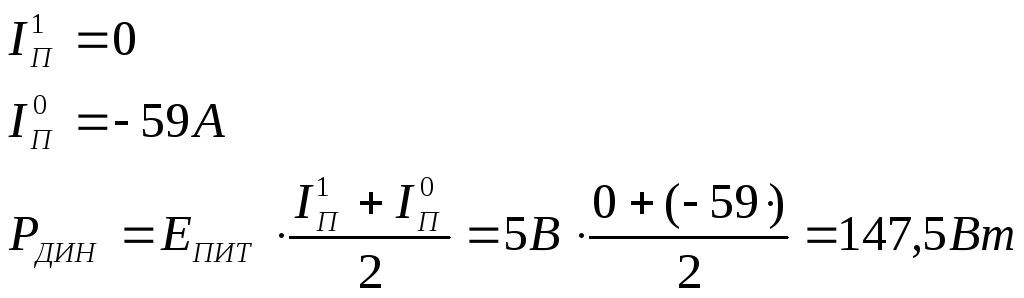

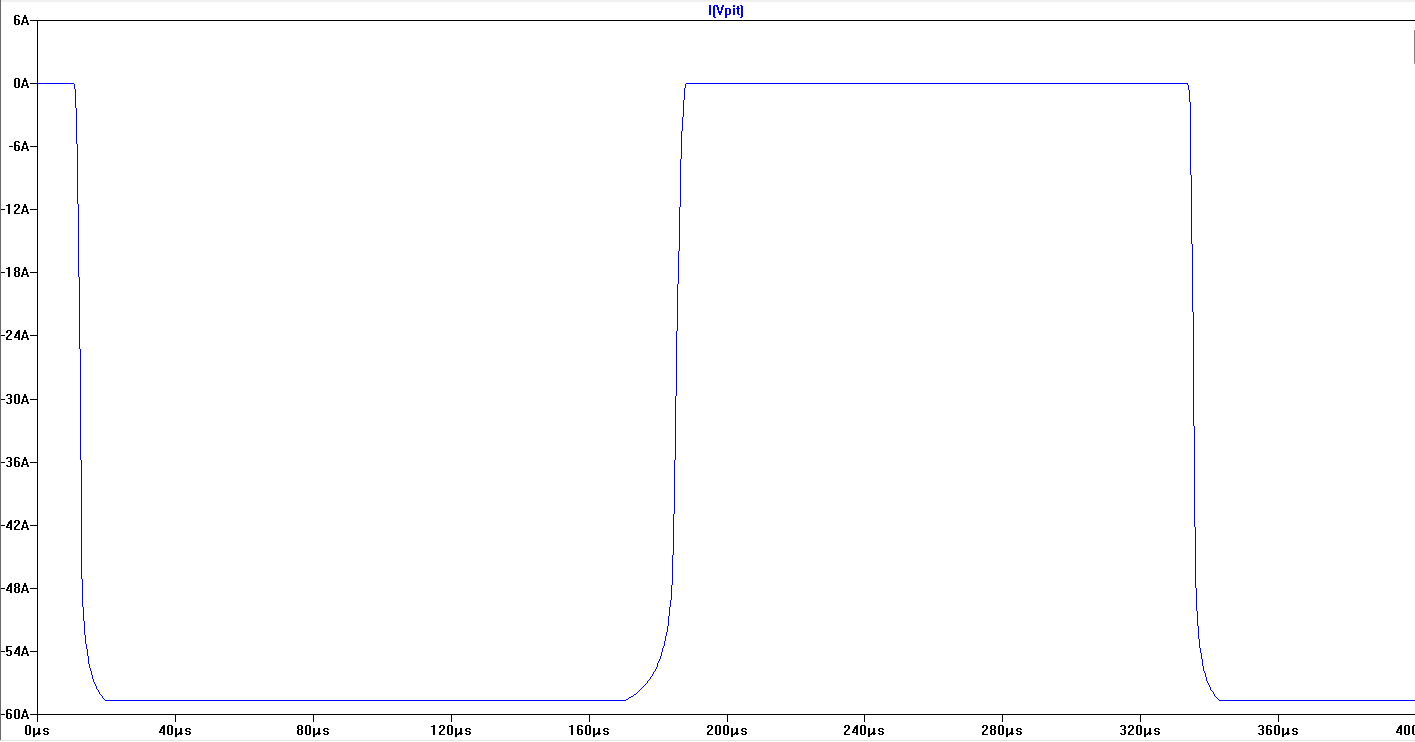

Статическая и динамическая мощности

|

|

|

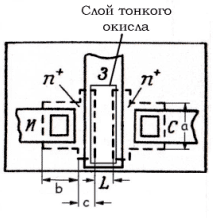

9. Сравнение с аналогами, выпускаемыми промышленностью

Для сравнения использовались цифровые базовые матричные кристаллы на основе n – МОП структур типа К1801ВП1

|

Параметр схемы |

Не менее |

Не более |

Исследуемая схема |

|

Напряжение питания, В |

4,75 |

5,25 |

5 |

|

Напряжение логического нуля, В |

- |

0,4 |

0,2 |

|

Напряжение логической единицы, В |

2,7 |

- |

4,3 |

|

Ток потребления, мкА |

- |

300 |

59 |

|

Максимальная входная частота, кГц |

- |

8 |

3.012 |

|

Среднее время задержки, мкс |

5,5 |

7,5 |

5,2 |