Основы схемотехники. 2011

.pdf

дежную и стабильную работу. Правда, надо учитывать, что триггеры Шмитта имеют несколько большую задержку, чем обычные логические элементы.

Рис. 30 – Формирователь импульса начальной установки по включению питания

Еще одно применение использование триггера Шмитта состоит в построении генераторов импульсов. В отличие от генераторов на обычных инверторах, в данном случае схема получается гораздо проще: достаточно всего лишь одного инвертирующего триггера Шмитта, одного резистора (порядка сотен Ом) и одного конденсатора (рис. 31). При этом очень удобно, что конденсатор одним выводом присоединен к общему проводу, к "земле". Это позволяет применять электролитические конденсаторы большой емкости, а также переменные конденсаторы. Использование двухвходовых триггеров Шмитта дает возможность легко разрешать или запрещать генерацию с помощью управляющего сигнала Разр. При уровне логической единицы на входе Разр. генерация идет, при уровне логического нуля генерации – нет.

Рис. 31 – Управляемый генератор на триггере Шмитта

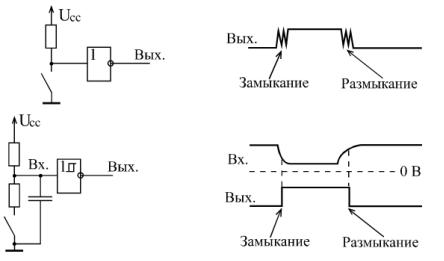

Наконец, последнее применение триггеров Шмитта состоит в подавлении так называемого дребезга контактов. Дело в том, что любой механический контакт (в кнопках, тумблерах, переключателях и т.д.) не замыкается и не размыкается сразу, мгновенно. Любое замыкание и размыкание сопровождается несколькими быстрыми замыканиями и размыканиями, приводящими к появлению паразитных коротких импульсов, которые могут нарушить работу дальнейшей цифровой схемы. Триггер Шмитта с RC-цепочкой на входе позволяет устранить этот эффект

(рис. 32).

Рис. 32 – Триггер Шмитта с RC-цепочкой на входе

Конденсатор заряжается и разряжается довольно медленно, в результате чего короткие импульсы подавляются и не проходят на выход триггера Шмитта. Номинал верхнего по схеме резистора должен в данном случае быть в 6-7 раз больше номинала нижнего, чтобы резистивный делитель при замкнутом тумблере давал на входе триггера Шмитта уровень логического нуля. Сопротивления резисторов должны быть порядка сотен Ом – единиц килоОм. Емкость конденсатора может выбираться в широком диапазоне и зависит от того, какова продолжительность дребезга контактов конкретного тумблера.

ЛЕКЦИЯ 7 КОМБИНАЦИОННЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

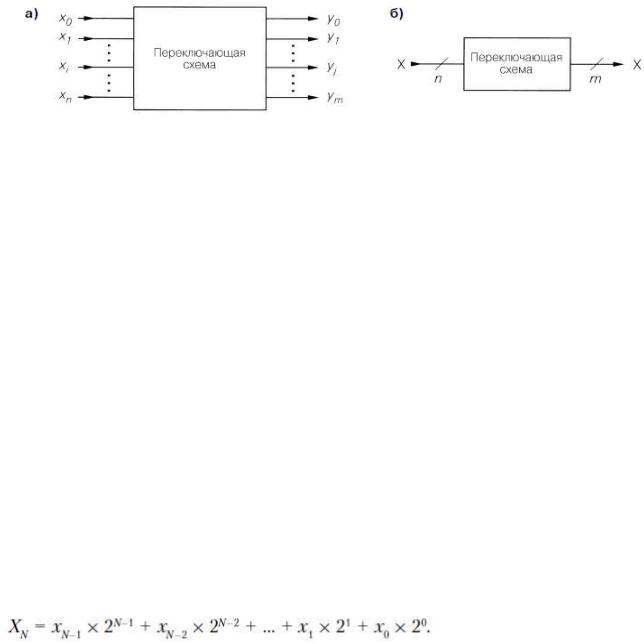

Комбинационной схемой называют структуру из цифровых схем без запоминания данных. Комбинация выходных переменных yj однозначно определяется комбинацией входных переменных xi в соответствии с блок-схемой, приведенной на рис. 1. Входы комбинационных элементов объединены в функциональные группы. Описание комбинационной схемы (элемента), то есть сопоставление выходных переменных входным, осуществляется посредством таблиц истинности или булевых функций. Построение комбинационных схем основано, как правило, на использовании логических элементов, т.е. все комбинационные элементы простроены внутри из простейших логических элементов.

Рис. 1. Диаграмма комбинационной схемы:

а – прохождение сигналов; б – прохождение векторов

Когда число единиц в таблице истинности невелико, невелико и число произведений в логических функциях. Но и при множестве единиц возможны простые логические функции, если в основе лежит высокая упорядоченность. Поэтому всегда следует упрощать логические функции. Делать это вручную с помощью булевой алгебры или таблиц Карно слишком утомительно, поэтому в век компьютерного проектирования интегральных микросхем задача решается программным путем. И лишь после получения нескольких простых функций имеет смысл приступать к составлению комбинационной схемы с использованием отдельных логических элементов.

Обычно комбинационные элементы применяются для пересчета и перекодирования чисел. Чтобы иметь возможность представлять числа посредством логических переменных, сами числа должны отображаться в виде последовательности двоичных чисел, то есть способных принимать только два значения. Будем обозначать строчными буквами логическую переменную, характеризующую отдельное знакоместо в числе, а прописными буквами – все число. Тогда для представления числа из N разрядов в двоичном виде можно записать:

Состав набора комбинационных микросхем, входящих в стандартные серии, был определен исходя из наиболее часто встречающихся задач. Требуемые для этого функции реализованы в комбинационных микросхемах наиболее оптимально, с минимальными задержками и минимальным потреблением мощности.

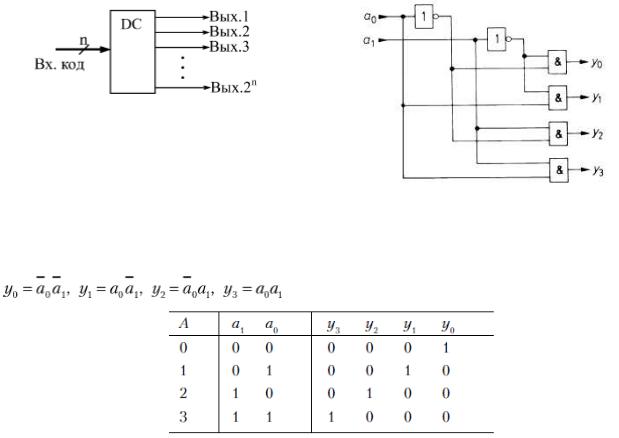

Дешифратор

Дешифратор преобразует входной двоичный код в номер выходного сигнала (дешифрирует код). Количество выходных сигналов дешифратора равно количеству возможных состояний двоичного кода (входного кода у дешифратора), то есть 2n (рис. 2). Дешифратор «один из n» представляет собой схему с n выходами и ln n входами. Другое обозначение дешифратора: ln n – n . Выходы yj нумеруются от 0 до (n – 1). Сигнал на том или ином выходе принимает значение логической единицы, когда двоичное число A на входе равно номеру J соответствующего выхода, т.е. на выходе дешифратора всегда присутствует только один сигнал, причем номер этого сигнала однозначно определяется входным кодом. Таблица истинности для дешифратора «1 из 4» (2–4) приведена в табл. 1. Переменные a0 и a1 служат двоичным кодом числа A. Это позволяет непосредственно считывать дизъюнктивную нормальную форму функций перекодировки. Соответствующая реализация показана на рис. 3.

Рис. 2. Функции дешифратора |

Рис. 3. Схема дешифратора «1 из 4» |

Таблица 1. Таблица истинности дешифратора «1 из 4»

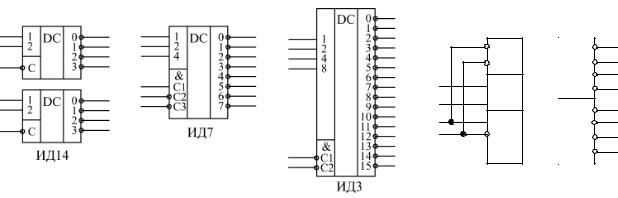

Дешифраторы, выпускаемые в виде отдельных микросхем, имеют буквенное обозначение ИД. На схемах микросхемы дешифраторов обозначаются буквами

DC (от английского Decoder). В сериях ТТЛ, в которых наиболее технологичны элементы И– НЕ, дешифраторы обычно имеют инверсные выходы. В КМОПсериях, где элементы ИЛИ-НЕ не менее технологичны, чем И-НЕ, дешифраторы чаще имеют прямые выходы. Стремление полнее использовать выводы типовых DIP-корпусов определяет размеры дешифраторов, выпускаемых в виде средних интегральных схем (СИС). Обычно это дешифраторы “1 из 8” (3–8), ”1 из 10”, (4– 16) сдвоенный ”1 из 4” (2–4), а также ”1 из 16” (4–16), но уже в корпусе DIP24.

Различаются микросхемы дешифраторов входами управления (разрешения/запрета выходных сигналов), а также типом выхода: 2С или ОК. Входы, на которые поступает входной код, называют часто адресными входами. Обозначают эти входы 1, 2, 4, 8, где число соответствует весу двоичного кода (1 – младший разряд, 2 – следующий разряд и т.д.), или А0, А1, А2, А3. На рис. 4 показаны три наиболее типичных микросхемы дешифраторов. Код на входах 1, 2, 4, 8 определяет номер активного выхода (вход 1 соответствует младшему разряду кода, вход 8 – старшему разряду кода). Входы разрешения С1, С2, С3 объединены по функции И.

Несколько разрешающих входов с разрешающей комбинацией конъюнкции. позволяют наращивать дешифраторы, используя каскадный принцип и строя первый каскад дешифрации не на отдельном специальном дешифраторе, а собирая его из конъюнкторов разрешающих входов. В микросхему К555ИД4 входят два дешифратора ”1 из 4” с общими адресными входами А1 и А0. Каждый дешифратор имеет пару разрешающих входов. У верхнего по схеме (рис. 5) дешифратора два инверсных входа EQ1 и EQ2, у нижнего – один прямой – EP1, и один инверсный – EP2. Это позволяет, объединив EQ1 и EP1 и подав на эту пару третий разряд адреса А2, использовать эту микросхему как дешифратор ”1 из 8”.

|

К555ИД4 |

|

|

|

|

EQ1 DC |

Q0 |

Q0 |

|

|

EQ2 |

Q1 |

Q1 |

|

A0 |

A0 |

Q2 |

Q2 |

|

A1 |

Q3 |

Q3 |

||

A1 |

P0 |

Q4 |

||

A2 |

EP1 |

|||

P1 |

Q5 |

|||

E |

||||

EP2 |

P2 |

Q6 |

||

|

|

P3 |

Q7 |

Рис. 4. Примеры микросхем дешифраторов |

Рис. 5. Использование |

|

разрешающих входов |

|

дешифраторов |

Примеры применения дешифраторов

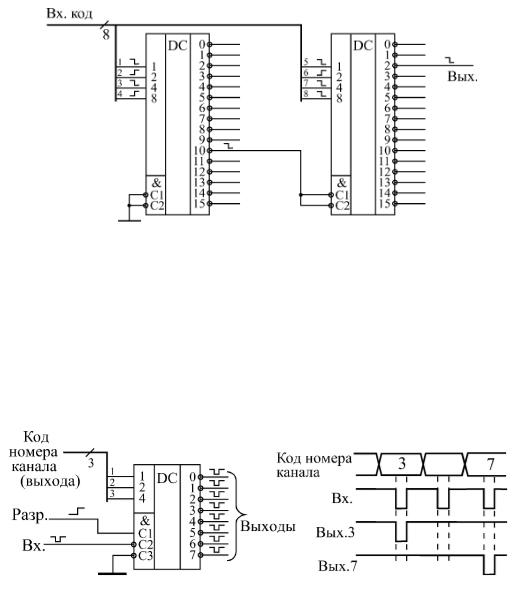

Распространенное применение дешифраторов – селекция (выбор) заданных входных кодов. Появление отрицательного сигнала на выбранном выходе дешиф-

ратора будет означать поступление на вход интересующего нас кода. Две микросхемы 4-16 позволяют селектировать 8-разрядный код (рис. 6). В примере на рисунке селектируется 16-ричный код 2А (двоичный код 0010 1010). При этом один дешифратор работает с младшими четырьмя разрядами кода, а другой – со старшими четырьмя разрядами. Объединяются дешифраторы так, что один из них разрешает работу другого по входам – С1 и – С2. Применяя механические переключатели выходов дешифраторов (тумблеры, перемычки), можно легко изменять код, селектируемый данной схемой.

Рис. 6 – Селектирование кода на дешифраторах

Важное применение дешифраторов состоит в перекоммутации одного входного сигнала на несколько выходов. Дешифратор в данном случае выступает в качестве демультиплексора входных сигналов (рис. 7), который позволяет разделить входные сигналы, приходящие в разные моменты времени, на одну входную линию (мультиплексированные сигналы).

Рис. 7 – Включение дешифратора как демультиплексора

При этом входы 1, 2, 4, 8 дешифратора используются в качестве управляющих, адресных, определяющих, на какой выход переслать пришедший в данный момент входной сигнал, а один из входов С выступает в роли входного сигнала, который пересылается на заданный выход. Если у микросхемы имеется несколько стробирующих входов С, то оставшиеся входы С можно использовать в качестве разрешающих работу дешифратора.

Как и для любых других цифровых микросхем, для дешифраторов наиболее критична ситуация одновременного или почти одновременного изменения входных сигналов. Например, если стробы С постоянно разрешают работу дешифратора, то в момент изменения входного кода на любом выходе дешифратора могут появиться паразитные отрицательные короткие импульсы. Это может быть связано как с неодновременным выставлением разрядов кода (из-за несовершенства микросхем источников кода или из-за разных задержек распространения по линиям связи), так и с внутренними задержками самих микросхем дешифраторов.

Если такие паразитные импульсы нужно исключить, то можно применять синхронизацию с помощью стробирующих сигналов. Используемый для этого сигнал С должен начинаться после текущего изменения кода, а заканчиваться до следующего изменения кода, то есть должен быть реализован вложенный цикл. На рис. 8 показано, как будет выглядеть выходной сигнал дешифратора без стробирования и со стробированием.

Рис. 8 – Стробирование выходных сигналов дешифратора

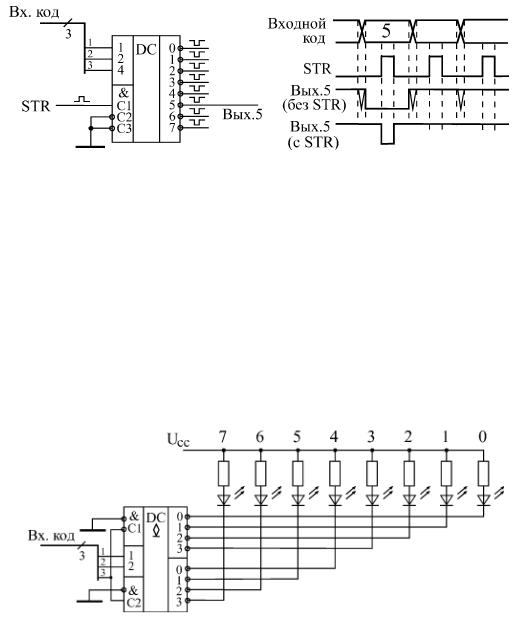

Дешифраторы, имеющие выходы типа ОК, удобно применять в схемах позиционной индикации на светодиодах. На рис. 9 приведен пример такой индикации на микросхеме ИД5, которая представляет собой два дешифратора 2–4 с объединенными входами для подачи кода и стробами, позволяющими легко строить дешифратор 3–8. При этом старший разряд кода выбирает один из дешифраторов 2–4 ( нуль соответствует верхнему по схеме дешифратору, а единица – нижнему). То есть в данном случае номер горящего светодиода равен входному коду дешифратора. Такая индикация называется позиционной.

Рис. 9 – Позиционная индикация на дешифраторе с выходами ОК

Шифратор

Шифратор преобразует номер входного сигнала в выходной двоичный код (шифрует номер входного сигнала). Количество входных сигналов шифратора равно количеству возможных состояний двоичного кода (выходного кода у шифратора), то есть 2n, где n – разрядность двоичного кода (рис. 10). Микросхемы шифраторов обозначаются на схемах буквами – CD ( от английского Coder).

Рис. 10. Функции шифратора

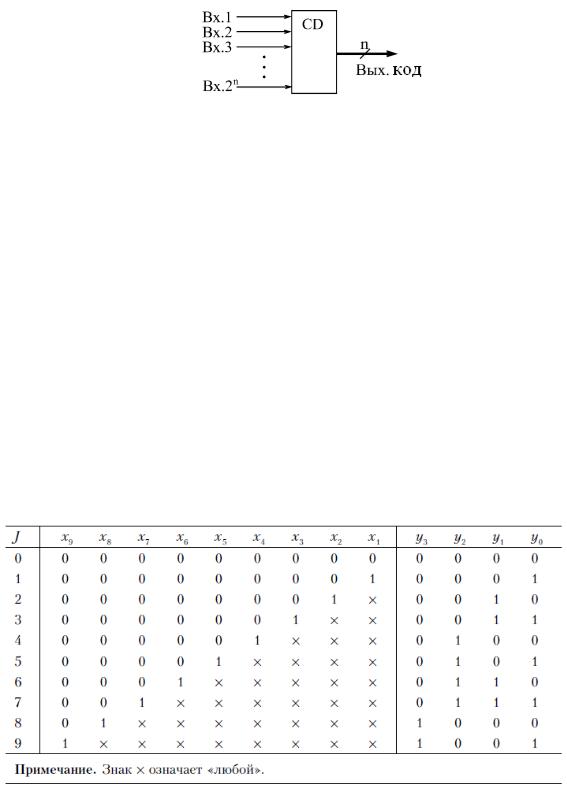

Выходной код шифратора однозначно определяется номером входного сигнала. Шифратор применяется для преобразования кода «один из n» в двоичный код. На его выходах появляется двоичное число, соответствующее наибольшему номеру входа, на который подан сигнал, при этом значение входной переменной не играет роли. На выходах кода 1, 2, 4 формируется двоичный код номера входной линии, на который приходит отрицательный входной сигнал. При одновременном поступлении нескольких входных сигналов формируется выходной код, соответствующий входу с наибольшим номером, то есть старшие входы имеют приоритет перед младшими. Поэтому такой шифратор называется приоритетным. Данное свойство схемы позволяет преобразовывать не только код «один из n», но и код с суммированием, когда единица занимает не один, а все более младшие разряды. Таблица истинности приоритетного дешифратора представлена в табл. 2.

Таблица. 2. Таблица истинности приоритетного дешифратора

На рис. 11 показаны для примера две микросхемы шифраторов ИВ1 и ИВ3. Первая имеет 8 входов и 3 выхода (шифратор 8–3), а вторая – 9 входов и 4 выхода (шифратор 9–4). Все входы шифраторов – инверсные (активные входные сигналы

– нулевые). Все выходы тоже инверсные, то есть формируется инверсный код. Микросхема ИВ1, помимо 8 информационных входов и 3 разрядов выходного кода (1, 2, 4), имеет инверсный вход разрешения -ЕI, выход признака прихода любого входного сигнала -GS, а также выход переноса -EO, позволяющий объединять несколько шифраторов для увеличения разрядности.

Рис. 11. Микросхемы шифраторов

Демультиплексор

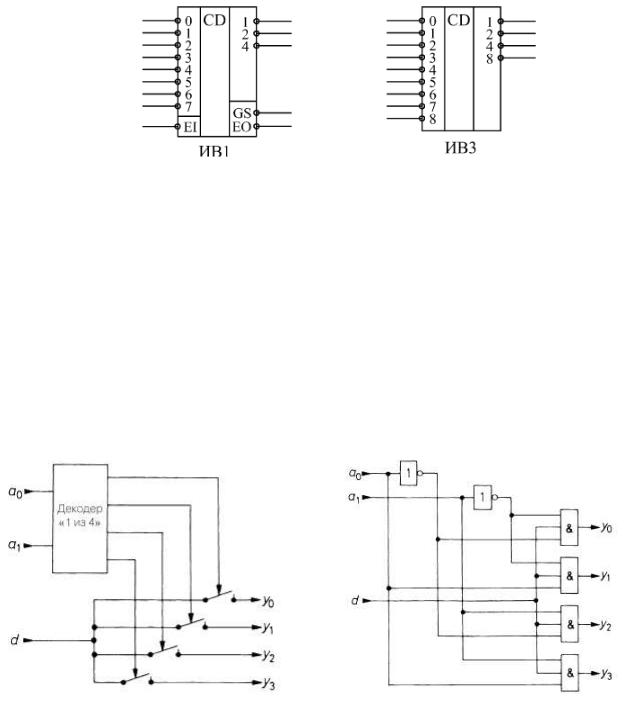

Демультиплексор позволяет направлять входную информацию d на различные выходы и представляет собой расширение дешифратора «один из n». Он распределяет данные по множеству выходов в соответствии с принятой адресацией, т.е. адресуемому выходу присваивается не единица, а значение входной переменной d. На рис. 12 показан принцип действия на примере схемы с ключами, а на рис. 13 демонстрируется реализация с помощью логических элементов. При d = const = 1 демультиплексор функционирует как дешифратор «один из n».

Рис. 12. Принцип действия |

Рис. 13. Схема демультиплексора |

демультиплексора |

|

Мультиплексор

Мультиплексором называют схему, которая подключает любой из множества источников данных к единственному выходу, причем выбор источника определяется его адресом. Мультиплексором называется устройство с функциями, обратными демультиплексору.

Следуя принципу действия схемы, показанной на рис. 12, для реализации мультиплексора достаточно поменять местами выходы с входами. Результат такой замены показан на принципиальной схеме (рис. 14), доступно объясняющей функционирование мультиплексора: дешифратор «один из n» выбирает из n входов тот, чей номер совпадает с заданным числом, и подключает его к выходу. Соответствующая реализация с помощью логических элементов показана на рис. 15.

Рис. 14. Принцип действия |

Рис. 15. Схема мультиплексора; |

мультиплексора |

|

В КМОП технологии мультиплексоры реализуются как на логических элементах, так и на аналоговых ключах (передаточных вентилях). Последние обеспечивают двунаправленную передачу сигнала, так что мультиплексор и демультиплексор становятся неразличимыми (ср. рис. 12 и 14). В этом случае схему называют аналоговым мультиплексором/демультиплексором.

Управление работой мультиплексора (выбор номера канала) осуществляется с помощью входного кода адреса. Например, для 4-канального мультиплексора необходим 2-разрядный управляющий (адресный) код, а для 16-канального – 4- разрядный код. Разряды кода обозначаются 1, 2, 4, 8 или А0, А1, А2, А3. Мультиплексоры бывают с выходом 2С и с выходом 3С. Выходы мультиплексоров бывают прямыми и инверсными. Выход 3С позволяет объединять выходы мультиплексоров с выходами других микросхем, а также получать двунаправленные и мультиплексированные линии. Некоторые микросхемы мультиплексоров имеют вход разрешения/запрета С (другое обозначение – S), который при запрете устанавливает прямой выход в нулевой уровень. На рис. 16 показаны для примера не-