Основы схемотехники. 2011

.pdf

Таким образом, в зависимости от выбора логики одна и та же схема может служить логическим элементом ИЛИ-НЕ либо И-НЕ. Как правило, логические схемы задаются в позитивной логике. С переходом к негативной логике происходит смена функций:

Впроизводстве цифровых интегральных схем (ИС) выделяют два технологических направления:

- технология биполярных транзисторных структур;

– технология униполярных транзисторных структур.

Втехнологии биполярных транзисторных структур применяются в основном транзисторы типа n-p-n, что объясняется их большим быстродействием по сравнению с транзисторами типа p-n-p. В транзисторах типа n-p-n напряжение питания Uп >0, следовательно, применяется положительная логика.

Втехнологии униполярных транзисторных структур используются полевые транзисторы структуры МДП (металл-диэлектрик-полупроводник) с индуцированным каналом проводимости. Канал образуется (индуцируется) благодаря притоку электронов (канал-n типа) или дырок (канал-p типа). В качестве диэлектрика

восновном применяется окисел кремния. Отсюда другое название структуры – МОП. Основным недостатком ИС на МОП транзисторах является меньшее быстродействие. По сравнению с микросхемами на биполярных транзисторах ИС на МОП транзисторах имеют следующие преимущества:

– более высокая нагрузочная способность;

– меньшая потребляемая мощность;

– меньшая стоимость изготовления;

– более высокая степень интеграции за счет меньшей площади МОП транзистора.

Основой каждой серии цифровых ИС является базовый логический элемент, выполняющий операцию НЕ, И-НЕ либо ИЛИ-НЕ.

Системы потенциальных элементов технологии биполярных транзисторных структур

Резисторно-транзисторная логика

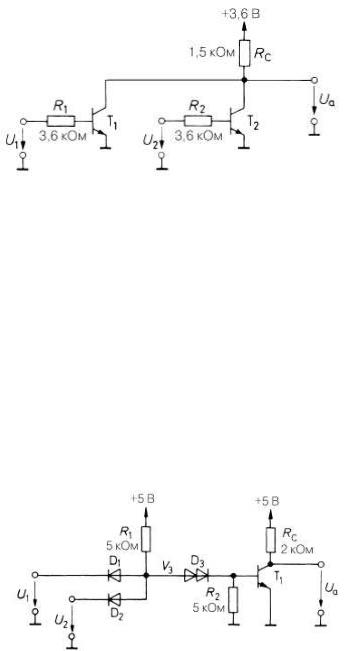

Элементы резисторно-транзисторной логики (РТЛ) представляют собой вариант переключающих схем на транзисторах в режиме насыщения. Если в элементе РТЛ на рис. 1 входное напряжение отвечает высокому уровню, соответствующий транзистор открыт, а на выходе образуется низкий уровень. В таких условиях при положительной логике реализуется функция ИЛИ-НЕ. Сравнительно низкоом-

ные резисторы в цепи базы гарантируют проводимость транзистора даже при небольшом усилении по току. Однако отсюда следует низкий коэффициент разветвления по выходу. В настоящее время элементы РТЛ вышли из употребления.

Рис. 1. Логический элемент РТЛ ИЛИ-НЕ типа MC717

Диодно-транзисторная логика

В схеме диодно-транзисторной логики (ДТЛ) на рис. 2 ток базы выходного транзистора протекает через резистор R1 при запертых входных диодах D1 и D2, то есть, когда все входные напряжения находятся в состоянии H, транзистор T1 открыт и выходное напряжение находится на уровне L. Таким образом, если выбрана положительная логика, реализуется функция И-НЕ. Если к выходу подключить аналогичный логический элемент И-НЕ, нагрузка выхода в состоянии H останется прежней. Поэтому уровень H выходного напряжения равен напряжению питания V+. Схемы ДТЛ в настоящее время не находят применения из-за недостаточного быстродействия, обусловленного насыщением транзисторов.

Рис. 2. Логический элемент ДТЛ И-НЕ типа MC849

Медленнодействующая помехоустойчивая логика

Элементы данного типа используются в приборах, где возможны значительные импульсные помехи, и представляют собой модифицированные схемы ДТЛ, у которых сдвоенный диод D3 заменен стабилитроном (рис. 3). В результате уровень переключения по входу поднят до 6 В, и при напряжении питания 12 В запас помехоустойчивости достигает 5 В.

Чтобы повысить коэффициент разветвления по выходу, элементы медленнодействующей помехоустойчивой логики (МПЛ) снабжаются двухтактным око-

нечным каскадом. Транзисторы, обладающие малым быстродействием, позволяют искусственно увеличить время переключения, а применение внешних конденсаторов делает его еще большим. Благодаря этому короткие импульсы помех не страшны даже тогда, когда их амплитуда превышает запас помехоустойчивости. Элементы МПЛ называют также схемами с высоким логическим уровнем.

Рис. 3. Логический элемент МПЛ И-НЕ

Транзисторно-транзисторная логика

Принцип действия схем ТТЛ аналогичен работе схем ДТЛ, а сами схемы различаются только диодными элементами и усилителем. У стандартной схемы ТТЛ (рис. 4) диодный элемент заменен транзистором T1 с несколькими эмиттерами. Когда все входные уровни отвечают состоянию H, ток через резистор R1 протекает по открытому в прямом направлении переходу база-коллектор входного транзистора в цепь базы транзистора T2 и переводит его в открытое состояние.

Рис. 4. Стандартный логический элемент ТТЛ И-НЕ типа SN7400 (K155)

Если на один из входов подан низкий потенциал, соответствующий переход база-эмиттер открывается и потенциал базы T2 оказывается близким к нулю, вследствие чего T2 запирается, а выходное напряжение соответствует состоянию H.

В схемах ТТЛ усилитель состоит из управляющего транзистора T2 и двухтактного оконечного каскада. Когда T2 открыт, T3 также открыт, а T4 заперт. На выходе возникает сигнал уровня L, и транзистор T3 приобретает способность пропускать большие токи, например, от подключенных входов логических эле-

ментов (в состоянии L ток вытекает из этих входов). T3 запирается вместе с T2, но при этом открывается T4, что приводит к появлению уровня H на выходе. В таком случае транзистор в режиме эмиттерного повторителя может создавать в нагрузке большие выходные токи и, следовательно, быстро заряжать емкости нагрузки. Стандартные схемы ТТЛ (рис. 4) в настоящее время не находят применения из-за недостаточного быстродействия, обусловленного насыщением транзисторов.

Включение диода Шоттки параллельно переходу коллектор-база (рис. 5) предотвращает насыщение транзистора. При открытом транзисторе благодаря обратной связи по напряжению диод не позволяет напряжению коллектор-эмиттер упасть ниже 0,3 В.

Рис. 5. Транзистор с диодом Шоттки для устранения насыщения и соответствующее схемное обозначение

На рис. 6 показан логический элемент ТТЛ, который построен из подобных «транзисторов Шоттки», представляющих собой маломощный ТТЛ элемент с диодами Шоттки. Номиналы резисторов схемы выбираются впятеро более высокоомными по сравнению со схемой стандартного логического элемента ТТЛ, благодаря чему потребляемая мощность снижается во столько же раз и достигает всего 2 мВт.

Рис. 6. Маломощный логический элемент ТТЛ с диодом Шоттки типа 74LS00

При этом быстродействие элемента не ухудшается, оставаясь равным 10 нс. Подобно схемам ДТЛ, диодный входной логический элемент строится на раздельных диодах. Транзистор Дарлингтона T3 заменяет здесь диод D в оконечном каскаде, необходимый для смещения потенциала в стандартной схеме (см. рис. 4).

Выходы с открытым коллектором

Иногда требуется логически соединять выходы многих элементов. Например, для 20 выходов потребовалось бы проложить 20 проводов к элементу с 20 входами. Использование элементов с открытым коллектором позволяет обойти эту трудность. У подобного элемента выходным каскадом служит n-p-n транзистор, эмиттер которого соединен с землей (рис. 7). В отличие от обычных двухтактных выходных каскадов такие выходы можно соединять параллельно друг другу и подключать к общему коллекторному резистору.

Рис. 7. Реализация логической функции путем соединения выходов элементов с открытым коллектором

Выходное напряжение принимает значение, соответствующее состоянию H, только в том случае, когда все выходы оказываются в состоянии H. В позитивной логике это равнозначно функции И. Вместе с тем выходное напряжение соответствует низкому уровню L, когда один или несколько выходов оказываются в состоянии L. Так реализуется функция ИЛИ в отрицательной логике. Поскольку подключения осуществляются с помощью внешнего монтажа, такие соединения называют «монтажным» И и «монтажным» ИЛИ. Выходы элементов характеризуются низким выходным сопротивлением только в состоянии L (логический нуль), поэтому их называют также схемами с низкоомным выходным активным нулем. Представление «монтажного» И с помощью условных обозначений показано на рис. 8.

Рис. 8. Условные обозначения «монтажной» функции И. Символ в виде подчеркнутого ромба означает выход с открытым коллектором

Выходы с открытым коллектором позволяют также реализовать функцию ИЛИ, если «монтажное» И применить к инвертированным переменным. Согласно теореме Де Моргана имеет место:

Соответствующая схема приведена на рис. 9.

Рис. 9. Функция ИЛИ, реализованная посредством выходов с общим коллектором

Недостаток применения выходов с открытым коллектором заключается в более медленном нарастании выходного напряжения по сравнению с двухтактным выходом, так как паразитные емкости могут заряжаться только через резистор RC. В этом отношении элементы ТТЛ с открытым коллектором сходны со схемами РТЛ (см. рис. 1), в которых логическая функция может интерпретироваться как «монтажное» И.

Трехстабильные выходы

Имеется еще одно важное применение параллельного включения выходов логических элементов, когда один из нескольких элементов по выбору должен определять логическое состояние сигнального проводника. В таком случае говорят о системе с шинной организацией.

Проблема решается также посредством элементов с открытым коллектором (см. рис. 8), если все выходы переводятся в высокоомное состояние H. Здесь удается обойти принципиальный недостаток медленного нарастания сигнала, применив элементы не с открытым коллектором, а с трехстабильным выходом. Это схема с двухтактным выходом, отличающимся тем, что он может переводиться в состояние с высоким выходным сопротивлением при помощи специального управляющего сигнала. Описанное состояние называют состоянием Z.

Принцип схемотехнической реализации показан на рис. 10, а условное обозначение на рис. 11. Когда разрешающий сигнал EN = 1, схема работает как обычный инвертор: при x = 0 имеем z1 = 0 и z2 = 1, то есть T1 заперт, а T2 открыт. При x = 1 T1 открыт, а T2 заперт. Но если управляющая переменная EN = 0, z1 = z2 = 0, так что оба выходных транзистора заперты, получаем состояние Z с высоким выходным сопротивлением.

Рис. 10. Инвертор с трехстабильным выходом

Рис. 11. Условное обозначение инвертора с трехстабильным выходом

Самое многочисленное семейство логических элементов образуют маломощные схемы ТТЛ с диодом Шоттки, отличающиеся высокими электрическими параметрами, разнообразием типов и дешевизной.

Эмиттерно-связанная логика

В дифференциальном усилителе ток Ik переключается между транзисторами при разности входных напряжений около ±100 мВ, следовательно, усилитель обладает двумя определенными коммутируемыми состояниями IC = Ik и IC = 0, что позволяет называть его переключателем тока. Если задать параметры схемы так, чтобы напряжение на коллекторном резисторе в процессе переключений изменялось незначительно, можно воспрепятствовать переходу открытого транзистора в состояние насыщения.

Схема типичного элемента ЭСЛ представлена на рис. 12. Дифференциальный усилитель образован транзисторами T2 и T3. К базе T3 через делитель напряжения R3, R4 приложен постоянный потенциал Vref. Когда напряжения на всех входах отвечают состоянию L, транзисторы T1 и T2 заперты и ток эмиттера течет через транзистор T3, вызывая падение напряжения на резисторе R2. Благодаря этому выходное напряжение Ua1 соответствует состоянию L, а Ua2 – состоянию H. Как только уровень хотя бы одного из входных сигналов перейдет в состояние H, произойдет перемена состояний выходов. В положительной логике для выхода Ua1 здесь реализуется функция ИЛИ, а для выхода Ua2 – функция ИЛИ-НЕ.

Теперь рассмотрим распределение потенциалов в схеме. При наименьшем входном уровне H = -1,1 В уровень L на выходе должен составлять не более -1,65 В. В отличие от остальных типов логических схем, входное напряжение в состоянии H сильно ограничено сверху и не должно превышать -0,8 В, в противном случае происходит насыщение соответствующего входного транзистора.

Рис. 12. Логический ЭСЛ элемент ИЛИ-ИЛИ-НЕ типа MC10102. В интегральной микросхеме нет эмиттерных резисторов R5 и R6, они подключаются извне.

Схемам ЭСЛ свойственно максимальное быстродействие (минимальное время переключения) среди всех логических схем. По данному параметру они превосходят схемы ТТЛ с диодами Шоттки, функционирующие также без перехода в режим насыщения. Различие между ними состоит в более высоком напряжении на участке коллектор-эмиттер у открытых транзисторов в схемах ЭСЛ, которое никогда не превышает 0,6 В. Это не только увеличивает запас по напряжению до перехода в насыщение, но и снижает барьерную емкость перехода коллектор-база. Амплитуда сигналов, при которых происходит переключение, мала и не превышает 0,8 В, что также улучшает быстродействие схем типа ЭСЛ, так как ускоряет перезаряд неизбежных паразитных емкостей. Сокращению времени переключения способствует низкое выходное сопротивление эмиттерного повторителя.

За хорошее быстродействие схем типа ЭСЛ приходится расплачиваться высокой потребляемой мощностью: у одиночного логического элемента серии MC 10000 она достигает 25 мВт. В заключение перечислим доводы в пользу применения логических элементов типа ЭСЛ в быстродействующих логических схемах:

•они обладают самым малым временем переключения;

•потребляемый ими ток не зависит от состояния схемы;

•переключение не сопровождается выбросами тока, благодаря чему высокочастотная составляющая почти не портит электропитание;

•симметричность выходов обеспечивает помехозащищенность передачи сигналов даже на протяженных линиях.

Системы потенциальных элементов технологии униполярных транзисторных структур

Комплементарная МОП логика

Семейство логических схем типа КМОП отличается особой экономичностью по электропитанию. Схема КМОП инвертора приведена на рис. 13. Она образована исключительно МОП транзисторами с индуцированным каналом. При

этом истоковые выводы n-канального МОП транзистора соединены с землей, а p- канального – с источником напряжения питания VDD. Таким образом, оба МОП транзистора функционируют в схеме с общим истоком, усиливают и инвертируют входное напряжение, причем в каждый момент времени один из них играет роль рабочего нагрузочного резистора для другого.

Рис. 13. КМОП инвертор

Модуль порогового напряжения обоих МОП транзисторов составляет около 1,5 В, поэтому при напряжении питания 5 В по крайней мере один из них открыт. При Ue = 0 открыт p-канальный МОП транзистор T2, а n-канальный T1 закрыт. Выходное напряжение становится равным VDD. При Ue = VDD закрыт T2, а T1 открыт и выходное напряжение принимает нулевое значение. Ясно, что в стационарных условиях ток через схему не идет. Слабый сквозной ток протекает только при переключении, пока входное напряжение находится в пределах |Up| < Ue < VDD – | Up|.

Логические уровни зависят от выбора напряжения питания. Диапазон допустимого напряжения питания КМОП приборов весьма широк. У схем с кремниевым затвором он лежит между 3 и 6 В, а у схем с металлическим затвором простирается от 3 до 15 В. По соображениям симметрии порог переключения всегда выбирают равным половине напряжения питания. Поэтому при питающем напряжении 5 В уровень H должен быть выше 3,5 В. По указанной причине для управления КМОП элементом с помощью ТТЛ выхода требуется дополнительный резистор установки рабочей точки. Зато полностью совместимы с ТТЛ элементами схемы типа HCT, на входе которых имеется специальный преобразователь уровня.

Потребление тока КМОП элементом складывается из трех составляющих:

•при постоянном входном напряжении, равном нулю или VDD, протекает слабый обратный ток величиной несколько микроампер;

•при смене состояния входного сигнала через оба транзистора течет преимущественно сквозной ток;

•основная составляющая появляется при заряде и разряде транзисторных емкостей Cr.

Выводы затвора МОП транзисторов крайне чувствительны к статическим зарядам. Во избежание повреждений входы интегральных МОП схем защищаются диодами (рис. 14).

Рис. 14. Входная защита схемы

Логические КМОП элементы

На рис. 15 представлен КМОП элемент ИЛИ-НЕ, функционирующий по тому же принципу, что и описанный инвертор. Чтобы сделать управляемый резистор высокоомным при переходе одного из входных напряжений в состояние H, требуется последовательная цепочка из соответствующего числа p-канальных полевых транзисторов. Заменяя последовательную цепочку параллельной, вместо логического элемента ИЛИ-НЕ получают элемент И-НЕ (рис. 16).

Рис. 15. КМОП элемент ИЛИ-НЕ |

Рис. 16. КМОП элемент И-НЕ |

Логический ключ

На рис. 17 представлена схемотехническая реализация ключа в КМОП технологии. Собственно ключ образован парой комплементарных МОП транзисторов T1 и T2. Управление осуществляется с помощью инвертора с комплементарными потенциалами затвора.

Рис. 17. Устройство логического ключа

При UST = 0 имеет место VGN = 0 и VGP = VDD; здесь оба МОП транзистора заперты, если напряжения сигнала U1 и U2 лежат в интервале от 0 до VDD. Если, на-