Основы схемотехники. 2011

.pdf

Код Хэмминга

Принцип кода Хэмминга состоит в том, чтобы с помощью нескольких контрольных разрядов не только распознавать, но и локализовать отдельные ошибки. Локализация ошибочного двоичного разряда позволяет исправлять его путем инвертирования.

Ответ на вопрос о количестве необходимых контрольных битов достаточно прост: k контрольных разрядов позволяют задавать 2k различных комбинаций. При m информационных разрядах общая длина слова составит m + k. Дополнительная контрольная комбинация требуется для проверки правильности принятого слова. Отсюда следует условие: 2k ≥m + k + 1.

Практически важные решения приведены в табл. 1. Таблица определяет количество контрольных разрядов, минимально необходимых для опознания и исправления одиночной ошибки, в зависимости от длины информационного слова

Таблица 1.

Поясним определение контрольных разрядов на примере 16-разрядного числа. Согласно табл. 1, для защиты 16 разрядов требуется пять контрольных бит, так что общая длина слова составит 21 бит. В коде Хэмминга отдельные контрольные биты рассчитываются в виде битов четности для разных частей информационного слова. Следовательно, потребуется пять генераторов четности. Их выводы распределяются по информационным битам так, чтобы каждый из них был подключен, по крайней мере, к двум из пяти генераторов. Если теперь один из информационных битов окажется переданным неверно, отличие появится именно в том бите четности, который связан с ошибочным разрядом.

При таком методе вместо сигнала об ошибке четности f получим 5- разрядный код ошибки (синдром), способный принимать 32 различных значения, что позволяет сделать вывод об ошибочном разряде. Заключение об одиночной ошибке признается однозначным, когда каждому разряду соответствует своя комбинация подключений. Если различие обнаруживается лишь в одном разряде четности, то неправильным может быть только данный разряд, так как при выбранной схеме подключения ошибка в информационном разряде должна приводить к изменению минимум двух контрольных разрядов четности. Если все информационные и контрольные разряды четности считаны без ошибок, то вычисленные разряды четности совпадают с разрядами в памяти, и синдром F = 0.

Особое достоинство ЗУ с коррекцией ошибок заключается в возможности несложной регистрации появляющихся ошибок памяти благодаря процедуре коррекции. Но чтобы сполна воспользоваться такими преимуществами, важно учесть ряд аспектов, стараясь свести к минимуму вероятность множественных ошибок, не подлежащих исправлению. По этой причине следует применять отдельную микросхему памяти для каждого информационного и контрольного разрядов.

В противном случае при выходе из строя элемента памяти будет повреждено множество разрядов. Кроме того, необходимо как можно быстрее устранять выявленные ошибки. Поэтому в случае обнаружения ошибки в ОЗУ компьютера текущая программа прерывается и вызывается программа обработки ошибок. Прежде всего, нужно выяснить, является ли ошибка случайной, устраняемой путем повторной записи в память и считывания исправленного информационного слова. Если таким способом ошибка не устраняется, она считается постоянной. В подобной ситуации считывается синдром, позволяющий локализовать затронутые сбоем микросхемы памяти, и их номера вместе со всеми неисправностями заносятся в таблицу. Регулярный опрос таблиц помогает своевременно заменять дефектные элементы. Данный способ повышает надежность памяти с помощью сис-

темы выявления и исправления ошибок EDC (Error Detection and Correction).

ЛЕКЦИЯ 13 ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ УСТРОЙСТВА

Программируемые логические устройства (ПЛУ) служат для хранения логических функций. Различают три варианта таких устройств (лк. 10): программируемая логическая матрица (ПЛМ), программируемая матричная логика (ПМЛ) и программируемый логический элемент (ПЛЭ), различающиеся гибкостью программирования. Проще всех программируются ПЛМ, поэтому они особенно популярны и выпускаются во множестве версий. ПМЛ более гибки, но их сложнее программировать; в настоящее время они утратили практическое значение. Вентильные матрицы с программированием в процессе эксплуатации, или матричные БИС FPGA (Field Programmable Gate Arrays), позволяют запрограммировать не только логические функции, но и любые пути передачи данных между блоками функций.

Для наглядного представления логических операций пользуются графическими средствами, показанными на рис. 1. Перекрестие на рисунке указывает на подключение того или иного входа. Неподключенный вход не оказывает никакого влияния, так как в операции И его состояние соответствует единице, а в операции ИЛИ отображается нулем.

Рис. 1. Сокращенное представление логических операций И и ИЛИ

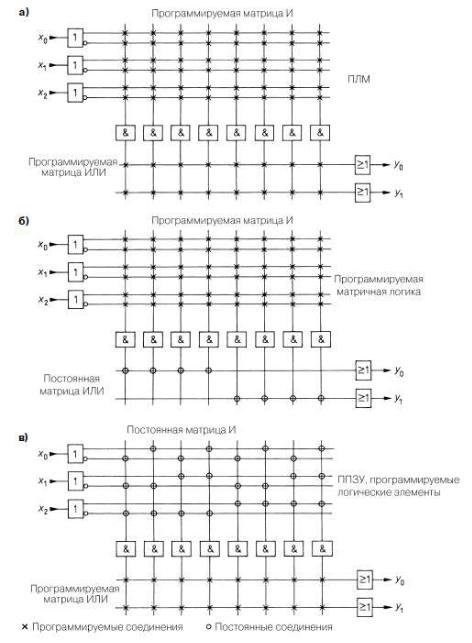

Представим внутреннее устройство ПМЛ и ПЛМ (рис. 2). Входные переменные вместе со своими отрицаниями с помощью пересекающихся входов логических элементов И образуют матрицу, которая позволяет выполнять все требуемые логические перемножения.

Тогда в соответствующей второй матрице могут быть образованы связи элементов И и ИЛИ с выходами для формирования необходимых функций логического сложения (дизъюнкции). Для этого нужен лишь один элемент ИЛИ на каждую выходную переменную. В случае ПЛМ (рис. 2а) обе матрицы программируются пользователем. В ПМЛ (рис. 2б) матрица ИЛИ задается изготовителем, так что пользователь программирует только матрицу И.

ППЗУ можно представить как устройство хранения функций, если дешифратор адресов интерпретировать как матрицу И. Тогда приходим к структуре, представленной на рис. 2в. По каждому из адресов значение 1 принимается только одной функцией И, причем именно той, которая соответствует указанному ад-

ресу. Следовательно, здесь имеют место n = 2N логических перемножений (конъюнкций), тогда как ПЛМ и ПМЛ располагают гораздо меньшими возможностями. Примет соответствующая функция значение 1 или 0, определяется тем, как запрограммирована матрица ИЛИ.

Рис. 2. Сравнение внутренней структуры ПЛМ, ПМЛ и ППЗУ

Программируемые ПЗУ, предназначенные для реализации логических функций, называются также программируемыми логическими элементами (ПЛЭ). Различия приведены в табл. 1. Здесь требуется отменить программирование всех связей, которые не нужны для этих функций. Из рис. 3 видно, что в матрице И устройств ПЛМ и ПМЛ образованы все необходимые конъюнкции. В случае ПЛМ многократно используемая конъюнкция может дважды применяться в матрице ИЛИ. Такой свободы нет в упрощенных ПМЛ, поскольку там данная матрица не программируется.

Таблица 1. Пример таблицы истинности и ее логических функций

Рис. 3. Реализация функций из табл. 1 с помощью ПЛМ (а), ПМЛ (б) и ППЗУ (в)

В программируемом ПЗУ значение 1 принимает именно то пересечение (конъюнкция), которое соответствует входной комбинации. Поэтому при наличии

комбинаций в матрице ИЛИ надо программировать связи, для которых в таблице истинности указана единица. Ясно, что программируемое ПЗУ как бы воспроизводит таблицу истинности, тогда как ПЛМ и ПМЛ представляют логические функции.

В программируемом ПЗУ можно запоминать любые таблицы истинности, а ПЛМ и ПМЛ предоставляют ограниченный набор логических функций умножения и сложения, поэтому с их помощью реализуются не произвольные таблицы истинности, а только те, которые легко преобразовать в простые логические функции. Ради повышения эффективности применения ПМЛ необходимо предельно упрощать указанные функции средствами булевой алгебры и при необходимости преобразовывать операции И и ИЛИ с помощью закона Де Моргана. Теперь это делается не вручную, а с помощью специальных программ на любом персональном компьютере.

Программируемая матричная логика

ПМЛ – важнейший представитель программируемых логических устройств. Они выпускаются во множестве вариантов, основанных на общем принципе (рис. 2б) и различающихся исполнением операции ИЛИ на выходе. Наиболее распространенные варианты показаны на рис. 4.

Версия ПМЛ с выходом High (H) представляет собой базовый вариант, показанный на рис. 2. У версии Low (L) выход обращен. Выход Sharing (S) аналогичен с ПЛМ. Здесь матрица ИЛИ частично программируется: две смежные схемы ИЛИ могут произвольно распределять между собой выделенные для них схемы И, что позволяет формировать такие функции, для которых иначе не хватило бы схем И. Многие ПМЛ допускают использование выхода в качестве входа или программирование его в виде двунаправленного порта (I/O). Для этого служит элемент с тремя состояниями на выходе, у которого состояние Enable (разблокировать) само является логической функцией.

ПМЛ успешно применяются для коммутации. Чтобы не обращаться к дополнительным схемным элементам, в ПМЛ встраиваются дополнительные регистры R, снабженные общим тактовым вводом для реализации синхронной коммутации. Кроме того, часто выходные сигналы через обратную связь внутри ИС подаются на матрицу И. При этом исчезает необходимость строить внешнюю цепь обратной связи и занимать какие-либо входы.

Разнообразие типов ПМЛ облегчает выбор оптимальной схемы (рис. 4). В последнее время все большее распространение получают ПМЛ с программируемой структурой выхода. Такая изменяемая «макроячейка» типа V также представлена на рис. 4. Главным звеном в ней служит мультиплексор, посредством кото-

рого выбирается один из четырех режимов работы. Они определяются путем программирования функциональных разрядов f0 и f1.

Рис. 4. Выходные схемы ПМЛ

Возможные режимы работы показаны в табл. 2. Разряд f0 задает нормальное или инверсное состояние выхода. Переключение между комбинаторным и синхронным режимами происходит по разряду f1. При этом одновременно переключается обратная связь со вторым мультиплексором между выходом и регистром. Таким путем удается воплотить большинство разновидностей ПМЛ в микросхемах одного типа.

Таблица 2. Режимы работы изменяемой макроячейки

Обзор типов ПЛУ

Если требуется построить цифровую схему, для которой нужно больше пары логических элементов 7400-й серии, имеет смысл реализовать ее на ПЛУ. Уже простейшие ПМЛ содержат от 300 до 500 логических элементов. Даже если пользователь способен задействовать только половину из них, в одном чипе будет реализовано множество схем. Единственная интегральная микросхема заменяет целый набор ТТЛ логики. Но этим выигрыш от снижения числа схемных элементов не ограничивается:

•монтажные платы становятся компактнее, что экономит место и средства;

•как правило, ПЛУ дешевле равнозначного количества требуемых схемных элементов;

•повышается надежность, так как соединения внутри ПЛУ надежнее, чем наружный монтаж на плате;

•упрощается внесение изменений в устройство схемы благодаря возможности перепрограммировать ПЛУ.

Все ПМЛ оснащены конфигурируемыми выходными ячейками типа V (рис. 4). Количество макроячеек является важнейшим параметром, характеризующим архитектуру ПЛУ: он указывает число логических функций, которые могут быть сформированы. Каждый вход ПЛУ и каждая макроячейка выдают по одному сигналу в матрицу И. Поэтому

Некоторые ПЛУ имеют существенно больше входов в матрицу И. Причина в том, что через обратную связь на каждую макроячейку подается несколько сигналов вместо одного, или в том, что расширитель конъюнктивных членов подсоединяется к матрице через обратную связь. Разумеется, в чипе имеется удвоенное количество входов в матрицу, так как каждый сигнал разрешается подать в инверсной форме (рис. 2). Количество выходов матрицы определяет возможное число конъюнктивных членов ПЛУ. При равномерном распределении по макроячейкам

,

что для 16V8 при 64 выходах составляет 64/8 = 8. Для большинства функций этого достаточно, но далеко не для всех. Чтобы формировать сложные функции, иногда приходится заимствовать члены соседнего произведения (Product Term Sharing) или применять расширители конъюнктивных членов, которые могут быть подчинены произвольным функциям. В данном отношении они ведут себя подобно ПЛМ. В случае столбцовой архитектуры наряду с числом контактов, используемых исключительно в качестве входов, задается число макроячеек. Их вы-

ход также допустимо сконфигурировать как вход, что уже знакомо по выходным ячейкам. Архитектуру ПМЛ нетрудно определить по обозначению типа прибора:

Наибольшее распространение получила микросхема 22V10. Здесь имеются две опции:

•«in system progamming» ( микросхема программируется прямо на плате без программатора);

•«zero power» ( статическое потребление тока равно нулю).

Сложные ПЛУ (СПЛУ) состоят из множества стандартных ПЛУ в одном чипе, соединяемых с помощью программируемого монтажа. СПЛУ позволяют реализовать в одном чипе такую схему, на которую пошло бы множество стандартных ПМЛ. Естественно, в этом случае сборщик устройства становится очень сложным, так как он должен распределить задачу по имеющимся ПЛУ, а затем запрограммировать необходимые соединения внутри чипа.

Для большинства ПЛУ характерно удивительно высокое потребление мощности даже в статическом состоянии, хотя речь идет о КМОП интегральных схемах. Причина кроется в нагрузочных резисторах «монтажных» логических схем И. Но бывают и ПЛУ, у которых потребление тока растет с частотой, так что в статическом режиме оно равно нулю.

Когда в коммутационной схеме надо запоминать пару разрядов, используются регистры макроячеек. Однако названный способ при большом объеме данных непрактичен, и приходится подключать внешнее ОЗУ. У некоторых новейших СПЛУ в этом нет необходимости, поскольку часть такой БИС допустимо сконфигурировать как ОЗУ.

Матрицы логических элементов, программируемые пользователем

Группу логических схем, также программируемых пользователем, составляют вентильные матрицы с программированием в процессе эксплуатации, или мат-

ричные БИС FPGA (Field Programmable Gate Arrays). Они отличаются от вышеопи-

санных ПЛУ более простыми ячейками своей внутренней структуры, состоящей из вентилей, триггеров и отчасти из простых ПЛУ типа 5V2. По числу эквивалентов логических схем БИС FPGA иногда превосходят СПЛУ, благодаря чему пригодны для синтеза сложных схем. Они особенно выгодны там, где решаемая задача плохо согласуется с архитектурой ПЛУ. Наряду с вводом реализуемой функции на языке описания, здесь принято непосредственно рисовать схему соединений, где примитивные ячейки связаны с требуемой функцией. Таким способом с помощью БИС FPGA удается создавать практически любые схемы в одном чипе подобно тому, как это делалось при размещении ТТЛ логики на плате.

По сравнению с синтезом ПЛУ здесь добавляется еще один этап проектирования, в ходе которого, подобно трассировке печатных плат, используемые логические элементы вначале размещаются по объему БИС FPGA, а затем связываются между собой. Естественно, соответствующий трассировщик должен учитывать архитектуру БИС и точно знать возможности прокладки соединений. Иногда указывают, какие соединения критичны по быстродействию, так как пути передачи данных характеризуются разной скоростью и короткие трассы работают быстрее, нежели те, что проходят через несколько вершин изломов. Здесь не обойтись без временного моделирования с учетом результатов монтажа.

Убольшинства БИС FPGA схема соединений хранится в собственном ОЗУ

ипосле включения питания автоматически загружается через последовательный порт из отдельного EPROM. Совсем иначе происходит программирование БИС FPGA по технологии программируемых связей (Programmable Link). В этом случае соединения устанавливаются программным путем аналогично тому, как программирование ППЗУ осуществлялось путем удаления плавких соединений. Программируемое соединение, как и плавкое, не стирается.

Компьютерное проектирование ПЛУ

Чтобы «персонифицировать» схему ПМЛ, сначала определяют логические схемы, подлежащие программированию, а затем приступают к собственно программированию. ПМЛ проектируются с помощью пакетов программ, работающих на любом персональном компьютере. Этапы проектирования демонстрируются на рис. 5. Обычно используется несколько форматов ввода, самые распространенные из них показаны на рисунке. Логические функции и таблицы истинности вводятся с помощью текстового процессора. При проектировании коммутационных схем применяются также диаграммы состояний и условия переходов.

Рис. 5. Последовательность компьютерного проектирования ПЛУ

Схема соединений является особенно эффективным способом ввода исходной информации. Здесь задействуются библиотеки, где наиболее распространен-