Регистры

.pdf

1.1.2. Регистры

1.1.2.1. Общие сведения. Классификация

Регистр – последовательностное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними.

Регистр представляет собой упорядоченную последовательность триггеров (как правило, D-триггеров), число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединенных друг с другом при помощи комбинационных цифровых устройств.

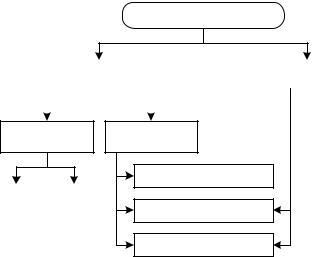

Классификация регистров приведена на рис. 1.11. Регистры различают на накопительные (регистры памяти, хранения) и сдвигающие.

Регистры

|

накопительные |

|

сдвигающие |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

по направлению передачи

однонаправленные |

|

реверсивные |

|

|

|

по способу ввода-вывода

параллельные

последовательные

универсальные

Рис. 1.11. Классификация регистров

В свою очередь сдвигающие регистры классифицируются по способу вводавывода информации и по направлению передачи информации. По способу вводавывода информации регистры различают на:

-параллельные, считывание и запись информации в которых происходит одновременно со всех входов на все выходы;

-последовательные, считывание и запись информации в которых происходит по очереди от первого триггера до последнего (со входа регистра информация записывается в первый триггер, в то время как та информация, которая была в этом триггере, перезаписывается в следующий и т.д. до последнего триггера на выходе регистра);

-универсальные (комбинированные), имеющие свойства как параллельных, так и последовательных регистров.

По направлению передачи информации различают однонаправленные и реверсивные регистры

Типичными операциями при работе регистров в цифровых электронных устройствах являются:

-прием слова в регистр;

-передача слова из регистра;

-поразрядные логические операции;

-сдвиг слова влево или вправо на заданное число разрядов;

-преобразование последовательного кода слова в параллельный и обратно;

-установка регистра в начальное состояние (сброс).

Принцип действия регистров ничем не отличается от принципа действия D- триггера, срабатывающих по фронту тактового сигнала. По положительному фронту тактового сигнала С каждый из выходов регистра устанавливается в тот уровень, который был в этот момент на соответствующем данному выходу входе D, и сохраняется таковым до прихода следующего положительного фронта сигнала С.

1.1.2.2. Параллельные регистры

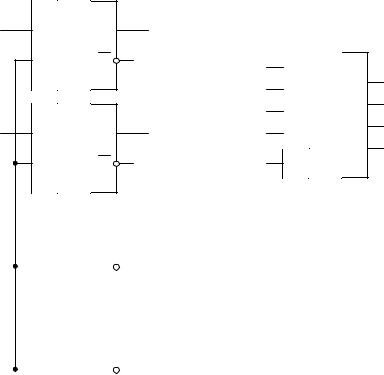

Параллельный регистр служит для запоминания многоразрядного двоичного слова. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырехразрядного параллельного регистра приведена на рис. 1.12, а его условно-графическое обозначение – на рис. 1.12, б.

При записи информации в параллельный регистр все биты (двоичные разряды) должны быть записаны одновременно. Поэтому все тактовые входы триггеров, входящих в состав регистра, объединяются параллельно. Для уменьшения входного тока вывода синхронизации C на этом входе в качестве усилителя часто ставится инвертор.

В условно-графическом обозначении возле каждого входа D указывается степень двоичного разряда, который должен быть запомнен в этом триггере регистра. Точно таким же образом обозначаются и выходы регистра. То, что микросхема является регистром, указывается в центральном поле условнографического обозначения символами RG.

D0 |

Т |

|

Q0 |

|

|

|

D |

Q |

|

|

|||

|

C |

Q |

|

D0 |

RG |

|

|

|

|

|

|||

|

|

|

|

D1 |

Q0 |

|

|

|

|

|

Q1 |

||

|

Т |

|

|

D2 |

||

|

|

|

Q2 |

|||

D1 |

D |

Q |

Q1 |

D3 |

||

Q3 |

||||||

|

C |

Q |

|

C |

||

|

|

|

||||

|

|

|

|

|

б |

D2 |

|

|

D |

Т |

Q |

|

|

Q2 |

||

|

|

|

|

|||||||

|

|

|

|

|||||||

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D3 |

|

|

D |

Т |

Q |

|

|

Q3 |

||

|

|

|

|

|||||||

|

|

|

|

|||||||

C |

|

|

C |

|

|

|

|

|

|

Рис. 1.12. Логическая схема |

|

|

|

Q |

|

|

|||||

|

|

|

|

параллельного регистра (а) |

||||||

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

и его условно-графическое |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

обозначение (б) |

Следует помнить, что назначение разрядов является условным. Если по каким-либо причинам (например, с точки зрения разводки печатной платы) удобно изменить нумерацию разрядов, то это можно свободно сделать. При этом нужно не забывать, точно таким же образом, изменить номера выходов параллельного регистра.

Для реализации параллельного регистра можно использовать как триггеры со статическим, так и с динамическим входом синхронизации. В литературе при

использовании для построения параллельного регистра триггеров-защелок этот регистр, в свою очередь, называют регистром-защелкой.

При использовании регистров со статическим входом тактирования следует соблюдать осторожность, так как при единичном потенциале на входе синхронизации C, сигналы с входов регистра будут свободно проходить на его выходы. В таких случаях обычно используется двухтактная синхронизация.

Промышленностью выпускаются четырехразрядные и восьмиразрядные микросхемы параллельных регистров. Для построения восьмиразрядных микросхем обычно используются регистры со статическим входом синхронизации.

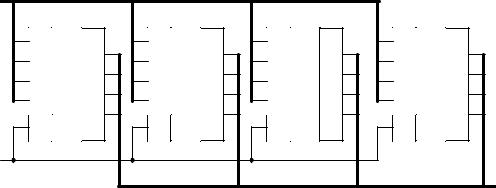

При решении практических задач часто требуется разрядность параллельных регистров большая восьми. В таком случае можно увеличивать разрядность регистров параллельным соединением готовых микросхем. Принципиальная схема параллельного соединения четырех регистров приведена на рис. 1.13.

1 |

D |

RG |

|

|

0 |

Q0 |

1 |

2 |

D1 |

||

|

Q1 |

2 |

|

3 |

D2 |

||

|

Q2 |

3 |

|

4 |

D3 |

||

|

Q3 |

4 |

|

|

C |

||

|

|

|

5 |

D |

RG |

|

|

0 |

Q0 |

5 |

6 |

D1 |

||

|

Q1 |

6 |

|

7 |

D2 |

||

|

Q2 |

7 |

|

8 |

D3 |

||

|

Q3 |

8 |

|

|

C |

||

|

|

|

9 |

D |

RG |

|

|

0 |

Q0 |

9 |

10 |

D1 |

||

|

Q |

10 |

|

11 |

|

||

|

D2 |

1 |

|

|

Q |

11 |

|

12 |

|

||

|

D3 |

2 |

|

|

Q |

12 |

|

|

C |

3 |

|

|

|

|

|

13 |

D |

RG |

|

|

0 |

Q |

13 |

14 |

|

||

|

D1 |

0 |

|

|

Q |

14 |

|

15 |

|

||

|

D2 |

1 |

|

|

Q |

15 |

|

16 |

|

||

|

D3 |

2 |

|

|

Q |

16 |

|

|

C |

3 |

|

|

|

|

|

Рис. 1.13. Пример увеличения разрядности параллельного регистра

1.1.2.3. Последовательные регистры

Кроме параллельного соединения триггеров для построения регистров используются последовательное соединение этих элементов.

Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем).

Принципиальная схема последовательного регистра, собранного на основе D- триггеров и позволяющего осуществить преобразование последовательного кода

впараллельный, приведена на рис. 1.14, а.

Вэтом регистре триггеры соединены последовательно, то есть выход первого соединен с входом второго и т.д. Входы синхронизации в последовательных регистрах, как и в параллельных, объединяются. Это обеспечивает одновременность смены состояния всех триггеров, входящих в состав последовательного регистра.

D0 |

|

|

|

D |

Т |

Q |

|

|

|

||

|

|

|

|

|

|

|

|||||

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

Т |

Q |

|

|

|

||

|

|

|

|

|

|

|

|

||||

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

Т |

Q |

|

|

|

||

|

|

|

|

|

|

|

|

||||

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

Т |

Q |

|

|

|

||

|

|

|

|

|

|

|

|

||||

C |

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

а

Q0 |

|

|

|

|

D0 |

RG |

Q0 |

|

Q |

||

|

|

|

1 |

Q1 |

|

|

Q2 |

C |

|

Q3 |

|

|

|

б

Q2

Q3 Рис. 1.14. Логическая схема последовательного регистра (а) и его условно-графическое

обозначение (б)

Преобразование последовательного кода в параллельный осуществляется следующим образом. Отдельные биты двоичной информации последовательно подаются на вход D0. Каждый бит сопровождается отдельным тактовым импульсом, который поступает на вход синхронизации C.

Пусть на вход регистра поступает сигнал, временная диаграмма которого изображена на рис. 1.15, тогда состояние выходов этого регистра будет последовательно принимать значения

№ |

1 |

2 |

3 |

4 |

|

такта |

|||||

|

|

|

|

||

|

|

|

|

|

|

Q0 |

1 |

0 |

1 |

1 |

|

Q1 |

х |

1 |

0 |

1 |

|

Q2 |

х |

х |

1 |

0 |

|

Q3 |

х |

х |

х |

1 |

После поступления первого тактового импульса логический уровень, присутствующий на входе D0, запоминается в первом триггере и поступает на его выход, а так как он соединен с входом второго триггера, то и на его вход.

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q0 |

|

|

первый бит |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q1 |

|

|

|

|

|

первый бит |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q2 |

|

|

|

|

|

|

|

|

первый бит |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q3 |

|

|

|

|

|

|

|

|

|

|

первый бит |

||||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

первый |

второй |

третий |

четвертый t |

||||||||

|

|

|

|

||||||||||||

|

|

|

|

такт |

такт |

такт |

|

такт |

|||||||

Рис. 1.15. Идеализированная временная диаграмма работы сдвигового регистра

После поступления второго тактового импульса логический уровень, присутствующий на входе второго триггера, запоминается в нем и поступает на его выход, а так как он соединен с входом третьего триггера, то и на его вход. Одновременно следующий бит запоминается в первом триггере.

После поступления четвертого тактового импульса в триггерах регистра будут записаны уровни бит, которые последовательно присутствовали на входе D0. Теперь этими битами можно воспользоваться, например, для отображения на индикаторах.

1.1.2.4. Универсальные регистры

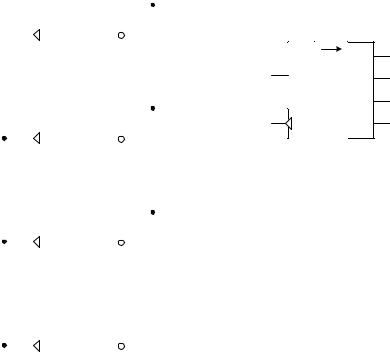

Регистры сдвига выполняют обычно как универсальные последовательнопараллельные микросхемы. Это связано с необходимостью записи в регистр параллельного двоичного кода при преобразовании параллельного кода в последовательный.

Переключение регистра из параллельного режима работы в последовательный и наоборот осуществляется при помощи мультиплексора. Использование мультиплексора позволяет входы триггеров регистра либо подключать к внешним выводам микросхемы, либо подключать к выходу предыдущего триггера.

Схема универсального регистра с использованием мультиплексоров на логических элементах 2И-2ИЛИ приведена на рис. 1.16.

DI |

& |

1 |

D |

Т |

Q |

Q0 |

|

|

|

|

|

|

|

|

|||

D0 |

& |

|

C |

|

Q |

|

DI |

RG |

|

|

|

|

|

|

|||

мульти- |

|

|

|

|

|

|

D0 |

|

плексор |

|

|

|

|

|

|

Q0 |

|

D0 |

|

|

|

|

|

D1 |

||

|

MS |

|

Т |

|

|

|||

|

D |

Q |

Q1 |

Q1 |

||||

|

D1 |

|

|

D |

||||

|

D |

|

|

|

|

|

2 |

Q2 |

|

|

C |

|

Q |

|

D3 |

||

D1 |

2 |

|

|

|

|

|||

D3 |

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

V |

3 |

|

|

|

|

|

|

|

|

|

|

D0 |

MS |

D |

Т |

Q |

Q2 |

C |

|

|

D1 |

|

|

|

|

|||

D2 |

D2 |

|

C |

|

Q |

|

|

б |

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

MS |

|

|

D |

Т |

Q |

|

|

|

Q3 |

||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

D2 |

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

Рис. 1.16. Логическая схема |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

универсального регистра (а) |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

и его условно-графическое |

|||||||

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

обозначение (б) |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

В этой схеме для переключения регистра из последовательного режима работы в параллельный используется вывод V. Подача на этот вход единичного потенциала превращает схему в параллельный регистр. При этом на входы ключей, подключенных к информационным входам D, подается единичный потенциал. Это приводит к тому, что сигналы с входов параллельной записи данных поступают на входы логических элементов ИЛИ, а на входы мультиплексоров, подключенных к выходам предыдущих триггеров, подаются нулевые потенциалы. То есть на их выходах будут присутствовать нулевые потенциалы, и они не будут мешать работе схемы.

Подача на вход V нулевого потенциала приводит к отключению входов параллельных данных от входов триггеров. Сигналы же с выхода предыдущего триггера свободно проходит через верхние логические элементы И на вход последующего триггера, так как на его второй вход подается единичный потенциал.

Инверторы на входах V и C использованы для усиления входного сигнала по току. В результате входной ток микросхемы будет равен не суммарному току четырех логических элементов И, а входному току инвертора.

Условно-графическое изображение универсального регистра приведено на рис. 1.16, б. Вход последовательного ввода данных на этом рисунке обозначен как DI и отделен от других групп входов чертой. Точно так же выделены в отдельные группы и входы управления V и синхронизации C.