- •Блок управления и синхронизации

- •Регистр управления/статуса приемопередатчика scon

- •Функциональное назначение бит регистра управления/статуса приемопередатчика scon.

- •Скорость приема/передачи информации через последовательный порт

- •Регистр управления мощностью pcon

- •Настройка таймера 1 для управления скоростью работы последовательного порта.

- •Режим 0. Синхронный последовательный порт.

- •Режим 1. Асинхронный восьмиразрядный последовательный порт.

- •Режим 2. Асинхронный девятиразрядный последовательный порт с фиксированной скоростью передачи.

- •Режим 3. Асинхронный девятиразрядный последовательный порт.

- •03 Rr a ;Сдвинуть содержимое аккумулятора вправо

- •8D15 mov 15h,r6 ;в первом операнде использована прямая байтовая адресация, а во втором – регистровая

- •Режим 0

- •Режим 1

- •Режим 2

- •Режим 3

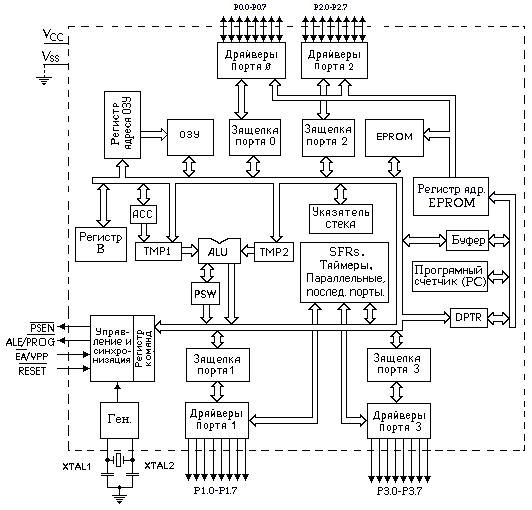

Архитектура микроконтроллеров MCS-51

Архитектура семейства MCS-51 в значительной мере предопределяется ее назначением - построение компактных и дешевых цифровых устройств. Все функции микроЭВМ реализуются с помощью единственной микросхемы. В состав семейства MCS-51 входит целый ряд микросхем от самых простых микроконтроллеров до достаточно сложных. Микроконтроллеры семейства MCS-51 позволяют выполнять как задачи управления различными устройствами, так и реализовывать отдельные узлы аналоговой схемы. Все микросхемы этого семейства работают с одной и той же системой команд, большинство из них выполняется в одинаковых корпусах с совпадающей цоколевкой (нумерация ножек для корпуса). Это позволяет использовать для разработанного устройства микросхемы разных фирм - производителей (таких как Intel, Dallas, Atmel, Philips и т.д.) без переделки принципиальной схемы устройства и программы.

Рис 1. Структурная схема контроллера К1830ВЕ751

Структурная схема контроллера представлена на рис.1. и состоит из следующих основных функциональных узлов: блока управления, арифметико-логического устройства, блока таймеров/счетчиков, блока последовательного интерфейса и прерываний, программного счетчика, памяти данных и памяти программ. Двусторонний обмен осуществляется с помощью внутренней 8-разрядной магистрали данных. Рассмотрим подробнее назначение каждого блока. По такой схеме построены практически все представители семейства MCS-51. Различные микросхемы этого семейства различаются только регистрами специального назначения (в том числе и количеством портов). Система команд всех контроллеров семейства MCS-51 содержит 111 базовых команд с форматом 1, 2 или 3 байта и не изменяется при переходе от одной микросхемы к другой. Это обеспечивает прекрасную переносимость программ с одной микросхемы на другую.

Блок управления и синхронизации

Блок управления и синхронизации (Timing and Control) предназначен для выработки синхронизирующих и управляющих сигналов, обеспечивающих координацию совместной работы блоков ОЭВМ во всех допустимых режимах ее работы.В состав блока управления входят:

устройство формирования временных интервалов,

логика ввода-вывода,

регистр команд,

регистр управления потреблением электроэнергии,

дешифратор команд, логика управления ЭВМ.

Устройство формирования временных интервалов предназначено для формирования и выдачи внутренних синхросигналов фаз, тактов и циклов. Количество машинных циклов определяет продолжительность выполнения команд. Практически все команды ОЭВМ выполняются за один или два машинных цикла, кроме команд умножения и деления, продолжительность выполнения которых составляет четыре машинных цикла. Обозначим частоту задающего генератора через Fг. Тогда длительность машинного цикла равна 12/Fг или составляет 12 периодов сигнала задающего генератора. Логика ввода - вывода предназначена для приема и выдачи сигналов, обеспечивающих обмен информации с внешними устройствами через порты ввода вывода Р0-Р3.

Регистр команд предназначен для записи и хранения 8-ми разрядного кода операции выполняемой команды. Код операции, с помощью дешифратора команд и логики управления ЭВМ, преобразуется в микропрограмму выполнения команды.

Регистр управления потреблением (PCON) позволяет останавливать работу микроконтроллера для уменьшения потребления электроэнергии и уменьшения уровня помех от микроконтроллера. Еще большего уменьшения потребления электроэнергии и уменьшения помех можно добиться, остановив задающий генератор микроконтроллера. Этого можно достичь при помощи переключения бит регистра управления потреблением PCON. Для варианта изготовления по технологии n-МОП (серия 1816 или иностранных микросхем, в названии которых в середине отсутствует буква 'c') регистр управления потреблением PCON содержит только один бит, управляющий скоростью передачи последовательного порта SMOD, а биты управления потреблением электроэнергией отсутствуют.

Арифметико-логическое устройство (ALU) представляет собой параллельное восьмиразрядное устройство, обеспечивающее выполнение арифметических и логических операций. АЛУ состоит из:

регистров аккумулятора, регистров временного хранения TMP1 и TMP2,

ПЗУ констант,

сумматора,

дополнительного регистра (регистра В),

аккумулятора (ACC),

регистра состояния программ (PSW).

Регистр аккумулятор и регистры временного хранения - восьмиразрядные регистры, предназначенные для приема и хранения операндов на время выполнения операций над ними. Эти регистры программно не доступны.

ПЗУ констант обеспечивает выработку корректирующего кода при двоично-десятичном представлении данных, кода маски при битовых операциях и кода констант.

Параллельный восьмиразрядный сумматор представляет собой схему комбинационного типа с последовательным переносом, предназначенную для выполнения арифметических операций сложения, вычитания и логических операций сложения, умножения, неравнозначности и тождественности.

Регистр B - восьмиразрядный регистр, используемый во время операций умножения и деления. Для других инструкций он может рассматриваться как дополнительный сверхоперативный регистр.

Аккумулятор - восьмиразрядный регистр, предназначенный для приема и хранения результата, полученного при выполнении арифметико-логических операций или операций сдвига

Блок последовательного интерфейса и прерываний (ПИП) предназначен для организации ввода - вывода последовательных потоков информации и организации системы прерывания программ. В состав блока входят:

буфер ПИП,

логика управления,

регистр управления,

буфер передатчика,

буфер приемника,

приемопередатчик последовательного порта,

регистр приоритетов прерываний,

регистр разрешения прерываний,

логика обработки флагов прерываний и схема выработки вектора.

Счетчик команд (Program Counter) предназначен для формирования текущего 16-разрядного адреса внутренней памяти программ и 8/16-разрядного адреса внешней памяти программ. В состав счетчика команд входят 16-разрядные буфер РС, регистр РС и схема инкремента (увеличения содержимого на 1).

Память данных (RAM) предназначена для временного хранения информации, используемой в процессе выполнения программы.

Порты P0, P1, P2, P3 являются квазидвунаправленными портами ввода - вывода и предназначены для обеспечения обмена информацией ОЭВМ с внешними устройствами, образуя 32 линии ввода- вывода.

Регистр состояния программы (PSW) предназначен для хранения информации о состоянии АЛУ при выполнении программы.

Память программ (EPROM) предназначена для хранения программ и представляет собой постоянное запоминающее устройство (ПЗУ). В разных микросхемах применяются масочные, стираемые ультрафиолетовым излучением или FLASH ПЗУ.

Регистр указателя данных (DPTR) предназначен для хранения 16 - разрядного адреса внешней памяти данных или памяти программ.

Указатель стека (SP) представляет собой восьмиразрядный регистр, предназначенный для организации особой области памяти данных (стека), в которой можно временно сохранить любую ячейку памяти.

![]()

Построение памяти микроконтроллеров семейства MCS-51

Микроконтроллеры семейства MCS-51 построены по Гарвардской архитектуре. Это означает, что память данных и память программ в этих микросхемах разделены и имеют отдельное адресное пространство. В этих микроконтроллерах имеется пять адресных пространств: память программ, внешняя память данных три для внутренней памяти. Такое построение памяти позволяет удвоить доступное адресное пространство. Кроме того такое построение памяти позволяет в ряде случаев увеличить быстродействие микросхем.

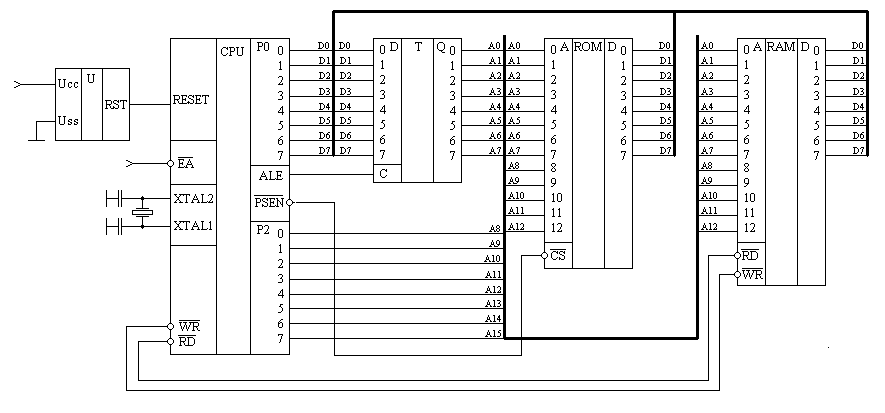

Схема подключения внешних микросхем памяти к микроконтроллерам семейства MCS-51 показана на рисунке 1. Регистр адреса D3 на этой схеме предназначен для запоминания младших 8-ми бит адреса, передаваемых через шину данных/памяти, совмещенную с портом P0. Старшие восемь бит адреса передаются через шину адреса, совмещенную с портом P2. Во время передачи адреса через порт P0, микроконтроллер вырабатывает синхроимпульс на ножке ALE. Именно этот импульс позволяет запомнить младший байт адреса в регистре D3.

Для обращения к памяти данных и к памяти программ используются одни и те же шина адреса и шина данных, но разные управляющие сигналы. Для чтения памяти программ вырабатывается сигнал PSEN, а для чтения памяти данных вырабатывается сигнал RD. Для записи информации в память данных вырабатывается сигнал WR. То есть память программ доступна только для чтения, а память данных доступна и для чтения и для записи любой информации, записанной в двоичном коде.

Рисунок 1. Схема подключения схем внешней памяти к микроконтроллерам семейства MCS-51

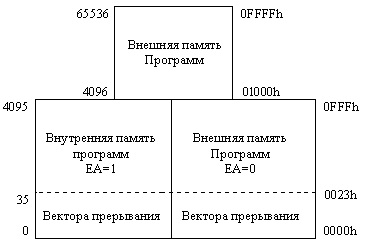

Память программ микроконтроллеров MCS-51

Память программ предназначена для хранения программ и имеет отдельное от памяти данных адресное пространство объемом 64 Кбайт, причем для некоторых микросхем (например КР1816ВЕ51, КМ1819ВЕ751, КР1830ВЕ51) для хранения программ на кристалле микроконтроллера расположено ПЗУ. Это ПЗУ отображается в область млаших адресов памяти программ. Учитывая, что выполнение программы после сброса микроконтроллера всегда начинается с нулевого адреса памяти программ, то при включении питания начнет выполняться программа, записанная во внутненнем ПЗУ микроконтроллера. Микроконтроллеры, не имеющие внутреннего ПЗУ (например КР1816ВЕ31 и КР1830ВЕ31) могут работать только с внешней микросхемой ПЗУ емкостью до 64 Кбайт (при использовании портов P1 и P3 в качестве расширителя адреса объем подключаемой ПЗУ может быть увеличен до 1Гбайта). Микроконтроллеры семейства MCS-51 имеют внешний вывод EA, с помощью которого можно запретить работу внутренней памяти, для чего необходимо подать на вывод EA логический "0" (соединить этот вывод с корпусом). При этом внутренняя память программ отключается и, начиная с нулевого адреса, все обращения происходят к внешней памяти программ.

Доступ к внешней памяти программ осуществляется в двух случаях:

при действии сигнала EA=0 независимо от адреса обращения,

в любом случае, если программный счетчик (РС) содержит число большее, чем максимальная ячейка внутренней памяти программ.

Распределение памяти программ микроконтроллера КР1830ВЕ51 представлено ниже:

|

Для чтения памяти программ используются команды MOVC A, A+@DPTR и MOVC A, A+@PC |

Рисунок 2. Адресное пространство памяти программ.

Для других микроконтроллеров этого семейства изменяется только объем внутренней памяти программ и количество доступных векторов прерываний программы.

Ниже приведены адреса векторов прерываний и соответствующие им аппаратурные источники прерываний программы:

Вектор прерывания |

Флаги, вызывающие прерывание |

Источник прерывания |

0000Н |

- |

Рестарт (сброс) контроллера RESET |

0003Н |

IE0 |

внешнее прерывание INT0 |

000bН |

TF0 |

Таймер 0 |

0013Н |

IE1 |

внешнее прерывание INT1 |

001bН |

TF1 |

Таймер 1 |

0023Н |

RI, TI |

Последовательный порт |

002bН |

TF2, EXF2 |

Таймер 2 |

0033Н |

CF, CCFn(n=0:4) |

Набор программируемых счётчиков (РСА) |

003bН |

AIF |

Аналого-цифровой преобразователь |

0043Н |

CF1,C1CCFn(n=1:4) |

Набор программируемых счётчиков (РСА1) |

004bН |

SEPIF |

Последовательный порт SEP |

0053Н |

IE2 |

внешнее прерывание INT2 |

005bН |

IE3 |

внешнее прерывание INT3 |

0063Н |

IE4 |

внешнее прерывание INT4 |

006bН |

IE5 |

внешнее прерывание INT5 |

0073Н |

IE6 |

внешнее прерывание INT6 |

Примечание: вектора прерывания, выделенные:

жирным подчеркнутым текстом- присутствуют во всех микросхемах семейства;

жирным текстом- отсутствуют в микросхемах 8051,8031, КР1816ВЕ31, КР1816ВЕ51, КР1816ВЕ751 КР1830ВЕ31, КР1830ВЕ51, КР1830ВЕ751;

обычным текстом- присутствуют только в микросхемах 8Х51FA, FB, FC и GB

курсивом- присутствуют только в микросхеме 8Х51GB

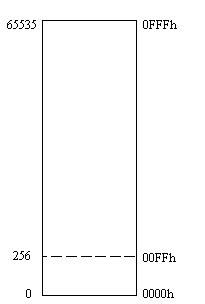

Внешняя память данных микроконтроллеров MCS-51

Внешняя память данных предназначена для временного хранения информации, используемой в процессе выполнения программы. Эта память физически должна быть подключена к микросхеме микроконтроллера при помощи схемы, изображенной на рисунке 1. Максимальный объем этой памяти определяется регистром DPTR и составляет 64 Кбайта. Точно также как и в случае внешней памяти программ, объем внешней памяти данных может быть увеличен за счет использования портов P1 и P3 до 1 Гбайта. Внешняя память данных для своей работы требует использование портов P0, P2 и P3. Это приводит к увеличению габаритов устройства, увеличению уровня помех и, в конечном итоге, увеличения стоимости устройства в целом. Поэтому в современных устройствах внешняя память не используется. Однако, в некоторых микроконтроллерах (например 87с550 фирмы DALLAS) команды обращения к внешней памяти используются для работы с дополнительной внутренней памятью большого объема.

|

Для обращения к внешней памяти данных используются команды MOVX A, @DPTR (команда чтения) и MOVX @DPTR, A (команда записи) |

Иногда для того, чтобы сохранить порт P2 в качестве порта общего использования, для обращения к памяти данных используются команды MOVX A, @R0 или MOVX A, @R0 (команды чтения) MOVX@R0, A MOVX@R0, A (команды записи) |

Рисунок 3. Адресное пространство внешней памяти данных.

Отметим, что в качестве внешней памяти данных могут быть использованы как микросхемы ОЗУ так и микросхемы ПЗУ.

Внутренняя память данных микроконтроллеров MCS-51

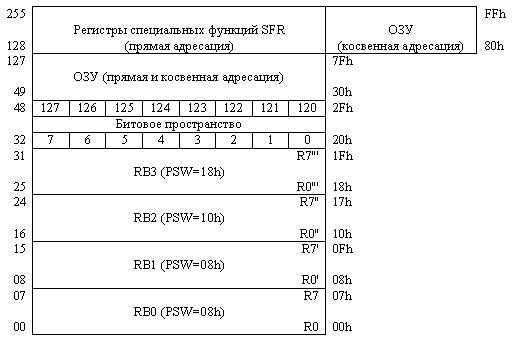

Несмотря на то, что это самое маленькое адресное пространство из рассматриваемых, оно устроено наиболее сложным образом. Распределение памяти данных микроконтроллеров серии MCS-51 приведено на рисунке 4.

Рисунок 4. Адресное пространство внутренней памяти данных.

Внутреннее ОЗУ данных предназначено для временного хранения информации, используемой в процессе выполнения программы, и занимает 128 младших байт, с адресами от 000h до 07Fh для микроконтроллеров 8051, 8031, КР1816ВЕ31, КР1816ВЕ51, КР1816ВЕ751 КР1830ВЕ31, КР1830ВЕ51, КР1830ВЕ751 или 256 восьмиразрядных ячеек, с адресами от 000h до 0FFh для всех остальных микроконтроллеров семейства.

Регистры специальных функций занимают адреса внутренней памяти данных с 080h по 0FFh. Так как адреса регистров специальных функций совпадают со старшими адресами внутреннего ОЗУ данных, то имеются особенности при использовании этих адресов внутренней памяти данных.

Система команд микроконтроллера позволяет обращаться к ячейкам внутренней памяти данных при помощи прямой и косвенно-регистровой адресации. При обращении к ячейкам памяти с адресами 0-127 использование любого из этих видов адресации будет производить выборку одной и той же ячейки памяти. При обращении к ячейкам ОЗУ с адресами 128-256 следует воспользоваться косвенно-регистровой адресацией. Учитывая, что работа со стеком ведётся при помощи косвенной адресации, то имеет смысл размещать в этой области памяти стек. Если же требуется обратиться к регистрам специальных функций, то нужно использовать прямую адресацию. Например:

MOV A, 80h ;Скопировать сигналы с внешних ножек порта P0 в аккумулятор

MOV R0, #80h ;Скопировать в аккумулятор содержимое

MOV A, @R0 ;ячейки внутреннего ОЗУ с адресом 80h

Регистры общего назначения позволяют писать самые эффективные программы. У микроконтроллеров семейства MCS-51 программирующему инженеру доступны восемь регистров. Более того, в этом семействе микроконтроллеров есть целых четыре набора (банка) регистров с именами RB0 - RB3. Банк регистров состоит из восьми восьмиразрядных регистров с именами R0, R1, …, R7. Несколько банков регистров служат для организации независимой работы нескольких параллельно выполняемых программ. Переключение банков регистров производится при помощи двух особых бит регистра слова состояния программы PSW (RS0 и RS1). Если организация нескольких параллельных потоков обработки данных не нужна, то можно пользоваться только нулевым банком регистров, включающимся автоматически после включения питания и сброса микроконтроллера, остальные ячейки памяти использовать как обычное ОЗУ.

Все четыре банка регистров объединены с 32 младшими байтами внутреннего ОЗУ данных (см. рисунок 4). Так как физически регистры и ячейки внутреннего ОЗУ объединены, то команды программы могут обращаться к регистрам, используя их имена R0-R7 ( регистровая адресация):

MOV A, R0 ;Скопировать содержимое регистра R0 в аккумулятор

MOV R7, A ;Скопировать содержимое регистра R7 в аккумулятор

или используя их адрес во внутренней памяти данных ( прямая байтовая адресация):

MOV A, 0 ;Скопировать содержимое нулевой ячейки ОЗУ в аккумулятор

MOV 7, A ;Скопировать содержимое аккумулятора в седьмую ячейку ОЗУ

Следующие после банков регистров внутреннего ОЗУ данных 16 ячеек памяти (адреса 20Н-2FH) образуют область памяти, к которой возможна как байтовая, так и битовая адресация. В этих ячейках располагаются 128 программных флагов (битовых ячеек памяти). Обращение к отдельным битам этих ячеек возможно по их битовым адресам. Например команды:

SETB 15 ;Запомнить в 15 флаге логическую единицу

JB 15, Metka ;Если в 15 флаге записана логическая единица, то перейти на метку

обращаются к 15 флагу, расположенному в старшем бите байтовой ячейки памяти 21h. Использование однобитовых ячеек памяти позволяет сократить необходимый для работы программы объём памяти данных, так как для хранения битовых переменных выделяется один бит в памяти данных, а не машинное слово, как это делается в универсальных микропроцессорах (компьютерах).

В битовой области сосредоточено только 128 флагов. Оставшиеся адреса в битовом пространстве используются для битовой адресации в области регистров специальных функций. Наиболее яркий пример использования битовой адресации в области регистров специальных функций - это обращение к отдельным ножкам параллельных портов:

CPL 92 ;Проинвертировать второй бит порта P1

Оставшаяся область памяти используется как обычное ОЗУ без особенностей. Хотя, надо отметить, что в современных микроконтроллерах эту память следует рассматривать как встроенные 256 регистров сверхоперативного ОЗУ. Основной памятью постепенно становится внутренняя память, доступная при помощи команд MOVX @DPTR, A

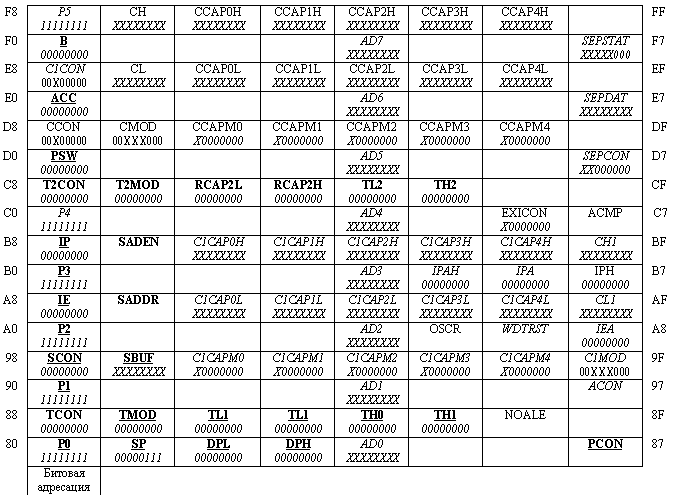

Регистры специальных функций.

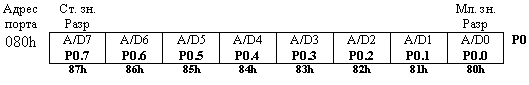

Регистры специальных функций - это дополнительные устройства, которые отображаются в адресное пространство внутренней памяти данных. В различных микроконтроллерах состав дополнительных устройств различается. Микроконтроллеры различаются между собой количеством параллельных портов, последовательных портов, таймеров. Некоторые из регистров специальных функций с указанием их адресов в адресном пространстве SFR внутреннего ОЗУ приведены на рисунке 5:

Рисунок 5. Адресное пространство регистров специальных функций.

Примечание: регистры, выделенные:

жирным подчеркнутым текстом- присутствуют во всех микросхемах семейства;

жирным текстом- отсутствуют в микросхемах 8051,8031, КР1816ВЕ31, КР1816ВЕ51, КР1816ВЕ751 КР1830ВЕ31, КР1830ВЕ51, КР1830ВЕ751;

обычным текстом- присутствуют только в микросхемах 8Х51FA, FB, FC и GB

курсивом- присутствуют только в микросхеме 8Х51GB

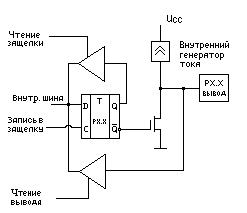

Устройство параллельных портов микроконтроллеров MCS-51

Порты P0, P1, P2, P3 являются квазидвунаправленными портами ввода- вывода и предназначены для обеспечения обмена информацией микроконтроллера с внешними устройствами, образуя 32 линии ввода- вывода. Каждый из портов содержит восьмиразрядный регистр, имеющий байтовую и битовую адресацию для установки (запись '1') или сброса (запись '0') разрядов этого регистра с помощью программного обеспечения. Выходы этих регистров соединены с внешними ножками микросхемы. Упрощенная схема одного разряда порта показана на рис. 1

Рис. 1. Упрощенная схема одного бита порта. |

Один разряд регистра - защелки порта представляет собой D-триггер. Данные с внутренней шины микроконтроллера записываются в регистр-защелку по сигналу "запись в защелку". Выход "Q" D-триггера подключается к внутренней шине (считывается) по сигналу "чтение защелки". Значение сигнала непосредственно с внешнего вывода порта считывается по сигналу "чтение вывода". Некоторые команды чтения порта используют сигнал "чтение защелки ", другие "чтение выода". Чтение внешних ножек микросхемы осуществляется командами: MOV A, P3 ;Скопировать состояние ножек порта P3 в аккумулятор JB P3.4, Metka ;Если на 4 ножке порта P3 логическая ‘1’, то перейти на метку Чтение регистра - защелки осуществляется командами чтение - модификация - запись. Например: CPL P3.1 ;Проинвертировать сигнал на первой ножке порта P3 ORL P2,#56h ;Установить единичный сигнал на ножках 1,2,4 и 6 порта P2 ANL P3,#03h ;Установить нулевой сигнал на ножках 0 и 1 порта P3 |

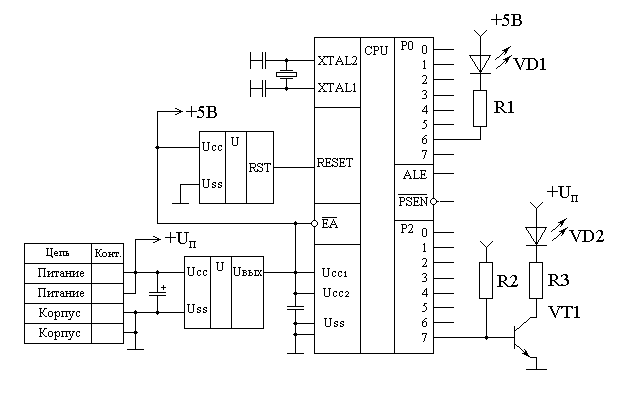

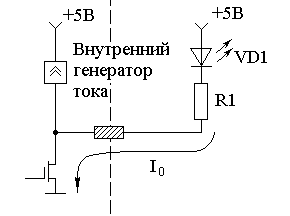

Порты микросхемы служат для управления внешними устройствами, подключенными к микроконтроллеру. Схема подключения простейших внешних устройств приведена на рисунке 2. Этот рисунок иллюстрирует особенности подключения индикаторов к параллельным портам микроконтроллера MCS-51.

Рисунок 2. Схема подключения светодиодных индикаторов к параллельному порту.

Присутствие в схеме мощного транзистора позволяет подключать к выводам порта светодиодные индикаторы непосредственно без усилителя мощности. Однако при этом необходимо следить за максимальной допустимой мощностью, рассеиваемой на микросхеме и напряжением, подаваемом на светодиод. Эквивалентная схема, на которой показан путь протекания выходного тока порта приведена на рисунке 3. Как видно из этой схемы именно этот ток используется для зажигания светодиода.

Рисунок 2. Эквивалентная схема подключения светодиодного индикатора к параллельному порту.

Для умощнения выводов порта можно применить транзисторный ключ, показанный на рисунке 2. Обратите внимание, что база транзистора подключена непосредственно к выводу порта. Это стало возможным только благодаря использованию в схеме порта генератора тока в верхнем плече выходного каскада (Схему подключения устройств к портам с TTL выходами можно посмотреть здесь). Если выходного тока достаточно для открывания транзисторного ключа, то резистор R2 не используется. Этот резистор подключается для увеличения базового тока транзисторного ключа. На максимальное значение тока через этот резистор накладываются те же ограничения, что и для непосредственного подключения светодиодного индикатора к выводам порта.

Микроконтроллеры предназначены для управления внешними устройствами, однако управлять напряжением на выходе параллельного порта микроконтроллера можно только при помощи программы, записанной в память программ. Какие напряжения необходимо подавать на выходы микросхемы зависят от схемы подключения индикатора. В приведённой на рисунке 2 схеме, для зажигания светодиода VD1, в шестой вывод порта P0 необходимо записать логический 0. Для зажигания светодиода VD2 необходимо в седьмой разряд порта P2 записать логическую единицу, а для его гашения – логический ноль.

Для записи числа в порт (изменения потенциалов на ножках микросхемы) можно воспользоваться командами с байтовой адресацией:

MOV (пересылка), например

MOV P2, #56h ;Установить единичный сигнал на ножках 1,2,4 и 6 порта P2

;и нулевой потенциал на ножках 0,3,5 и 7

MOV P1, #01110011b ;Выдать на все восемь выводов порта P1 число 011100112

MOV P3, A ;Выдать на все восемь выводов содержимое аккумулятора

ANL (логическое 'И'), например

ANL P1, #11110011b ;выдать низкий потенциал на ножках P1.2 и P1.3

XRL (исключающее 'ИЛИ'), например

XRL P3, #01000100b ;инвертировать состояние ножек P3.2 и P3.6

ORL (логическое 'ИЛИ'), например

ORL P1, #00001100b ;выдать высокий потенциал на ножках P1.2 и P1.3

Эти команды изменяют потенциал сразу на нескольких выводах порта. Кроме того, для изменения потенциалов на ножках микросхемы, можно воспользоваться командами с битовой адресацией:

MOV (пересылка), например

MOV P1.2, C ;выдать содержимое бита переноса через 2-й бит порта P2

CPL (инверсия), например

CPL P1.2 ;проинвертировать второй бит порта P2

SETB (установить бит), например

SETB P2.3 ;выдать высокий потенциал на 3-й ножке порта P2

CLR (сбросить бит), например

CLR P2.3 ;выдать низкий потенциал на 3-й ножке порта P2

При записи в разряд порта (в триггере Т) логического '0' выходной транзистор открывается и на выводе микросхемы появляется низкий потенциал, изменить который извне невозможно. Поэтому при опросе ножки микросхемы входная информация в этом случае всегда будет восприниматься как логический '0' независимо от состояния выходов внешних устройств. Если в указанный разряд записать логическую '1', то выходной транзистор закрывается и на выводе микросхемы появляется высокий потенциал за счет генератора тока. Он может извне изменен на нулевой потенциал (замыканием этой ножки микросхемы на корпус). В этом случае, считываемая микроконтроллером информация, будет соответствовать информации на выходе внешнего устройства. Поэтому, перед тем как осуществить ввод информации по какому-либо выводу порта, соответствующий разряд необходимо настроить на ввод - записать в него логическую '1'.

По той же причине при настройке выводов порта на выполнение альтернативных функций в соответствующие разряды должны быть записаны логические '1'.

Кроме работы в качестве обычных портов ввода - вывода, внешние выводы портов Р0 .. Р3 могут выполнять ряд дополнительных (альтернативных) функций:

Порт P0 может быть использован для организации шины данных при работе микроконтроллера с внешней памятью данных или программ, при этом через него выводится младший байт адреса A0 - A7, выдается из микроконтроллера или принимается в микроконтроллер байт данных. Во время доступа к внешней памяти во все триггеры - защелки порта P0 аппаратно записываются "1" (т.е. содержимое порта теряется). Кроме того, через порт P0 передаюься данные при программировании внутреннего ППЗУ, и читается содержимое внутренней памяти программ при работе с программатором. При сбросе микросхемы во все разряды порта записываются '1'. Схема порта P0 отличается от всех других портов тем, что у этого порта нет внутреннего генератора тока. Поэтому при работе с этим портом приходится подключать внешние резисторы.

Схема использования порта P0 в качестве шины данных приведена на рисунке 3.

Рисунок 3. Использование порта P0 в качестве шины данных.

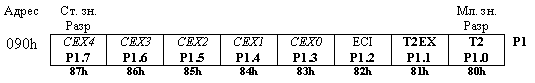

Порт P1 может быть использован для чтения внутренней памяти программ или для передачи младшего байта адреса при программировании внутреннего РПЗУ. В младших моделях микроконтроллера семейства других альтернативных функций у порта P1 нет. При сбросе микросхемы во все разряды порта записываются '1'.

P1.0 T2 -внешний вход таймера/счетчика 2 P1.1 T2EX -вход управления перезагрузки/захвата таймера P1.2 ECI - внешний вход набора программируемых счетчиков (РСА) P1.3 CEX0 -внешний вход/выход для вывода ШИМ или сравнения/захвата модуля 0 P1.4 CEX1 -внешний вход/выход для вывода ШИМ или сравнения/захвата модуля 0 P1.5 CEX2 -внешний вход/выход для вывода ШИМ или сравнения/захвата модуля 0 P1.6 CEX3 -внешний вход/выход для вывода ШИМ или сравнения/захвата модуля 0 P1.7 CEX4 -внешний вход/выход для вывода ШИМ или сравнения/захвата модуля 0

Примечание: альтернативные функции, выделенные:

жирным подчеркнутым текстом - присутствуют во всех микросхемах

жирным текстом - отсутствуют в микросхемах 8051,8031, КР1816ВЕ31, КР1816ВЕ51, КР1816ВЕ751 КР1830ВЕ31, КР1830ВЕ51, КР1830ВЕ751;

курсивом - присутствуют только в микросхемах 8Х51FA, FB, FC и GB