- •Подати план виконання апаратної частини цифрового проекту. Зазначити на цьому плані етапи, що автоматизуються, перелічити переваги виконання цих проектів із застосуванням сапр

- •Роз'яснити призначення і функції апаратури керування тактовими імпульсами в пліс Віртекс фірми Xilinx

- •Розробити структуру одноциклової risc машини з архітектурою dlx рівня машинних інструкцій та прокоментувати цю структуру

- •Подати типову структуру системи на кристалі та роз’яснити її.

- •Розробити структуру одноциклової risc машини з архітектурою dlx рівня машинних інструкцій та прокоментувати цю структуру

- •.Подати план виконання апаратної частини цифрового проекту. Зазначити на цьому плані етапи, що автоматизуються, перелічити переваги виконання цих проектів із застосуванням сапр

- •Подати план виконання апаратної частини цифрового проекту. Зазначити на цьому плані етапи, що автоматизуються, перелічити переваги виконання цих проектів із застосуванням сапр

- •Подати план виконання апаратної частини цифрового проекту. Зазначити на цьому плані етапи, що автоматизуються, перелічити переваги виконання цих проектів із застосуванням сапр

Білет №1

Подати план виконання апаратної частини цифрового проекту. Зазначити на цьому плані етапи, що автоматизуються, перелічити переваги виконання цих проектів із застосуванням САПР

Пояснити наступний витяг з протоколу синтезу пристрою, що розглядається в питанні № 2.

Design Statistics

# IOs : 5

Cell Usage :

# BELS : 2

# LUT2 : 1

# LUT4 : 1

# IO Buffers : 5

# IBUF : 4

# OBUFT : 1

Ідентифікувати пристрій, поданий наступною VHDL моделлю. Подати коментарі після позначень -- і технологічну схему (для синтезованого пристрою).

-- під’єднання бібліотек

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

-- означення входів і виходів мікросхеми

entity constant_ex is

port (OPCODE : in STD_LOGIC_VECTOR(1 downto 0); -- код операції

A, B : in STD_LOGIC; -- операнди

OP_OUT : out STD_LOGIC); -- результат

end constant_ex;

-- означення констант, внутрішніх змінних проекту і функцій мікросхеми

architecture BEHAV of constant_ex is

-- уведення символічних позначень комбінацій кодів (для зручності запровадження змін)

constant ZERO : STD_LOGIC_VECTOR (1 downto 0) := "00"; -- на виході завжди нуль

constant A_AND_B: STD_LOGIC_VECTOR (1 downto 0) := "01"; -- на виході логічний

добуток

constant A_OR_B : STD_LOGIC_VECTOR (1 downto 0) := "10"; -- на виході логічна сума

constant ONE : STD_LOGIC_VECTOR (1 downto 0) := "11"; -- на виході завжди одиниця

-- подано перелік операцій, що виконує пристрій асинхронно, без використання

-- тактового імпульсу; отже, це комбінаційний операційний пристрій, а саме: спрощений АЛП

begin

-- АЛП змінює вихід лише за умови зміни коду операції і/або аргументів А,В

process (OPCODE, A, B)

begin

if (OPCODE = A_AND_B) then OP_OUT <= A and B;

elsif (OPCODE = A_OR_B) then OP_OUT <= A or B;

elsif (OPCODE = ONE) then OP_OUT <= '1';

else OP_OUT <= '0';

-- усі випадки розписано, чим заборонено непрямий,непотрібний синтез защіпки

end if;

end process;

end BEHAV;

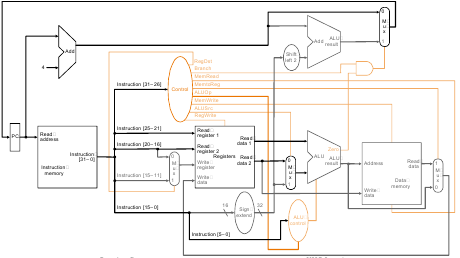

Розробити структуру одноциклової RISC машини з архітектурою DLX рівня машинних інструкцій та прокоментувати цю структуру

Білет №2

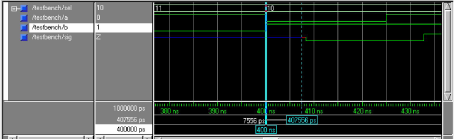

Проаналізувати результати часового симулювання поведінки однорозрядного D-регістра (з питання № 25), що надані наступною часовою діаграмою.

.Ідентифікувати невідомий пристрій за наданою поведінковою VHDL моделлю. Подати коментарі (після позначень --). Навести RTL схему синтезованого пристрою.

-- під’єднання бібліотек

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

-- означення входів і виходів (інтерфейс)

ENTITY add IS

PORT (CI: IN STD_LOGIC;

A, B: IN STD_LOGIC;

SUM: OUT STD_LOGIC;

CO: OUT STD_LOGIC);

END add;

-- алгоритм

ARCHITECTURE archadd OF add IS

BEGIN

SUM <= A XOR B XOR CI; -- однорозрядна сума

CO <= (A and B) or (A and CI) or (B and CI); -- вихідний перенос

END archadd;

Розпізнати і роз’яснити структуру системи, надану рис.

.Роз'яснити призначення і функції апаратури керування тактовими імпульсами в ПЛІС Xilinx Virtex

Білет №3

Ідентифікувати невідомий пристрій за наступною поведінковою VHDL моделлю. Подати коментарі до VHDL моделі (після позначень --) та RTL схему синтезованого пристрою (ПЛІС Virtex-2).

library IEEE;-- розділ бібліотек

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

library unisim; ; -- бібліотека, що містить симуляційні моделі елементів ПЛІС, що тут називають віртуальними компонентами

use unisim.vcomponents.all; -- такі елементи ПЛІС називають віртуальними компонентами

entity lvds is

Port ( i : in std_logic; --прямий вхід

ib : in std_logic; -- інверсний вхід

tri: in std_logic; -- керування тристабільним станом (на виході всього пристрою)

o : out std_logic; --прямий вихід

ob : out std_logic); -- інверсний вихід

end lvds;

architecture low_level of lvds is

component IBUFDS_LVDS_25

port( I : in std_logic; --прямий диференційний вхід

IB : in std_logic; --інверсний диференційний вхід

O : out std_logic ); --бістабільний вихід

end component;

component OBUFTDS_LVDS_25 -- бібліотечний елемент, що формує вихідний диференційний сигнал з вхідного двохстабільного

port(

I : in std_logic;

T : in std_logic; -- керування високостабільним (третім станом на обидвох диференційних виходах прямому O та інверсному ОВ

O : out std_logic;

OB : out std_logic

);

end component;

signal wire_in : std_logic;

signal wire_out : std_logic;

begin

U0: wire_in <= not wire_out;

U1: IBUFDS_LVDS_25--інсталяція lvds приймача

port map ( I => i, -- прямий вхід ззовні до LVDS вхідного буфера

IB => ib, -- інверсний вхід ззовні до LVDS вхід. буфера

O => wire_out –- вхідний сигнал до логіки ПЛІС

);

U2: OBUFTDS_LVDS_25 --інсталяція lvds передавача

port map (

I => wire_in, -- вхід до вихідного буфера від накристальної ПЛІС логіки

T => tri, -- керування третім станом на вихадних контактах

-- вихідного буфера lvds

O => o, -- P-канальний вихід буфера LVDS

OB => ob -- N-канальний вихід буфера LVDS

);

end low_level;

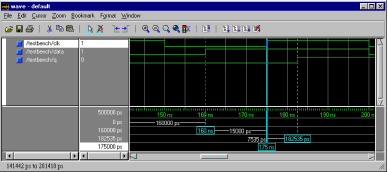

Пояснити надану часову діаграму симулювання поведінки пристрою, поданого питаннм № 1

Означити і прокоментувати послідовність виконання операцій логічного програмування ПЛІС на основі VHDL моделювання в САПР Xilinx ISE WebPack

Подати план виконання апаратної частини цифрового проекту. Зазначити на цьому плані етапи, що автоматизуються, перелічити переваги виконання цих проектів із застосуванням сапр

Білет №4

Навести і прокоментувати експертні правила комп’ютерного дизайну.

Ідентифікувати пристрій, поданий наступною VHDL моделлю, подати коментарі після позначення -- . Навести технологічну схему результату синтезу моделі.

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity clock_enable is

port (IN1,IN2,DATA,CLOCK,LOAD: in STD_LOGIC;

DOUT: out STD_LOGIC);

end clock_enable;

architecture BEHAV of clock_enable is

signal ENABLE: STD_LOGIC;

begin

-- формування сигналу дозволу як логічного добутку

ENABLE <= IN1 and IN2 and LOAD;

-- защіпування входу на виході

EN_PR: process (ENABLE,DATA,CLOCK)

begin

if (CLOCK'event and CLOCK='1') then –- на фронті тактового імпульсу

if (ENABLE='1') then –- коли є дозвіл, тоді

DOUT <= DATA; -- переслати дані на вихід

end if;

end if;

end process;

end BEHAV;

Ідентифікувати на основі наданого фрагменту VHDL моделі компонент зі складу одноциклової RISC машини. Подати (після позначень --) коментарі до фрагменту моделі. Структуру машини надає рис.

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_ARITH.all;

entity x_chip is

port( -- прокоментувати всі сигнали цього порту

Op : in std_logic_vector(5 downto 0); -- код операції з інструкції

RegDst : out std_logic; -- мікронаказ вибору номера регістра призначення

ALUSrc : out std_logic; -- мікронаказ вибору оперенда для АЛП

MemtoReg : out std_logic; -- мікронаказ запису до рег. Файлу виходу пам’яті

RegWrite : out std_logic; -- мікронаказ запису до регістрового файлу

MemWrite : out std_logic; -- мікронаказ запису до пам’яті даних

Branch : out std_logic); -- ознака виконання умовного переходу

end x_chip;

Порівняно з минулим, визначити місце і можливості ПЛІС на сучасному етапі розвитку техніки і технологій проектування апаратних комп’ютерних засобів

Білет №5

Ідентифікувати пристрій, поданий наступною VHDL моделлю. Подати технологічну схему результату синтезу пристрою. Надати коментарі до VHDL моделі (після позначень --).

library IEEE;

use IEEE.std_logic_1164.all;

-- пристрій має чотири бітових входи: дані,швидкий і повільний такт, селектор, бітовий вихід QOUT

entity x_device is

port (DATA, SEL: in STD_LOGIC;

SLOW_CLOCK, FAST_CLOCK: in STD_LOGIC;

DOUT: out STD_LOGIC);

end x_device;

architecture XILINX of x_device is

-- уведено два внутрішніх сигнали

signal CLOCK: STD_LOGIC;

signal CLOCK_GBUF: STD_LOGIC;

-- залучено відомий системі компонент BUFGS – так званий вторинний

-- глобальний буфер, що є внутрішним підсисювачем вторинних тактових сигналів;

-- цей компонент має один бітовий вхід І, на який надсилають такт, що треба електрично

-- підсилити, та один бітовий вихід О, з якого забирають підсилені такти для

-- використання в межах кристалу (матриці ПЛІС)

component BUFGS

port (I: in STD_LOGIC;

O: out STD_LOGIC);

end component;

begin

Clock_MUX: process (SEL)

begin

if (SEL = '1') then

CLOCK <= FAST_CLOCK;

else

CLOCK <= SLOW_CLOCK;

end if;

end process;

-- наступним оператором виконується підсилення проселектованого

-- вхідного такту CLOCK; при цьому, електрично підсилений такт, що споживається в

-- кристалі,отримує назву CLOCK_GBUF; він пересилається в кристалі швидкими металевими

-- лініями з мінімальною і передбачуваною затримкою

GBUF_FOR_MUX_CLOCK: BUFGS

port map (I => CLOCK,

O => CLOCK_GBUF);

-- нарешті,наступним і останнім оператором процесу із позначкою

-- “інформаційний шлях” означено функцію формування сигналу на виході, а саме:

-- сигнал на виході DOUT відслідкує вхідний сигнал DATA тоді, коли набігає зростаючий

-- фронт електрично підсиленог такту CLOCK_GBUF

Data_Path: process (CLOCK_GBUF, DATA)

begin

if (CLOCK_GBUF'event and CLOCK_GBUF='1') then

DOUT <= DATA;

end if;

end process;

end XILINX;

Пояснити текст, що є фрагментом звіту САПР Xilinx WebPack про результат фази трансляції етапу імплементації (ідентифікованого в питанні 2) пристрою.

ERROR:NgdBuild:604 - logical block 'GBUF_FOR_MUX_CLOCK' with type 'BUFGS' could

not be resolved. A pin name misspelling can cause this, a missing edif or ngc

file, or the misspelling of a type name. Symbol 'BUFGS' is not supported in target 'spartan3a'

Розробити структуру одноциклової RISC машини з архітектурою DLX рівня машинних інструкцій та прокоментувати цю структуру Розробити VHDL модель однорозрядного D-регістра, що має інформаційний вхід DATA, тактовий вхід CLK і інформаційний вихід Q. Подати коментарі до моделі (після позначень --). Навести технологічну схему синтезованого регістра

Білет №6

Ідентифікувати компонент одноциклової RISC машини (з архітектурою DLX на рівні машинних інструкцій) за наданою VHDL моделлю. Подати коментарі до VHDL моделі (після позначень --).

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_ARITH.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

entity X_chip is

port( clock : in std_logic; -- такт

reset : in std_logic; -- скид

PCsrc : in std_logic; -- вибір джерела для РС: наступна або стрибкова адреса

Branch_Address : in std_logic_vector(7 downto 0); -- стрибкова адреса

PCview : out std_logic_vector(7 downto 0); -- для спостереження

Instruction : out std_logic_vector(31 downto 0); -- код інструкції

NPC : out std_logic_vector(7 downto 0)); -- наступне значення програмного лічильника

end X_chip;

architecture behav of X_chip is

signal PC : std_logic_vector(7 downto 0);

signal PC_Input : std_logic_vector(7 downto 0); -- на вході програмн. лічильника

signal NPC_temp : std_logic_vector(7 downto 0);

constant rom0 : std_logic_vector(31 downto 0) :=x"8c040000"; -- lw $4, 0($0)

constant rom1 : std_logic_vector(31 downto 0) := x"8c050001"; -- lw $5, 1($0)

constant rom2 : std_logic_vector(31 downto 0) := x"00852020"; -- add $4, $4, $5

constant rom3 : std_logic_vector(31 downto 0) := x"ac040000"; -- sw $4, 0($0)

constant rom4 : std_logic_vector(31 downto 0) := x"1080fffb"; -- beq $4, $0, -20

constant rom5 : std_logic_vector(31 downto 0) := x"1084ffff"; -- beq $4, $4, -4

constant rom6 : std_logic_vector(31 downto 0) := x"00000025"; -- or $0, $0, $0

constant rom7 : std_logic_vector(31 downto 0) :=x"00000025"; -- or $0, $0, $0

begin

PCview <= PC;

NextAddr:

NPC_temp(7 downto 2) <= PC(7 downto 2) + 1;

NPC_temp(1 downto 0) <= b"00";

NPC <= NPC_temp;

JumpAddrMux:

PC_Input <= Branch_Address when PCsrc = '1' else NPC_temp;

PC1: process

begin

wait until (clock'event) and (clock='1');

If reset='1' then

PC <= x"00"; -- скид

else

PC <= PC_Input; -- зарахування обчисленого значення адреси інструкції

end if;

end process;

IM: process (PC)

begin

case PC(7 downto 2) is

when "000000" => instruction <= rom0;

when "000001" => instruction <= rom1;

when "000010" => instruction <= rom2;

when "000011" => instruction <= rom3;

when "000100" => instruction <= rom4;

when "000101" => instruction <= rom5;

when "000110" => instruction <= rom6;

when "000111" => instruction <= rom7;

when others => instruction <= x"00000000";

end case;

end process;

end behav;

Подати послідовність кроків виконання цифрового проекту на базі ПЛІС/ПЛМ. Зазначити переваги автоматизованого виконання проектних робіт за допомогою САПР.

Подати послідовність виконання проекту в САПР Xilinx WebPack (+ симулятор ModelSim або вбудований до САПР симулятор).

Експертні правила комп’ютерного дизайну

Білет №7

Пояснити правило інсталювання компонент VHDL проекту на основі наданого фрагменту кода.

ARCHITECTURE struct OF root IS

COMPONENT leaf

PORT (

clk,data : in std_logic;

Qout : out std_logic);

END COMPONENT;

BEGIN

u1 : leaf

PORT MAP ( clk => clk, data => d_in(0), Qout => q_out(0)); . . .

Ідентифікувати пристрій, наданий VHDL моделлю. Надати коментарі до моделі (після позначень --). Пояснити часові діаграми, отримані часовою симуляцією цієї моделі (ПЛІС Спартан-2Е фірми Xilinx).

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

entity mux_tbuf is

port ( SEL: in STD_LOGIC_VECTOR (1 downto 0); -- по одному біту вибору на кожний вхід

A,B: in STD_LOGIC; -- бітові входи мультиплексора

SIG: out STD_LOGIC); -- бітовий вихід мультиплексора

end mux_tbuf;

architecture data_flow of mux_tbuf is

begin

SIG <= A when (SEL(0)='0') else 'Z';

SIG <= B when (SEL(1)='0') else 'Z'; -- на вихід переслати або В,

end data_flow;

Результати часового симулювання функціонування пристрою подано наступною часовою діаграмою.