- •Лабораторний практикум

- •Загальні методичні вказівки

- •Технології оперативної пам'яті

- •1.3 Постановка завдання

- •1.5 Контрольні запитання

- •2.3 Постановка завдання

- •2.5 Контрольні запитання

- •3.3 Постановка завдання

- •Основні риси risc-процесорів

- •Risc-процесори 3-го покоління

- •Структура процесорів Alpha: 21064, 21264

- •Порівняльні характеристики Alpha 21164 і 21264

- •4.3 Постановка завдання

- •Паралельна обробка даних на еом

- •Закон Амдала

- •5.3 Постановка завдання

- •5.5 Контрольні запитання

- •Лабораторна робота №6 сучасна архітектура обчислювальних систем

- •6.1 Мета роботи

- •6.2 Теоретичні відомості

- •Vliw архітектура

- •Архітектура ia-64

- •Опис ia-64

- •6.3 Постановка завдання

- •Лабораторна робота №7

- •7.3 Постановка завдання

- •7.5 Контрольні запитання

- •Лабораторна робота №8 визначення швидкодії обчислювальної системи

- •8.1 Мета роботи

- •8.2 Теоретичні відомості

- •Порівняння за швидкістю процесора обчислювальної системи

- •Оцінка обчислювальної системи за тестами

- •Приклади тестів швидкодії/ефективності обчислювальних систем

- •Рекомендації щодо виконання роботи

- •8.3 Постановка завдання

- •8.5 Контрольні запитання

- •Перелік рекомендованих джерел

- •В.Г. Хорошевский. Архитектура вычислительных систем/ в.Г. Хорошевский. – м.: мгту им. Баумана,2008 - 530 с.

2.3 Постановка завдання

Розробити алгоритми організації паралельної обробки даних за допомогою конвеєрів команд і суперскалярності.

Написати програму для організації паралельної обробки даних за допомогою конвеєрів команд і суперскалярності.

Провести тестування написаної програми.

На основі проведеного дослідження зробити висновки щодо ефективності того чи іншого коду залежно від особливостей архітектури ЦП.

2.4 Зміст звіту

мета роботи;

теоретичні відомості;

тексти програм та відповідне програмне відображення;

результати обчислень на ЕОМ;

висновок.

2.5 Контрольні запитання

Які блоки складають конвеєр МП 80286?

Який блок і чому був доданий в конвеєр МП Intel-486?

Що розуміють під суперскалярною архітектурою?

Які способи обробки даних об'єднує термін "динамічного виконання програми"?

У чому полягає внутрішня RISC-архитектура ЦП Pentium Pro?

У роботі якого процесора спостерігається відхилення від принципів фон Неймана? У чому це виявляється?

У чому полягає перевага використання подвійної незалежної шини?

Що нового з'явилося в архітектурі процесора Pentium III в порівнянні з Pentium MMX?

Які особливості має Net Burst-архітектура?

ЛАБОРАТОРНА РОБОТА №3

СПІВПРОЦЕСОРИ

3.1 Мета роботи

Метою роботи є ознайомлення з основними принципами організації співпроцесорів, здобуття умінь і навиків, необхідних для налагодження роботи систем із співпроцесорами.

Триваліть роботи – 2 години

3.2 Теоретичні відомості

Співпроцесори. Способи обміну інформацією між ЦП і співпроцесором

Співпроцесор - це спеціалізована інтегральна схема, яка працює разом з ЦП, але менш універсальна. На відміну від ЦП, співпроцесор не має лічильника команд. Співпроцесор призначений для виконання специфічного набору функцій, наприклад: виконання операцій з дійсними числами - математичний співпроцесор, підготовка графічних зображень і тривимірних сцен - графічний співпроцесор, цифрова обробка сигналів - сигнальний співпроцесор і ін.

Використання співпроцесорів з різною функціональністю дозволяє вирішувати проблеми широкого кола:

обробка економічної інформації;

моделювання;

графічні перетворення;

промислове управління;

системи числового управління;

роботи;

навігація;

збір даних і ін.

Можна виділити два способи обміну інформацією між ЦП і співпроцесором:

пряме з'єднання вхідних і вихідних портів (ЦП має спеціальний інтерфейс для взаємодії із співпроцесором);

з обміном через пам'ять (обмін інформацією між ЦП і співпроцесором відбувається завдяки доступу співпроцесора до оперативної пам'яті через системну магістраль).

Математичний співпроцесор: основні функції

Один з найбільш поширених типів співпроцесорів - математичний співпроцесор. Математичний співпроцесор призначений для швидкого виконання арифметичних операцій з плаваючою крапкою, обчислення тригонометричних і інших трансцендентних функцій (tg, arctg, log ...).

Більшість сучасних математичних співпроцесорів для представлення дійсних чисел використовують стандарт IEEE 754-1985 "IEEE1) Standard for Binary Floating-Point Arithmetics". Старший розряд двійкового представлення дійсного числа завжди кодує знак числа. Остання частина розбивається на дві частини: експоненту і мантису. Дійсне число обчислюється як: (-1)S·2E·M, де S - знаковий біт числа, E - експонента, M - мантиса. Якщо 1 M<2, то таке число називається нормалізованим. При зберіганні нормалізованих чисел співпроцесор відкидає цілу частину мантиси (вона завжди 1), зберігаючи лише дробову частину. Експонента кодується із зрушенням на половину розрядної сітки, таким чином, удається уникнути питання про кодування знаку експоненти. Тобто при 8-бітовій розрядності експоненти код 0 відповідає числу -127, 1 - числу -126, ..., 255 числу +126 (експонента обчислюється як код 127).

Стандарт IEEE-754 визначає три основні способи кодування (типа) дійсних чисел.

Таблиця 3.1 - Типи (способи кодування) дійсних чисел

Тип

|

Діапазон значень (по модулю) |

Двійкове представлення |

Суттєве ординарної точності (single precision) - 32 біт |

1,18·10-38... 3,40·1038

|

|

Суттєве подвійній точності (double precision) - 64 біт |

2,23·10-308... 1,79·10308

|

|

Продовження таблиці 3.1

Суттєве розширеної точності (extended precision) - 80 біт

|

3,37·10-4932... 1,18·104392

|

|

Наведемо приклад кодування дійсного числа 178,625:

178,62510 = 128 + 32 + 16 + 2 + 0,5 + 0,125 =

= 1·27 + 0·26 + 1·25 + 1·24 + 0·23 + 0·22 + 1·21 + 0·20 +

+ 1·2-1 + 0·2-2 + 1·2-3 = 10110010,1012

Для представлення цього числа відповідно до IEEE-754 його потрібно нормалізувати (привести в експоненціальний вигляд):

1,78625E102 = 1,0110010101E2111

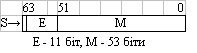

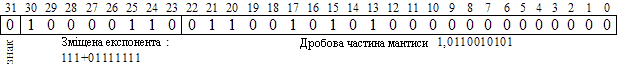

У форматі дійсного числа одинарної точності воно буде представлено так:

Рисунок 3.1 – Предаставлення дійсного числа

Слід зазначити, що не всі можливі комбінації такого представлення відповідають нормалізованим дійсним числам. У загальному випадку вся сукупність двійкових комбінацій ділиться на наступні класи (таблиця. 3.2):

нормалізовані дійсні числа із знаком;

денормалізовані дійсні числа із знаком;

нуль із знаком;

нескінченність із знаком;

нечисла (NAN - not а number).

Таблиця 3.2 - Представлення чисел і нечисел на прикладі IEEE-754 single precision

Тип

|

Двійковае представлення

|

Нуль із знаком

|

|

Денормалізоване дійсне число із знаком

|

|

Нормалізоване дійсне число із знаком

|

|

Нескінченність із знаком

|

|

Нечисло

|

|

Математичні співпроцесори фірми Intel

Сучасні процесори архітектури IA-32 містять блок операцій з дійсними числами (Floating Point Unit - FPU). Функціонування цього блоку багато в чому засноване на архітектурі першого представника сімейства математичних співпроцесорів Intel - 8087.

Випуск чергового покоління ЦП фірми Intel ознаменувався впровадженням блоку речової арифметики в структуру ЦП. Першим таким представником сімейства процесорів став i486DX.

У п'ятому поколінні процесорів інтеграція блоку FPU в суперскалярну архітектуру дозволила значно підвищити ефективність виконання операцій з дійсними числами. Блок FPU може виконувати одну операцію з плаваючою крапкою в кожному такті або ж отримувати і одночасно виконувати 2 команди з плаваючою крапкою, однією з яких має бути команда обміну. Команди з плаваючою крапкою проходять по цілочисельному конвеєру (зазвичай лише по U-конвейеру - 5 рівнів) і передаються на виконавчі рівні конвеєра FPU (3 рівні). В цілому ж, не дивлячись на те, що блок FPU інтегрований в центральний процесор, цей блок працює незалежно і одночасно з пристроєм цілочисельних обчислень.

Подальший розвиток цього сімейства супроводився доповненням набору команд блоку FPU спеціальними функціональними підмножинами: MMX, SSE, SSE2.

В цілому базова програмна модель всіх перерахованих співпроцесорів і блоку FPU в IA-32 схожа: регістровий стек (вісім 80-бітових регістрів R0-R7), слово тегов, регістр управління, регістр стану, покажчик команди і покажчик даних.

. Для зберігання даних в співпроцесорі призначені регістри R0-R7. Ці регістри організовані в стек, і доступ до них проводиться відносно вершини стека - ST. Номер регістра, відповідного вершині стека, зберігається в регістрі стану (поле TOS). Як і в ЦП, стек співпроцесора зростає до регістрів з меншими адресами. Команди, які проводять запам'ятовування і витягання із стека, передають дані з поточного регістра ST, а потім проводять інкремент поля TOS в регістрі стану. Багато команд співпроцесора допускають неявне звернення до вершини стека, ST, що позначається, або ST(0). Для вказівки i-го регістра відносно вершини використовується позначення ST(i), де I = 0,:,7. Наприклад, якщо поле TOS регістра стану містить значення 0112 (вершиною стека є регістр R3), то команда FADD ST,ST(2) підсумовує вміст регістрів R3 і R5. Стекова організація спрощує програмування підпрограм, допускаючи передачу параметрів в регістровому стеку співпроцесора.

Старший байт регістра стану містить:

біт зайнятості B (біт 15), що сигналізує, чи вільний співпроцесор (B=0) або зайнятий виконанням чисельної команди (B = 1). Команди співпроцесора, які використовують регістровий стек, вимагають, аби перед початком їх виконання співпроцесор не був зайнятий. У FPU цей біт дублює значення прапора сигналізації особливого випадку.

поле TOS "Тор-of-the-stack" (біти 11-13), яке містить номер регістра, що є логічною вершиною стека. При приміщенні в регістровий стек нового числа це значення зменшується. Якщо це поле досягає значення 0, можливі дві ситуації: станеться заворачивание стека на регістри з великими номерами (тобто R7) або, якщо згортування призведе до затирання незбереженого значення, виникне особливий випадок співпроцесора "переповнювання стека".

4 біти коду умови (біти 14, 10, 9, 8), аналогічні прапорцям стану FLAGS в IA-32, що відображають результат арифметичних операцій. Ці прапорці можуть бути використані для умовних переходів.

Молодший байт регістра стану містить прапорці особливих випадків співпроцесора: переповнювання стека, втрата точності, втрата значущих розрядів, чисельне переповнювання, ділення на нуль, денормалізація, недійсна операція. Якщо відповідний особливий випадок виник і не був замаскований (у слові управління), це приведе до генерації центральним процесором особливого випадку співпроцесора (#16).

Молодше слово регістра управління містить біти масок особливих випадків. Співпроцесор допускає індивідуальне маскування особливих випадків. Якщо той або інший особливий випадок замаскований, при виникненні відповідної ситуації співпроцесор виконує деякі заздалегідь визначені внутрішні дії, які частенько прийнятні для більшості вживань. Наприклад, якщо замаскований особливий випадок ділення на нуль, то виконання операції 85,32/0 дасть результат + ∞.

Старше слово регістра управління містить два поля: управління точністю РС (біти 8 і 9) і управління округленням RC (біти 10 і 11). Біти управління точністю можна використовувати для пониження точності обчислень. За умовчанням використовується розширена точність (РС = 112), можна також використовувати подвійну точність (РС = 102) і одинарну точність (РС = 002) за стандартом IEEE-754.

Якщо результат чисельної операції не може бути точно представлений у вибраному форматі, співпроцесор виконує округлення відповідно до поля RC (таблиця. 3.3). За умовчанням RC = 00. У прикладах в таблиці. 7.3 зроблена спроба представити числа +2,23 і +2,05 у вигляді двійкових дійсних чисел з 3-бітовою дробовою частиною мантиси. У цьому форматі не можна підібрати точне двійкове значення для цих чисел. Найближчі до них уявні числа - +2,00 (+1,000E21) і +2,25 (+1,001E21).

Таблиця 3.3 - Режими округлення співпроцесорів Intel x87

RRC

|

Режим

|

Приклад 1 1,000E21<2,23E100 < 1,001E21 -1,001E21<-2,23E100 < -1,000E21 |

Приклад 2 1,000E21<2,05E100 < 1,001E21 -1,001E21<-2,05E100 < -1,000E21 |

000 |

Округлення до найближчого (або парному) |

2,23E100≈1,001E21 -2,23E100≈-1,001E21 |

2,05E100≈1,000E21 -2,05E100≈-1,000E21 |

001 |

Округлення вниз (до ∞)

|

2,23E100≈1,000E21 -2,23E100≈-1,001E21 |

2,05E100≈1,000E21 -2,05E100≈-1,001E21 |

110 |

Округлення вгору (до +∞)

|

2,23E100≈1,001E21 -2,23E100≈-1,000E21

|

2,05E100≈1,001E21 -2,05E100≈-1,000E21

|

111 |

Округлення до нуля (усікання)

|

2,23E100≈1,000E21 -2,23E100≈-1,000E21 |

2,05E100≈1,000E21 -2,05E100≈-1,000E21 |

Регістр тегів містить 8 тегів - ознак, що характеризують вміст відповідного чисельного регістра співпроцесора. Тег може набувати наступних значень:

00 - у регістрі знаходиться дійсне число;

01 - нульове число в регістрі;

10 - недійсне число (нескінченність, денормалізоване число, нечисло);

11 - порожній регістр.

Співпроцесор використовує теги, аби визначити переповнювання або спустошення стека. Якщо при приміщенні в стек чергового числа опиниться, що декрементированный TOS вказує на непорожній регістр (відповідний тег не дорівнює 112), співпроцесор сигналізує про переповнювання стека. Якщо при витяганні із стека числа виявиться, що інкрементований TOS вказує на порожній регістр (відповідний тег дорівнює 112), співпроцесор сигналізує про спустошення стека.

Покажчик команд і покажчик даних містять логічні адреси (селектор сегменту і зсув) останньої команди і її операнда. (це 32-бітові регістри в 8087 і 80287 і 48-бітові - в 80387 і FPU). Ця інформація використовується обробником особливих випадків співпроцесора.

Для команд співпроцесора виділена група кодів, що починається з 11011ххх. У асемблерах мнемоніки команд співпроцесора починаються з "F": FADD (складання), FCOM (порівняння), FCOS (косинус), FDIV (ділення) і тому подібне

Паралельна робота ЦП і співпроцесора ставить перед програмістом проблеми синхронізації. Наприклад:

mem DW 0

:

FILD mem

INC mem

FSQRT

У даному прикладі, команда FILD перетворить 16-бітове ціле число в пам'яті у формат співпроцесора і зберігає його в ST, потім цілочисельна команда INC збільшує це значення на 1, після чого співпроцесор обчислює квадратний корінь ST (FSQRT).

Для зовнішніх співпроцесорів (8087, 80287, 80387) ЦП почне виконувати команду INC раніше, ніж співпроцесор закінчить FILD, а, отже, в стек співпроцесора може попасти невірне значення. Вбудований блок FPU в IA-32 позбавлений цього недоліку, оскільки ЦП відстежує звернення до пам'яті і не почне виконувати цілочисельну команду, якщо вона звертається до елементу пам'яті, з якою в даний момент працює блок FPU. Проте залишається невирішеною інша проблема. Якщо при виконанні інструкції FPU виникає ситуація, відповідна одному з незамаскованих особливих випадків, FPU припиняє виконання інструкції і сигналізує про особливий випадок. Проте відповідне виключення процесора буде викликано лише при черговому зверненні процесора до блоку FPU, а до цього моменту цілочисельний блок може змінити елемент пам'яті, значення якої привело до виключення, так що обробник виключення не зможе правильно інтерпретувати причину особливого випадку.

Описана ситуація говорить про необхідність використовувати в таких випадках засоби синхронізації. Наприклад, команда FWAIT припиняє роботу цілочисельного пристрою до тих пір, поки не буде завершена робота виконуваної співпроцесором інструкції або не буде викликано виключення, якщо при виконанні останньої інструкції FPU виник особливий випадок. Для цих же цілей можна використовувати будь-яку іншу інструкцію співпроцесора, окрім спеціальних "нечекаючих" інструкцій: FNINIT - скидання співпроцесора без чекання, FNSTCW/FNSTSW - збереження регістра управления/состояния без чекання, FNCLEX - скинути прапори особливих випадків без чекання, FNSAVE/FNSTENV - збереження стану (контексту) співпроцесора без чекання.

Таким чинно, наведений вище приклад слід переписати так:

FILD mem

FSQRT

INC mem