- •1.1. Развитие элементной базы вс.

- •1.2. Перспективы развития архитектур класса mpp (Massively Parallel Processor).

- •С хематический вид архитектуры с раздельной памятью

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Использование гиперкуба для реализации параллельных алгоритмов.

- •Решение задачи быстрой сортировки на гиперкубе

- •2.1. Матричные вс с ассоциативной обработкой инф-ции на примере вс pepe.

- •2.2 Супер-эвм фирмы Cray Research.

- •1. Три типа различных регистров:

- •2. Параллельная обработка на нескольких уровнях.

- •3. Организация памяти.

- •2.3 Понятие метакомпьютинга. Способы организации метакомпьютера. Основные решаемые задачи. Примеры использования метакомпьютера для решения сложных задач.

- •3.1Транспьютеры. Практическое применение

- •3.2 Способы распределения задач по процессорам в мультипроцессорных вс.

- •3.3 Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •4.1 Вс на основе систолических и волновых матриц

- •Волновая матрица.

- •4.2 Возм-ые пути постр-ия высокопроизв-ых вс, отличных от фоннеймановского типа. Понятие семантического разрыва между стр-рой вс и реал-ой прогр-ой.

- •Концепция неограниченного параллелизма. Выявление микро- и макропараллелизма в алгоритмах.

- •5.1 Анализ производ-ти мультипроцессорных вс. Коэффициент ускорения вычислений. Проблемы достижимости линейного роста производительности.

- •5.2 Редукционная машина «Алиса». Пример выполнения фрагмента программы.

- •Параллельная редукция

- •6.1 Развитие новых методов вычислений Японская программа по развитию вычислительной техники:

- •Основной язык: Prolog

- •6.2 Показатели качества функционирования вс. Критерий Гроша. Критерий Минского. Двухпараметрический критерий. Проблемы достижения линейного роста производительности вс.

- •7.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •7.3 Перспективы развития vpp (Vector Parallel Processor)

- •8.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •8.2 Особенности перехода к параллельным вычислениям. Проблемы организации параллельных вычислений.

- •9.1 Сравнительный анализ режимов и алгоритмов обработки информации в вс Сравнительные возможности двух методов организации параллельных вычислений: метод конвейеризации и метод параллелизма.

- •9.2 Принцип вычислений на основе управления потоком данных. Машины потоков данных (мпд). Архитектура. Достоинства и недостатки мпд.

- •Структура машины потоков данных. Данные хранятся в пакетах данных – в активных ячейках памяти. Ба – блок арифметический. Бл – блок логический. В активной памяти находятся пакеты, готовые к выполнению.

- •Функционирование машин потоков данных.

- •Организация сети передачи пакетов в мпд.

- •Достоинства мпд.

- •Недостатки мпд.

- •Обработка структур в мпд.

- •Структура мпд для обработки структур.

- •Структура устройства хранения и обработки.

- •9.3 Реализация фундаментальных вычислительных алгоритмов в матричной сети процессоров.

- •Решение задач линейной алгебры на матричной сети процессоров

- •10.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •10.2 Принцип вычислений на основе управления потоком данных. Машины потоков данных (мпд). Архитектура. Достоинства и недостатки мпд.

- •Данные хранятся в пакетах данных – в активных ячейках памяти. В активной памяти находятся пакеты, готовые к выполнению.

- •10.3 Принцип «разделяй и властвуй» и его использование для повышения эффективности выполнения вычислительных алгоритмов в сетях процессоров

- •11.1 Абстрактная архитектура вс. Основные модули и интерфейсы

- •Арифметический и командный конвейер

- •11.2 Особенности перехода к параллельным вычислениям. Проблемы организации параллельных вычислений.

- •11.3 Современные тесты для оценки производительности вс.

- •12.1 Диаграмма выполнения команды в машине фон Неймана. «Узкие места» при выполнении команды в последовательной вс. Методы устранения «узких» мест.

- •12.2 Редукционная g-машина. Пример выполнения фрагмента программы.

- •1. Три типа различных регистров:

- •2. Параллельная обработка на нескольких уровнях.

- •3. Организация памяти.

- •13.1 Арифметический и командный конвейер.

- •13.2 Организация тэговой памяти и оценка ее эффективности на примере мультипроцессорной вс Эльбрус.

- •Независимость программных средств от обрабатываемых данных. Программные средства реализованы только на логический уровень, поэтому:

- •Разработка высокопроизводительных систем класса мпд на основе ассоциативной памяти.

- •14.1. Способы выбора количества уровней совмещения (ступеней) в командном конвейере.

- •Тип решаемой задачи.

- •Стоимость организации вычислений.

- •14.2 Кластерные проекты (на примере мвс-1000 м). Коммуникационные технологии построения кластеров. Beowulf- кластеры. Beowulf- кластеры. The-hive.

- •14.3Теоретические модели параллельных систем. Ячеечные автоматы Неймана. Пространственная машина Унгера.

- •15.1 Достижения и перспективы развития вычислительной техники.

- •Японская программа по развитию вычислительной техники:

- •Задачи:

- •Существуют трансляторы с полуестетвенных языков

- •15.2 Способы распределения задач по процессорам в мультипроцессорных вс.

- •Организация супер-эвм с общей памятью (на примере hp Superdone). Архитектура ccNuma.

- •16.1 Классификационные схемы архитектур вс (по Флинну, по Энслоу). Достоинства и недостатки каждой из классификаций.

- •Многовходовые

- •Несимметричные(системы с неоднородными процессорами)

- •5.Вс с матричными (векторными) процессорами (Архитектура мрр)

- •16.2 Теоретические модели параллельных систем. Ячеечные автоматы Неймана. Пространственная машина Унгера

- •16.3Организация супер-эвм с общей памятью (на примере hp Superdone). Архитектура ccNuma.

- •17.1Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •17.2 Вычислительные системы с векторной обработкой команд (структура). Диаграмма выполнения операций с векторной обработкой команд.

- •Вычисление параллельного префикса

- •63 Гусеничный алгоритм обработки элементов массива. Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •65 Реализация фундаментальных вычислительных алгоритмов в матричной сети процессоров.

- •Решение задач линейной алгебры на матричной сети процессоров

- •Японская программа по развитию вычислительной техники:

- •Задачи:

- •Существуют трансляторы с полуестетвенных языков

- •2 Пути развития вычислительных систем (вс). Пять японских программ о развитии и внедрении средств вычислительной техники.

- •Использование гиперкуба для реализации параллельных алгоритмов.

- •Решение задачи быстрой сортировки на гиперкубе

- •Использование комбинаторов в редукционном вычислении

- •Процесс вычисления комбинаторного выражения

- •Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •20.1 Эволюция развития архитектур вс

- •20.2 Принципы векторизации последовательных программ. Критерии оценки векторной архитектуры.

- •2) Стартовое время конвейера.

- •Гусеничный алгоритм обработки элементов массива. Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •21.2 Теоретические модели параллельных систем. Машина Холланда.

- •Решение задач линейной алгебры на систолических массивах.

- •22.2 Реализация принципа «сверхмультиобработки». Статический и динамический способ создания «общего кода».

- •22.3 СуперЭвм фирмы Fujitsu.

- •23.1 Сравнительные возможности двух методов организации параллельных вычислений: метод конвейеризации и метод параллелизма.

- •Факторы, влияющие на снижение производительности в системах с векторной обработкой команд

- •5. Зависимость по управлению

- •Основные технологии параллельного программирования.

- •62 Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Вычислительные системы с векторной обработкой команд (структура). Диаграмма выполнения операций с векторной обработкой команд.

3. Организация памяти.

V0…V7 – организуют локальную память.

Взаимодействие локальной памяти с главной памятью и с конвейером:

Л окальная

память

должна быть многоуровневой.

При наличии большого

количества конвейерных устройств

эта структура

усложняется.

Д

окальная

память

должна быть многоуровневой.

При наличии большого

количества конвейерных устройств

эта структура

усложняется.

Д ля

повышения эффективности локальной

памяти используются коммутаторы.

ля

повышения эффективности локальной

памяти используются коммутаторы.

Обе памяти являются расслоенными.

В системах Cray соединение: либо через коммутатор (обе памяти являются расслоенными), либо через сдвоенный буфер:

3 -й

способ – введение

в систему команд машины специальных

команд,

которые обеспечивают бесконфликтный

доступ.

-й

способ – введение

в систему команд машины специальных

команд,

которые обеспечивают бесконфликтный

доступ.

POST – запрос вызова операндов. POST Если выполняется команда WAIT, другие запросы к памяти; WAIT блокируются

2.3 Понятие метакомпьютинга. Способы организации метакомпьютера. Основные решаемые задачи. Примеры использования метакомпьютера для решения сложных задач.

Во многих задачах, таких как гидрология, космология, окружающая среда, биология, множество задач прогнозирования, требуют следующую мощность вычислительных ресурсов:

Быстродействие: 0,2:20 Терра LFOPS;

ОП: 100:200 Гбайт;

Дисковая память: 1–2 Терра байта;

Пропускная способность УВВ: 0,2–0,5 Гбайт/сек.

Ни одна СуперЭВМ не достигает этого уровня. Наиболее приближенными к этому уровню являются СуперЭВМ:

Cray X–MP; SGI; Fujitsu, Hitachi.

Т.о. чтобы решать эти задачи необходимо создание метакомпьютера (сверхкомпьютера). Это направление развивается с 1997 года. В США для этого создан специальный центр суперкомпьютерной технологии. Эта технология метакомпьютинг основана на слиянии 2-х основных направлений ВТ.

создание СуперЭВМ;

развитие сетей ЭВМ.

В этой технологии Суперкомпьютеры объединены с помощью глобальных сетей для создания масштабируемой вычислительной мощности.

Основные формы развития метакомпьютинга:

Настольный Суперкомпьютер – это СуперЭВМ с выходом через сеть на более мощные ВС.

Интелектуальные интегральные системы, в которых в реальном масштабе времени объединяются: обработка информации от датчиков (управление различными системами), анализ этих данных, принятие решения, выдача управляющих воздействий, моделирование различных процессов.

Сетевой Суперкомпьютинг. В плане создания масштабируемых систем, это направление делится на 2 части:

Объединение вычислительных ресурсов с помощью локальной сети для создания такой вычислительной мощности, достаточной для решения задач;

Объединение суперузлов в рамках региона и в национальном масштабе.

В настоящее время в России отсутствуют Суперкомпьютеры с открытой архитектурой, которые можно было бы использовать для этого. Отсюда основное направление метакомпьютинга в России – первое.

3.1Транспьютеры. Практическое применение

Транспьютер (англ. transputer) — элемент построения многопроцессорных систем, выполненный на одном кристалле большой интегральной схемы, продукт английской компании INMOS Ltd. (ныне — подразделение STMicroelectronics).

Термин транспьютер происходит от слов Transistor и Computer. Такой генезис должен, по мнению разработчиков, подчёркивать возможность построения сложных вычислительных комплексов на базе транспьютеров, где их роль уподоблялась бы роли транзисторов, выступающих основным элементом при проектировании электронных схем. Другая интерпретация: trans-put-er — тот, кто передаёт, указывает на присутствие встроенных скоростных устройств ввода/вывода для обмена с соседними процессорами.

Параллельная система может создаваться из набора транспьютеров, которые функционируют независимо и взаимодействуют через последовательные каналы связи. Такие системы можно проектировать и программировать на языке Occam, основанном на концепции взаимодействующих процессов, или на других языках (например, Concurrent C, Concurrent Fortran), имеющих соответствующие средства.

Язык программирования Occam был разработан компанией INMOS на основе теории Энтони Хоара (англ. C. A. R. Hoare) о взаимодействии процессов. Occam является алголо-подобным языком высокого уровня; при этом язык оптимизирован с точки зрения эффективности его трансляции в систему команд транспьютера. Первоначально INMOS даже предлагала воспринимать Occam в качестве транспьютерного ассемблера, но позже выпустила пакет низкоуровневых средств для разработчиков компиляторов, а также включила в Occam предписание GUY, позволяющее вставлять код на уровне процессора.

Транспьютеры успешно использовались в различных областях — от встроенных систем до суперЭВМ. В настоящее время транспьютеры не производятся, будучи вытесненными похожими разработками конкурентов, особенно Texas Instruments (TMS320) и Intel (80860). Принято считать, что концепция транспьютеров оказала заметное влияние на развитие микропроцессорной техники1980—1990-х годов.

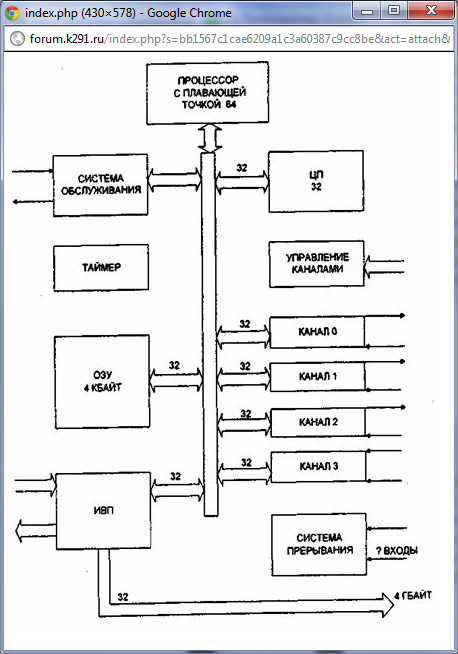

На рис приведена структура транспьютера Т800(Texas Instruments). На одном кристалле располагается центральный процессор (ЦП), обрабатывающий целочисленные величины, 64-разрядный блок обработки Данных с плавающей точкой (БПТ), внутренняя память (ОП) объемом в 4 Кбайт, интерфейс с внешней (внекристальной) памяти (ИВП). Внутренняя память обеспечивает доступ со временем цикла, равного одному такту процессора. Это позволяет рассматривать ее как сверхбыстродействующую память. Мультиплексируемый интерфейс с внешней памятью обеспечивает доступ к 32-Разрядному адресному пространству объемом до 4 Гбайт.

Внутренняя и внешняя память образуют одно непрерывное пространство. БПТ предназначено для высокопроизводительного выполнения операций, предусматривающих операции с одинарной точностью(32 разряда) и двойной точностью (64 разряда).

|

Наиболее известная матричная арх-ра, состоящая из транспьютеров – тороидальная матрица.