- •1.1. Развитие элементной базы вс.

- •1.2. Перспективы развития архитектур класса mpp (Massively Parallel Processor).

- •С хематический вид архитектуры с раздельной памятью

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Использование гиперкуба для реализации параллельных алгоритмов.

- •Решение задачи быстрой сортировки на гиперкубе

- •2.1. Матричные вс с ассоциативной обработкой инф-ции на примере вс pepe.

- •2.2 Супер-эвм фирмы Cray Research.

- •1. Три типа различных регистров:

- •2. Параллельная обработка на нескольких уровнях.

- •3. Организация памяти.

- •2.3 Понятие метакомпьютинга. Способы организации метакомпьютера. Основные решаемые задачи. Примеры использования метакомпьютера для решения сложных задач.

- •3.1Транспьютеры. Практическое применение

- •3.2 Способы распределения задач по процессорам в мультипроцессорных вс.

- •3.3 Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •4.1 Вс на основе систолических и волновых матриц

- •Волновая матрица.

- •4.2 Возм-ые пути постр-ия высокопроизв-ых вс, отличных от фоннеймановского типа. Понятие семантического разрыва между стр-рой вс и реал-ой прогр-ой.

- •Концепция неограниченного параллелизма. Выявление микро- и макропараллелизма в алгоритмах.

- •5.1 Анализ производ-ти мультипроцессорных вс. Коэффициент ускорения вычислений. Проблемы достижимости линейного роста производительности.

- •5.2 Редукционная машина «Алиса». Пример выполнения фрагмента программы.

- •Параллельная редукция

- •6.1 Развитие новых методов вычислений Японская программа по развитию вычислительной техники:

- •Основной язык: Prolog

- •6.2 Показатели качества функционирования вс. Критерий Гроша. Критерий Минского. Двухпараметрический критерий. Проблемы достижения линейного роста производительности вс.

- •7.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •7.3 Перспективы развития vpp (Vector Parallel Processor)

- •8.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •8.2 Особенности перехода к параллельным вычислениям. Проблемы организации параллельных вычислений.

- •9.1 Сравнительный анализ режимов и алгоритмов обработки информации в вс Сравнительные возможности двух методов организации параллельных вычислений: метод конвейеризации и метод параллелизма.

- •9.2 Принцип вычислений на основе управления потоком данных. Машины потоков данных (мпд). Архитектура. Достоинства и недостатки мпд.

- •Структура машины потоков данных. Данные хранятся в пакетах данных – в активных ячейках памяти. Ба – блок арифметический. Бл – блок логический. В активной памяти находятся пакеты, готовые к выполнению.

- •Функционирование машин потоков данных.

- •Организация сети передачи пакетов в мпд.

- •Достоинства мпд.

- •Недостатки мпд.

- •Обработка структур в мпд.

- •Структура мпд для обработки структур.

- •Структура устройства хранения и обработки.

- •9.3 Реализация фундаментальных вычислительных алгоритмов в матричной сети процессоров.

- •Решение задач линейной алгебры на матричной сети процессоров

- •10.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •10.2 Принцип вычислений на основе управления потоком данных. Машины потоков данных (мпд). Архитектура. Достоинства и недостатки мпд.

- •Данные хранятся в пакетах данных – в активных ячейках памяти. В активной памяти находятся пакеты, готовые к выполнению.

- •10.3 Принцип «разделяй и властвуй» и его использование для повышения эффективности выполнения вычислительных алгоритмов в сетях процессоров

- •11.1 Абстрактная архитектура вс. Основные модули и интерфейсы

- •Арифметический и командный конвейер

- •11.2 Особенности перехода к параллельным вычислениям. Проблемы организации параллельных вычислений.

- •11.3 Современные тесты для оценки производительности вс.

- •12.1 Диаграмма выполнения команды в машине фон Неймана. «Узкие места» при выполнении команды в последовательной вс. Методы устранения «узких» мест.

- •12.2 Редукционная g-машина. Пример выполнения фрагмента программы.

- •1. Три типа различных регистров:

- •2. Параллельная обработка на нескольких уровнях.

- •3. Организация памяти.

- •13.1 Арифметический и командный конвейер.

- •13.2 Организация тэговой памяти и оценка ее эффективности на примере мультипроцессорной вс Эльбрус.

- •Независимость программных средств от обрабатываемых данных. Программные средства реализованы только на логический уровень, поэтому:

- •Разработка высокопроизводительных систем класса мпд на основе ассоциативной памяти.

- •14.1. Способы выбора количества уровней совмещения (ступеней) в командном конвейере.

- •Тип решаемой задачи.

- •Стоимость организации вычислений.

- •14.2 Кластерные проекты (на примере мвс-1000 м). Коммуникационные технологии построения кластеров. Beowulf- кластеры. Beowulf- кластеры. The-hive.

- •14.3Теоретические модели параллельных систем. Ячеечные автоматы Неймана. Пространственная машина Унгера.

- •15.1 Достижения и перспективы развития вычислительной техники.

- •Японская программа по развитию вычислительной техники:

- •Задачи:

- •Существуют трансляторы с полуестетвенных языков

- •15.2 Способы распределения задач по процессорам в мультипроцессорных вс.

- •Организация супер-эвм с общей памятью (на примере hp Superdone). Архитектура ccNuma.

- •16.1 Классификационные схемы архитектур вс (по Флинну, по Энслоу). Достоинства и недостатки каждой из классификаций.

- •Многовходовые

- •Несимметричные(системы с неоднородными процессорами)

- •5.Вс с матричными (векторными) процессорами (Архитектура мрр)

- •16.2 Теоретические модели параллельных систем. Ячеечные автоматы Неймана. Пространственная машина Унгера

- •16.3Организация супер-эвм с общей памятью (на примере hp Superdone). Архитектура ccNuma.

- •17.1Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •17.2 Вычислительные системы с векторной обработкой команд (структура). Диаграмма выполнения операций с векторной обработкой команд.

- •Вычисление параллельного префикса

- •63 Гусеничный алгоритм обработки элементов массива. Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •65 Реализация фундаментальных вычислительных алгоритмов в матричной сети процессоров.

- •Решение задач линейной алгебры на матричной сети процессоров

- •Японская программа по развитию вычислительной техники:

- •Задачи:

- •Существуют трансляторы с полуестетвенных языков

- •2 Пути развития вычислительных систем (вс). Пять японских программ о развитии и внедрении средств вычислительной техники.

- •Использование гиперкуба для реализации параллельных алгоритмов.

- •Решение задачи быстрой сортировки на гиперкубе

- •Использование комбинаторов в редукционном вычислении

- •Процесс вычисления комбинаторного выражения

- •Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •20.1 Эволюция развития архитектур вс

- •20.2 Принципы векторизации последовательных программ. Критерии оценки векторной архитектуры.

- •2) Стартовое время конвейера.

- •Гусеничный алгоритм обработки элементов массива. Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •21.2 Теоретические модели параллельных систем. Машина Холланда.

- •Решение задач линейной алгебры на систолических массивах.

- •22.2 Реализация принципа «сверхмультиобработки». Статический и динамический способ создания «общего кода».

- •22.3 СуперЭвм фирмы Fujitsu.

- •23.1 Сравнительные возможности двух методов организации параллельных вычислений: метод конвейеризации и метод параллелизма.

- •Факторы, влияющие на снижение производительности в системах с векторной обработкой команд

- •5. Зависимость по управлению

- •Основные технологии параллельного программирования.

- •62 Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Вычислительные системы с векторной обработкой команд (структура). Диаграмма выполнения операций с векторной обработкой команд.

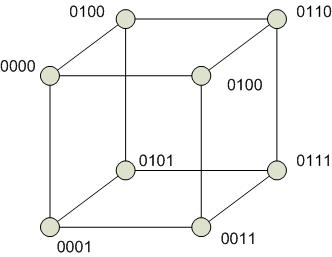

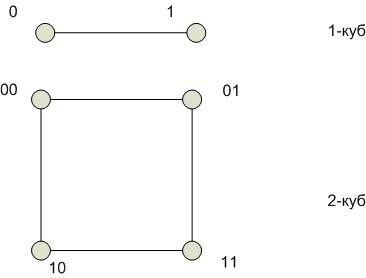

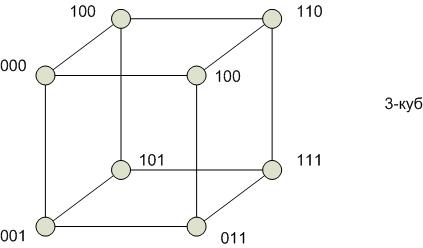

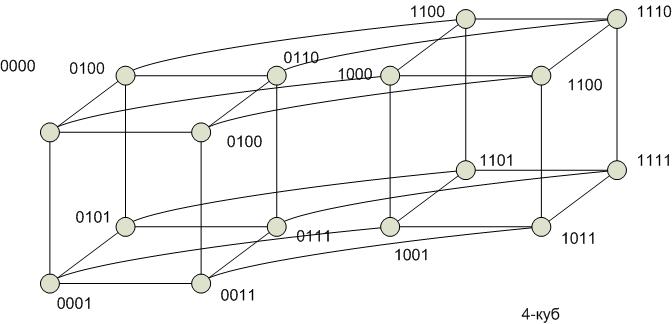

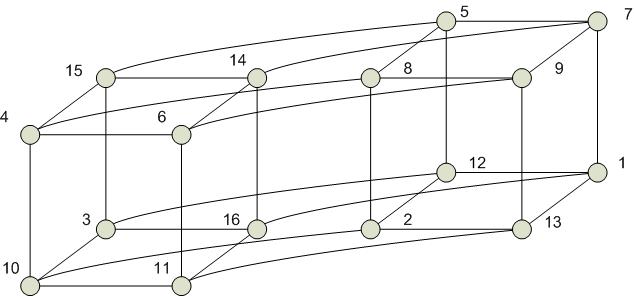

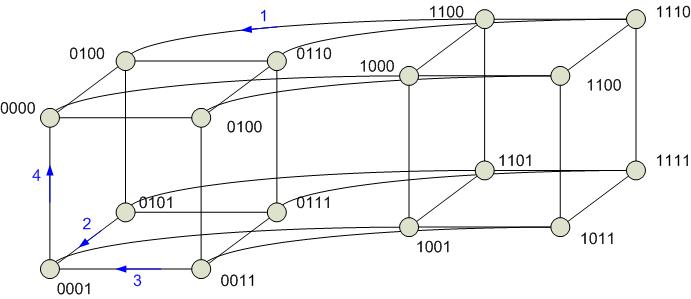

Использование гиперкуба для реализации параллельных алгоритмов.

С тепень

строго не определена. В отличие от других

архитектур связанность в гиперкубе

можно наращивать. Степень одинакова

для всех вершин. Отсутствие фиксированной

архитектуры является и недостатком.

тепень

строго не определена. В отличие от других

архитектур связанность в гиперкубе

можно наращивать. Степень одинакова

для всех вершин. Отсутствие фиксированной

архитектуры является и недостатком.

Диаметр

гиперкуба пропорционален

![]() ,

где n

– число вершин. При этом между любой

парой вершин гиперкуба существует путь

минимальной длины.

,

где n

– число вершин. При этом между любой

парой вершин гиперкуба существует путь

минимальной длины.

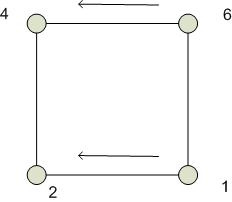

Выполнение операции поиска минимума на гиперкубе:

из правого куба пересылаются данные между одноименными вершинами, которые имеют разницу только в одном разряде:

1 Особенностью гиперкуба является возможность моделирования на нем других сетевых архитектур. Тогда ребра куба моделируют каналы передачи информации.

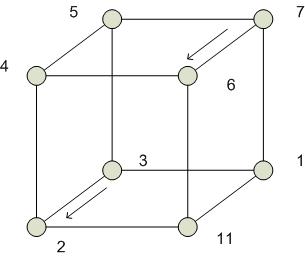

Решение задачи быстрой сортировки на гиперкубе

Задача Quick Sort Hyper:

предполагается, что n элементов располагается по 2d вершин гиперкуба. Каждая вершина содержит

элементов;

элементов;каждый процессор сортирует свои n элементов независимо;

0-я вершина гиперкуба определяет медиану своих n элементов;

0-я вершина может рассылать свою медиану всем 2d узлам.

1-й шаг – ребро 1

2-й шаг – ребро 2

3-й шаг – ребро 3

4-й шаг – ребро 4.

2.1. Матричные вс с ассоциативной обработкой инф-ции на примере вс pepe.

Элементные процессоры, объединенные в матрицы

б ыл

реализован 1 квадрант (256 процессоров)

=> Illiac

– IV;

1млрд операций в секунду (4-я часть от

SOLOMON);

Состоит из 4-х квадрантов; Каждый

управляющий процессор имеет матрицу

8х8 Е

ыл

реализован 1 квадрант (256 процессоров)

=> Illiac

– IV;

1млрд операций в секунду (4-я часть от

SOLOMON);

Состоит из 4-х квадрантов; Каждый

управляющий процессор имеет матрицу

8х8 Е

У каждого элементарного процессора имеется регистр режима работы, который определяет, как выполнить команду, или указывает , что команду выполнять не надо (определяет необходимость выполнения команды). (Подавались команды, они выполнялись процессорами. У процессора одна степень свободы: выполнить команду или не выполнить).

А = {а1, а2,… а64} В = {b1, b2,… b64} C = A + B. Достаточно одного такта матрицы 8Х8, чтобы выполнить команду С=А+В. а1, b2 – в первый процессор,…, а64, b64 – в 64 процессор. Эффективность – при режимах векторных и матричных вычислений.

Д ругие

системы(наиболее известные): STARAN

– радиолокационные задачи, управление

воздушным движением, 32 ассоциативные

матрицы. PEPE

– “ансамбль параллельных процессоров”

– противоракетная оборона, Bell

Telphone

Laboratories.

Система PEPE

сочетает ассоциативную обработку

информации и организацию вычислений

с помощью матричных процессоров.

ругие

системы(наиболее известные): STARAN

– радиолокационные задачи, управление

воздушным движением, 32 ассоциативные

матрицы. PEPE

– “ансамбль параллельных процессоров”

– противоракетная оборона, Bell

Telphone

Laboratories.

Система PEPE

сочетает ассоциативную обработку

информации и организацию вычислений

с помощью матричных процессоров.

АВУ – управление своим вычислительным устройством; Е + ОЗУ – элементарный процессор; БУ КУ – блок управления корреляционным устройством; БУ Е - блок управления элементарными процессорами; БУ АВУ – блок управления ассоциативным вычислительным устройством; Е – элементарный процессор; К – корреляционное устройство

Сочетание настройки, выполнения, … Ассоциативное ЗУ(запоминающее устройство) : не только блок хранения информации, но и логическая обработка данных, которые там находятся. Следующее направление связанно с матричной обработкой информации – Транспьютер (середина 70-х, Inmos – фирма, процессор назывался Т414). Транспьютер – элементарный процессор с RISK-архитектурой, который имел на плате специальный интерфейс для соединения с другими транспьютерами и организации в матрицы.