- •1.1. Развитие элементной базы вс.

- •1.2. Перспективы развития архитектур класса mpp (Massively Parallel Processor).

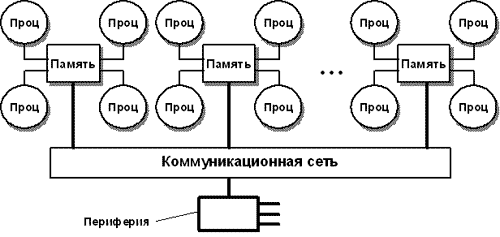

- •С хематический вид архитектуры с раздельной памятью

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Использование гиперкуба для реализации параллельных алгоритмов.

- •Решение задачи быстрой сортировки на гиперкубе

- •2.1. Матричные вс с ассоциативной обработкой инф-ции на примере вс pepe.

- •2.2 Супер-эвм фирмы Cray Research.

- •1. Три типа различных регистров:

- •2. Параллельная обработка на нескольких уровнях.

- •3. Организация памяти.

- •2.3 Понятие метакомпьютинга. Способы организации метакомпьютера. Основные решаемые задачи. Примеры использования метакомпьютера для решения сложных задач.

- •3.1Транспьютеры. Практическое применение

- •3.2 Способы распределения задач по процессорам в мультипроцессорных вс.

- •3.3 Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •4.1 Вс на основе систолических и волновых матриц

- •Волновая матрица.

- •4.2 Возм-ые пути постр-ия высокопроизв-ых вс, отличных от фоннеймановского типа. Понятие семантического разрыва между стр-рой вс и реал-ой прогр-ой.

- •Концепция неограниченного параллелизма. Выявление микро- и макропараллелизма в алгоритмах.

- •5.1 Анализ производ-ти мультипроцессорных вс. Коэффициент ускорения вычислений. Проблемы достижимости линейного роста производительности.

- •5.2 Редукционная машина «Алиса». Пример выполнения фрагмента программы.

- •Параллельная редукция

- •6.1 Развитие новых методов вычислений Японская программа по развитию вычислительной техники:

- •Основной язык: Prolog

- •6.2 Показатели качества функционирования вс. Критерий Гроша. Критерий Минского. Двухпараметрический критерий. Проблемы достижения линейного роста производительности вс.

- •7.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •7.3 Перспективы развития vpp (Vector Parallel Processor)

- •8.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •8.2 Особенности перехода к параллельным вычислениям. Проблемы организации параллельных вычислений.

- •9.1 Сравнительный анализ режимов и алгоритмов обработки информации в вс Сравнительные возможности двух методов организации параллельных вычислений: метод конвейеризации и метод параллелизма.

- •9.2 Принцип вычислений на основе управления потоком данных. Машины потоков данных (мпд). Архитектура. Достоинства и недостатки мпд.

- •Структура машины потоков данных. Данные хранятся в пакетах данных – в активных ячейках памяти. Ба – блок арифметический. Бл – блок логический. В активной памяти находятся пакеты, готовые к выполнению.

- •Функционирование машин потоков данных.

- •Организация сети передачи пакетов в мпд.

- •Достоинства мпд.

- •Недостатки мпд.

- •Обработка структур в мпд.

- •Структура мпд для обработки структур.

- •Структура устройства хранения и обработки.

- •9.3 Реализация фундаментальных вычислительных алгоритмов в матричной сети процессоров.

- •Решение задач линейной алгебры на матричной сети процессоров

- •10.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •10.2 Принцип вычислений на основе управления потоком данных. Машины потоков данных (мпд). Архитектура. Достоинства и недостатки мпд.

- •Данные хранятся в пакетах данных – в активных ячейках памяти. В активной памяти находятся пакеты, готовые к выполнению.

- •10.3 Принцип «разделяй и властвуй» и его использование для повышения эффективности выполнения вычислительных алгоритмов в сетях процессоров

- •11.1 Абстрактная архитектура вс. Основные модули и интерфейсы

- •Арифметический и командный конвейер

- •11.2 Особенности перехода к параллельным вычислениям. Проблемы организации параллельных вычислений.

- •11.3 Современные тесты для оценки производительности вс.

- •12.1 Диаграмма выполнения команды в машине фон Неймана. «Узкие места» при выполнении команды в последовательной вс. Методы устранения «узких» мест.

- •12.2 Редукционная g-машина. Пример выполнения фрагмента программы.

- •1. Три типа различных регистров:

- •2. Параллельная обработка на нескольких уровнях.

- •3. Организация памяти.

- •13.1 Арифметический и командный конвейер.

- •13.2 Организация тэговой памяти и оценка ее эффективности на примере мультипроцессорной вс Эльбрус.

- •Независимость программных средств от обрабатываемых данных. Программные средства реализованы только на логический уровень, поэтому:

- •Разработка высокопроизводительных систем класса мпд на основе ассоциативной памяти.

- •14.1. Способы выбора количества уровней совмещения (ступеней) в командном конвейере.

- •Тип решаемой задачи.

- •Стоимость организации вычислений.

- •14.2 Кластерные проекты (на примере мвс-1000 м). Коммуникационные технологии построения кластеров. Beowulf- кластеры. Beowulf- кластеры. The-hive.

- •14.3Теоретические модели параллельных систем. Ячеечные автоматы Неймана. Пространственная машина Унгера.

- •15.1 Достижения и перспективы развития вычислительной техники.

- •Японская программа по развитию вычислительной техники:

- •Задачи:

- •Существуют трансляторы с полуестетвенных языков

- •15.2 Способы распределения задач по процессорам в мультипроцессорных вс.

- •Организация супер-эвм с общей памятью (на примере hp Superdone). Архитектура ccNuma.

- •16.1 Классификационные схемы архитектур вс (по Флинну, по Энслоу). Достоинства и недостатки каждой из классификаций.

- •Многовходовые

- •Несимметричные(системы с неоднородными процессорами)

- •5.Вс с матричными (векторными) процессорами (Архитектура мрр)

- •16.2 Теоретические модели параллельных систем. Ячеечные автоматы Неймана. Пространственная машина Унгера

- •16.3Организация супер-эвм с общей памятью (на примере hp Superdone). Архитектура ccNuma.

- •17.1Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •17.2 Вычислительные системы с векторной обработкой команд (структура). Диаграмма выполнения операций с векторной обработкой команд.

- •Вычисление параллельного префикса

- •63 Гусеничный алгоритм обработки элементов массива. Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •65 Реализация фундаментальных вычислительных алгоритмов в матричной сети процессоров.

- •Решение задач линейной алгебры на матричной сети процессоров

- •Японская программа по развитию вычислительной техники:

- •Задачи:

- •Существуют трансляторы с полуестетвенных языков

- •2 Пути развития вычислительных систем (вс). Пять японских программ о развитии и внедрении средств вычислительной техники.

- •Использование гиперкуба для реализации параллельных алгоритмов.

- •Решение задачи быстрой сортировки на гиперкубе

- •Использование комбинаторов в редукционном вычислении

- •Процесс вычисления комбинаторного выражения

- •Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •20.1 Эволюция развития архитектур вс

- •20.2 Принципы векторизации последовательных программ. Критерии оценки векторной архитектуры.

- •2) Стартовое время конвейера.

- •Гусеничный алгоритм обработки элементов массива. Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •21.2 Теоретические модели параллельных систем. Машина Холланда.

- •Решение задач линейной алгебры на систолических массивах.

- •22.2 Реализация принципа «сверхмультиобработки». Статический и динамический способ создания «общего кода».

- •22.3 СуперЭвм фирмы Fujitsu.

- •23.1 Сравнительные возможности двух методов организации параллельных вычислений: метод конвейеризации и метод параллелизма.

- •Факторы, влияющие на снижение производительности в системах с векторной обработкой команд

- •5. Зависимость по управлению

- •Основные технологии параллельного программирования.

- •62 Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Вычислительные системы с векторной обработкой команд (структура). Диаграмма выполнения операций с векторной обработкой команд.

Организация супер-эвм с общей памятью (на примере hp Superdone). Архитектура ccNuma.

Гибридная архитектура (NUMA) Организация когерентности многоуровневой иерархической памяти. Гибридная архитектура NUMA (nonuniform memory access). Главная особенность такой архитектуры - неоднородный доступ к памяти.

Гибридная архитектура воплощает в себе удобства систем с общей памятью и относительную дешевизну систем с раздельной памятью. Суть этой архитектуры - в особой организации памяти, а именно: память является физически распределенной по различным частям системы, но логически разделяемой, так что пользователь видит единое адресное пространство. Система состоит из однородных базовых модулей (плат), состоящих из небольшого числа процессоров и блока памяти. Модули объединены с помощью высокоскоростного коммутатора. Поддерживается единое адресное пространство, аппаратно поддерживается доступ к удаленной памяти, т.е. к памяти других модулей. При этом доступ к локальной памяти осуществляется в несколько раз быстрее, чем к удаленной. По существу архитектура NUMA является MPP (массивно-параллельная архитектура) архитектурой, где в качестве отдельных вычислительных элементов берутся SMP (cимметричная многопроцессорная архитектура) узлы.

Структурная схема компьютера с гибридной сетью: четыре процессора связываются между собой при помощи кроссбара в рамках одного SMP узла. Узлы связаны сетью типа "бабочка" (Butterfly):

Впервые идею гибридной архитектуры предложил Стив Воллох и воплотил в системах серии Exemplar. Вариант Воллоха - система, состоящая из 8-ми SMP узлов. Фирма HP купила идею и реализовала на суперкомпьютерах серии SPP. Идею подхватил Сеймур Крей (Seymour R.Cray) и добавил новый элемент - когерентный кэш, создав так называемую архитектуру cc-NUMA (Cache Coherent Non-Uniform Memory Access), которая расшифровывается как "неоднородный доступ к памяти с обеспечением когерентности кэшей". Он ее реализовал на системах типа Origin.

Организация когерентности многоуровневой иерархической памяти.

Понятие когерентности кэшей описывает тот факт, что все центральные процессоры получают одинаковые значения одних и тех же переменных в любой момент времени. Действительно, поскольку кэш-память принадлежит отдельному компьютеру, а не всей многопроцессорной системе в целом, данные, попадающие в кэш одного компьютера, могут быть недоступны другому. Чтобы избежать этого, следует провести синхронизацию информации, хранящейся в кэш-памяти процессоров.

Для обеспечения подобной когерентности кэшей существуют несколько возможностей:

• Использовать механизм отслеживания шинных запросов (snoopy bus protocol), в котором кэши отслеживают переменные, передаваемые к любому из центральных процессоров и, при необходимости, модифицируют собственные копии таких переменных. • Выделять специальную часть памяти, отвечающую за отслеживание достоверности всех используемых копий переменных.

Наиболее известными системами архитектуры cc-NUMA являются: HP 9000 V-class в SCA-конфигурациях, SGI Origin3000, Sun HPC 15000, IBM/Sequent NUMA-Q 2000. На настоящий момент максимальное число процессоров в cc-NUMA-системах может превышать 1000 (серия Origin3000). Обычно вся система работает под управлением единой ОС, как в SMP. Возможны также варианты динамического "подразделения" системы, когда отдельные "разделы" системы работают под управлением разных ОС. При работе NUMA-системами, также как с SMP, используют так называемую парадигму программирования с общей памятью (shared memory paradigm).