- •1.1. Развитие элементной базы вс.

- •1.2. Перспективы развития архитектур класса mpp (Massively Parallel Processor).

- •С хематический вид архитектуры с раздельной памятью

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Использование гиперкуба для реализации параллельных алгоритмов.

- •Решение задачи быстрой сортировки на гиперкубе

- •2.1. Матричные вс с ассоциативной обработкой инф-ции на примере вс pepe.

- •2.2 Супер-эвм фирмы Cray Research.

- •1. Три типа различных регистров:

- •2. Параллельная обработка на нескольких уровнях.

- •3. Организация памяти.

- •2.3 Понятие метакомпьютинга. Способы организации метакомпьютера. Основные решаемые задачи. Примеры использования метакомпьютера для решения сложных задач.

- •3.1Транспьютеры. Практическое применение

- •3.2 Способы распределения задач по процессорам в мультипроцессорных вс.

- •3.3 Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •4.1 Вс на основе систолических и волновых матриц

- •Волновая матрица.

- •4.2 Возм-ые пути постр-ия высокопроизв-ых вс, отличных от фоннеймановского типа. Понятие семантического разрыва между стр-рой вс и реал-ой прогр-ой.

- •Концепция неограниченного параллелизма. Выявление микро- и макропараллелизма в алгоритмах.

- •5.1 Анализ производ-ти мультипроцессорных вс. Коэффициент ускорения вычислений. Проблемы достижимости линейного роста производительности.

- •5.2 Редукционная машина «Алиса». Пример выполнения фрагмента программы.

- •Параллельная редукция

- •6.1 Развитие новых методов вычислений Японская программа по развитию вычислительной техники:

- •Основной язык: Prolog

- •6.2 Показатели качества функционирования вс. Критерий Гроша. Критерий Минского. Двухпараметрический критерий. Проблемы достижения линейного роста производительности вс.

- •7.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •7.3 Перспективы развития vpp (Vector Parallel Processor)

- •8.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •8.2 Особенности перехода к параллельным вычислениям. Проблемы организации параллельных вычислений.

- •9.1 Сравнительный анализ режимов и алгоритмов обработки информации в вс Сравнительные возможности двух методов организации параллельных вычислений: метод конвейеризации и метод параллелизма.

- •9.2 Принцип вычислений на основе управления потоком данных. Машины потоков данных (мпд). Архитектура. Достоинства и недостатки мпд.

- •Структура машины потоков данных. Данные хранятся в пакетах данных – в активных ячейках памяти. Ба – блок арифметический. Бл – блок логический. В активной памяти находятся пакеты, готовые к выполнению.

- •Функционирование машин потоков данных.

- •Организация сети передачи пакетов в мпд.

- •Достоинства мпд.

- •Недостатки мпд.

- •Обработка структур в мпд.

- •Структура мпд для обработки структур.

- •Структура устройства хранения и обработки.

- •9.3 Реализация фундаментальных вычислительных алгоритмов в матричной сети процессоров.

- •Решение задач линейной алгебры на матричной сети процессоров

- •10.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •10.2 Принцип вычислений на основе управления потоком данных. Машины потоков данных (мпд). Архитектура. Достоинства и недостатки мпд.

- •Данные хранятся в пакетах данных – в активных ячейках памяти. В активной памяти находятся пакеты, готовые к выполнению.

- •10.3 Принцип «разделяй и властвуй» и его использование для повышения эффективности выполнения вычислительных алгоритмов в сетях процессоров

- •11.1 Абстрактная архитектура вс. Основные модули и интерфейсы

- •Арифметический и командный конвейер

- •11.2 Особенности перехода к параллельным вычислениям. Проблемы организации параллельных вычислений.

- •11.3 Современные тесты для оценки производительности вс.

- •12.1 Диаграмма выполнения команды в машине фон Неймана. «Узкие места» при выполнении команды в последовательной вс. Методы устранения «узких» мест.

- •12.2 Редукционная g-машина. Пример выполнения фрагмента программы.

- •1. Три типа различных регистров:

- •2. Параллельная обработка на нескольких уровнях.

- •3. Организация памяти.

- •13.1 Арифметический и командный конвейер.

- •13.2 Организация тэговой памяти и оценка ее эффективности на примере мультипроцессорной вс Эльбрус.

- •Независимость программных средств от обрабатываемых данных. Программные средства реализованы только на логический уровень, поэтому:

- •Разработка высокопроизводительных систем класса мпд на основе ассоциативной памяти.

- •14.1. Способы выбора количества уровней совмещения (ступеней) в командном конвейере.

- •Тип решаемой задачи.

- •Стоимость организации вычислений.

- •14.2 Кластерные проекты (на примере мвс-1000 м). Коммуникационные технологии построения кластеров. Beowulf- кластеры. Beowulf- кластеры. The-hive.

- •14.3Теоретические модели параллельных систем. Ячеечные автоматы Неймана. Пространственная машина Унгера.

- •15.1 Достижения и перспективы развития вычислительной техники.

- •Японская программа по развитию вычислительной техники:

- •Задачи:

- •Существуют трансляторы с полуестетвенных языков

- •15.2 Способы распределения задач по процессорам в мультипроцессорных вс.

- •Организация супер-эвм с общей памятью (на примере hp Superdone). Архитектура ccNuma.

- •16.1 Классификационные схемы архитектур вс (по Флинну, по Энслоу). Достоинства и недостатки каждой из классификаций.

- •Многовходовые

- •Несимметричные(системы с неоднородными процессорами)

- •5.Вс с матричными (векторными) процессорами (Архитектура мрр)

- •16.2 Теоретические модели параллельных систем. Ячеечные автоматы Неймана. Пространственная машина Унгера

- •16.3Организация супер-эвм с общей памятью (на примере hp Superdone). Архитектура ccNuma.

- •17.1Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •17.2 Вычислительные системы с векторной обработкой команд (структура). Диаграмма выполнения операций с векторной обработкой команд.

- •Вычисление параллельного префикса

- •63 Гусеничный алгоритм обработки элементов массива. Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •65 Реализация фундаментальных вычислительных алгоритмов в матричной сети процессоров.

- •Решение задач линейной алгебры на матричной сети процессоров

- •Японская программа по развитию вычислительной техники:

- •Задачи:

- •Существуют трансляторы с полуестетвенных языков

- •2 Пути развития вычислительных систем (вс). Пять японских программ о развитии и внедрении средств вычислительной техники.

- •Использование гиперкуба для реализации параллельных алгоритмов.

- •Решение задачи быстрой сортировки на гиперкубе

- •Использование комбинаторов в редукционном вычислении

- •Процесс вычисления комбинаторного выражения

- •Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •20.1 Эволюция развития архитектур вс

- •20.2 Принципы векторизации последовательных программ. Критерии оценки векторной архитектуры.

- •2) Стартовое время конвейера.

- •Гусеничный алгоритм обработки элементов массива. Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •21.2 Теоретические модели параллельных систем. Машина Холланда.

- •Решение задач линейной алгебры на систолических массивах.

- •22.2 Реализация принципа «сверхмультиобработки». Статический и динамический способ создания «общего кода».

- •22.3 СуперЭвм фирмы Fujitsu.

- •23.1 Сравнительные возможности двух методов организации параллельных вычислений: метод конвейеризации и метод параллелизма.

- •Факторы, влияющие на снижение производительности в системах с векторной обработкой команд

- •5. Зависимость по управлению

- •Основные технологии параллельного программирования.

- •62 Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Вычислительные системы с векторной обработкой команд (структура). Диаграмма выполнения операций с векторной обработкой команд.

Независимость программных средств от обрабатываемых данных. Программные средства реализованы только на логический уровень, поэтому:

Они проще, и логический уровень проще.

Какие-то изменения на физическом уровне не влияют на программы, следовательно, программы не зависят от физического уровня.

Меньший объем памяти, занимаемый программой.

Введем дополнительное поле для индексации типов данных. Казалось бы, что объем памяти должен быть больше, но оказывается, что этот объем получается меньше.

Пример: Sx – суммарный объем программы для традиционной машины. Sy – суммарный памяти команд машины с ТП. Машина Х содержит 150 типов команд, КОП – 8 бит. Машина Y: 3-х битовый тег, 50 типов команд, КОП – 6 бит.

В традиционной машине каждый раз обрабатывается КОП, а в машине с ТП - нет, так как уровень программы и физический уровень – независимы. Машина будет эффективна, если отношение (Sy/Sx) < 1.

Недостатки теговой организации. Привязка задачи к архитектуре на этапе выполнения, имеет отрицательные черты, так как вносит дополнительные задержки при формировании кода программы. Это имеет значение в специализированных системах. Теговая память является эффективной не для всех вычислительных машин. Более значительный эффект от применения ТП в универсальных ЭВМ, где больше набор команд.

Представление массивов в теговой памяти. При представлении массивов и строк, в памяти отводится только один тег. Должна быть указана размерность массива. При организации массивов в ТП используется иерархическая смысловая структура. Пример: массив 3*4

13.3

Разработка высокопроизводительных систем класса мпд на основе ассоциативной памяти.

Исследования в области метеорологии.

Исследование структуры динамических и газодинамических неровностей с целью создания сложных аэродинамических комплексов.

Изучение свойств вещества в интересах атомной энергетики.

Структурное исследование человеческих генов.

Молекулярное конструирование лекарств.

Проектирование сверхсложных радиометрических комплексов.

Для решения поставленных задач требуется производительность 1012 – 1013 операций в секунду, объем оперативной памяти 1012 – 1015 бит. Эти условия могут быть достигнуты за счет:

- схемотехнических решений,

- распараллеливования вычислительных процессов.

Задача распараллеливования на математическом уровне решена и сводится к решению задач математической физики, то есть к решению задач матрично-векторного типа. Векторно-матричные системы обладают высокой степенью параллелизма, так например перемножение матриц 2-го порядка ранга 100 имеет уровень параллелизма 106

Для решения сложных задач наиболее приемлемы:

кластерные архитектуры,

многопроцессорные комплексы с общей памятью,

машины потоков данных (data flow);

платы, которые содержат полностью функциональный ассоциативный процессор для реализации памяти пакетов.

Институт проблем информатики РАН по аналогии с израильской системой создал 128000 72-разрядных слов ассоциативной памяти.

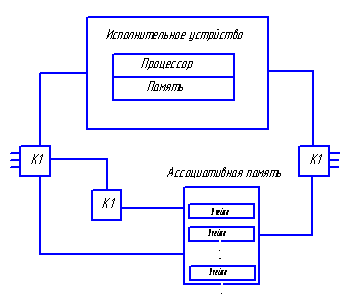

Общая архитектура такой системы:

Передача пакетов (ячеек) выполняется независимо по индивидуальным каналам связи. Выходящие из исполнительного устройства (ИУ) данные содержат указатели на операторы, которые должны быть выполнены. Ассоциативная память (АП) объединяет данные, относящиеся к одной команде. Если парного данного в АП нет, то происходит его запись в свободное место. Если есть парные данные, то происходит его считывание из АП и формирование пары данных, которая направляется к одному ИУ, эти данные стираются из памяти. В качестве ИУ используются обычные микропроцессоры.

Основные проблемы, возникающие при организации системы DataFlow:

так как для большого числа команд используются одни и те же ресурсы, то используется сверхмультипараллелизм. Каждому запросу ставится в соответствие свой цвет и можно будет определить, какой запрос обрабатывается. Реализуется виртуальная адресация в адресном пространстве.

совместный доступ к АП.

Применение АП помогает в решении следующих задач:

- для нескольких процессоров решается проблема обработки массивов, содержащих общие данные для нескольких параллельных процессов;

- проблема стирания и освобождения памяти.

Особенности реализации DataFlow.

На аппаратном уровне реализуется сверхпараллелизм.

Производительность 1011 – 1013 операций в секунду.

Программист исключается из распределения ресурсов, которые выделяются автоматически.

Обеспечивается высокая технологичность за счет идентичности модулей.

Используется принцип конвейеризации, который обеспечивает отсутствие задержек в логических схемах, то есть скалярные операции выполняются на уровне параллельных вычислений.

В АП возможна непосредственная работа с адресами за счет чего процессор может работать в реальном масштабе времени.

Недостаток DataFlow – производительность АП пропорциональна объему. Для устранения используется модульный принцип.

В системе используются два коммутатора:

К1 – распределяет выходящие из АП пары операндов по свободным ИУ,

К2 – распределяет выходящие из ИУ данные по АП.

Если имеется N ИУ и М модулей АП, то К1 и К2 являются матрицами N×M.

Буферная память (БП) используется для сглаживания неровностей потоков данных.