- •1.1. Развитие элементной базы вс.

- •1.2. Перспективы развития архитектур класса mpp (Massively Parallel Processor).

- •С хематический вид архитектуры с раздельной памятью

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Использование гиперкуба для реализации параллельных алгоритмов.

- •Решение задачи быстрой сортировки на гиперкубе

- •2.1. Матричные вс с ассоциативной обработкой инф-ции на примере вс pepe.

- •2.2 Супер-эвм фирмы Cray Research.

- •1. Три типа различных регистров:

- •2. Параллельная обработка на нескольких уровнях.

- •3. Организация памяти.

- •2.3 Понятие метакомпьютинга. Способы организации метакомпьютера. Основные решаемые задачи. Примеры использования метакомпьютера для решения сложных задач.

- •3.1Транспьютеры. Практическое применение

- •3.2 Способы распределения задач по процессорам в мультипроцессорных вс.

- •3.3 Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •4.1 Вс на основе систолических и волновых матриц

- •Волновая матрица.

- •4.2 Возм-ые пути постр-ия высокопроизв-ых вс, отличных от фоннеймановского типа. Понятие семантического разрыва между стр-рой вс и реал-ой прогр-ой.

- •Концепция неограниченного параллелизма. Выявление микро- и макропараллелизма в алгоритмах.

- •5.1 Анализ производ-ти мультипроцессорных вс. Коэффициент ускорения вычислений. Проблемы достижимости линейного роста производительности.

- •5.2 Редукционная машина «Алиса». Пример выполнения фрагмента программы.

- •Параллельная редукция

- •6.1 Развитие новых методов вычислений Японская программа по развитию вычислительной техники:

- •Основной язык: Prolog

- •6.2 Показатели качества функционирования вс. Критерий Гроша. Критерий Минского. Двухпараметрический критерий. Проблемы достижения линейного роста производительности вс.

- •7.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •7.3 Перспективы развития vpp (Vector Parallel Processor)

- •8.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •8.2 Особенности перехода к параллельным вычислениям. Проблемы организации параллельных вычислений.

- •9.1 Сравнительный анализ режимов и алгоритмов обработки информации в вс Сравнительные возможности двух методов организации параллельных вычислений: метод конвейеризации и метод параллелизма.

- •9.2 Принцип вычислений на основе управления потоком данных. Машины потоков данных (мпд). Архитектура. Достоинства и недостатки мпд.

- •Структура машины потоков данных. Данные хранятся в пакетах данных – в активных ячейках памяти. Ба – блок арифметический. Бл – блок логический. В активной памяти находятся пакеты, готовые к выполнению.

- •Функционирование машин потоков данных.

- •Организация сети передачи пакетов в мпд.

- •Достоинства мпд.

- •Недостатки мпд.

- •Обработка структур в мпд.

- •Структура мпд для обработки структур.

- •Структура устройства хранения и обработки.

- •9.3 Реализация фундаментальных вычислительных алгоритмов в матричной сети процессоров.

- •Решение задач линейной алгебры на матричной сети процессоров

- •10.1 Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •10.2 Принцип вычислений на основе управления потоком данных. Машины потоков данных (мпд). Архитектура. Достоинства и недостатки мпд.

- •Данные хранятся в пакетах данных – в активных ячейках памяти. В активной памяти находятся пакеты, готовые к выполнению.

- •10.3 Принцип «разделяй и властвуй» и его использование для повышения эффективности выполнения вычислительных алгоритмов в сетях процессоров

- •11.1 Абстрактная архитектура вс. Основные модули и интерфейсы

- •Арифметический и командный конвейер

- •11.2 Особенности перехода к параллельным вычислениям. Проблемы организации параллельных вычислений.

- •11.3 Современные тесты для оценки производительности вс.

- •12.1 Диаграмма выполнения команды в машине фон Неймана. «Узкие места» при выполнении команды в последовательной вс. Методы устранения «узких» мест.

- •12.2 Редукционная g-машина. Пример выполнения фрагмента программы.

- •1. Три типа различных регистров:

- •2. Параллельная обработка на нескольких уровнях.

- •3. Организация памяти.

- •13.1 Арифметический и командный конвейер.

- •13.2 Организация тэговой памяти и оценка ее эффективности на примере мультипроцессорной вс Эльбрус.

- •Независимость программных средств от обрабатываемых данных. Программные средства реализованы только на логический уровень, поэтому:

- •Разработка высокопроизводительных систем класса мпд на основе ассоциативной памяти.

- •14.1. Способы выбора количества уровней совмещения (ступеней) в командном конвейере.

- •Тип решаемой задачи.

- •Стоимость организации вычислений.

- •14.2 Кластерные проекты (на примере мвс-1000 м). Коммуникационные технологии построения кластеров. Beowulf- кластеры. Beowulf- кластеры. The-hive.

- •14.3Теоретические модели параллельных систем. Ячеечные автоматы Неймана. Пространственная машина Унгера.

- •15.1 Достижения и перспективы развития вычислительной техники.

- •Японская программа по развитию вычислительной техники:

- •Задачи:

- •Существуют трансляторы с полуестетвенных языков

- •15.2 Способы распределения задач по процессорам в мультипроцессорных вс.

- •Организация супер-эвм с общей памятью (на примере hp Superdone). Архитектура ccNuma.

- •16.1 Классификационные схемы архитектур вс (по Флинну, по Энслоу). Достоинства и недостатки каждой из классификаций.

- •Многовходовые

- •Несимметричные(системы с неоднородными процессорами)

- •5.Вс с матричными (векторными) процессорами (Архитектура мрр)

- •16.2 Теоретические модели параллельных систем. Ячеечные автоматы Неймана. Пространственная машина Унгера

- •16.3Организация супер-эвм с общей памятью (на примере hp Superdone). Архитектура ccNuma.

- •17.1Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •17.2 Вычислительные системы с векторной обработкой команд (структура). Диаграмма выполнения операций с векторной обработкой команд.

- •Вычисление параллельного префикса

- •63 Гусеничный алгоритм обработки элементов массива. Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •65 Реализация фундаментальных вычислительных алгоритмов в матричной сети процессоров.

- •Решение задач линейной алгебры на матричной сети процессоров

- •Японская программа по развитию вычислительной техники:

- •Задачи:

- •Существуют трансляторы с полуестетвенных языков

- •2 Пути развития вычислительных систем (вс). Пять японских программ о развитии и внедрении средств вычислительной техники.

- •Использование гиперкуба для реализации параллельных алгоритмов.

- •Решение задачи быстрой сортировки на гиперкубе

- •Использование комбинаторов в редукционном вычислении

- •Процесс вычисления комбинаторного выражения

- •Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •20.1 Эволюция развития архитектур вс

- •20.2 Принципы векторизации последовательных программ. Критерии оценки векторной архитектуры.

- •2) Стартовое время конвейера.

- •Гусеничный алгоритм обработки элементов массива. Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Достоинства и недостатки видов соединений вычислительных модулей в высокопроизводительных вс. Шина. Кольцо.

- •Одномерный путь передачи информации (отсутствует параллелизм передачи информации).

- •21.2 Теоретические модели параллельных систем. Машина Холланда.

- •Решение задач линейной алгебры на систолических массивах.

- •22.2 Реализация принципа «сверхмультиобработки». Статический и динамический способ создания «общего кода».

- •22.3 СуперЭвм фирмы Fujitsu.

- •23.1 Сравнительные возможности двух методов организации параллельных вычислений: метод конвейеризации и метод параллелизма.

- •Факторы, влияющие на снижение производительности в системах с векторной обработкой команд

- •5. Зависимость по управлению

- •Основные технологии параллельного программирования.

- •62 Реализация фундаментальных вычислительных алгоритмов в линейной сети процессоров.

- •Линейная сеть процессоров

- •Повышение эффективности решения задач на линейной сети процессоров

- •Вычисление параллельного префикса

- •Вычислительные системы с векторной обработкой команд (структура). Диаграмма выполнения операций с векторной обработкой команд.

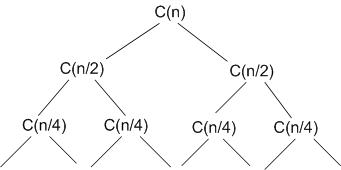

10.3 Принцип «разделяй и властвуй» и его использование для повышения эффективности выполнения вычислительных алгоритмов в сетях процессоров

Этот принцип состоит из трех частей:

р

азделение

задачи на подзадачи;

азделение

задачи на подзадачи;рекурсивное решение этих подзадач;

объединение решений подзадач в единое решение.

Этот принцип представляет собой построение рекурсивного дерева.

Сначала получаем решения на последнем уровне, затем объединяем их. Наиболее типовой задачей здесь является сортировка слиянием. Рассмотрим реализацию такой схемы в линейной сети процессоров.

Исходные данные: 3, 1, 8, 4, 5, 2, 7, 6.

делим данные на 2 последовательности: 3, 1, 8, 4 | 5, 2, 7, 6

проводим упорядочение каждой из подпоследовательности путем циклического сдвига либо на основе алгоритма подсчета ранга каждого из элементов. Каждый из в подпоследовательности получает индекс. 1, 3, 4, 8 | 2, 5, 6, 7

Объединение подпоследовательности в единую:

-

1

3

4

8

2

5

6

7

1

2

3

4

1

2

3

4

0

Каждый

процессор Pi,

![]() ,

«знает», что элемент, который он в данный

момент содержит, является i-м

элементом в подпоследовательности.

,

«знает», что элемент, который он в данный

момент содержит, является i-м

элементом в подпоследовательности.

Для объединения двух подпоследовательностей в единую, надо знать ранги элементов в своей и другой части последовательности.

Основные недостатки:

требуется, чтобы во время каждого рекурсивного шага объединения циклический сдвиг мог выполняться только для одной подпоследовательности;

время выполнения алгоритма соизмеримо со временем реализации tractor thread (т.е. довольно велико).

11.1 Абстрактная архитектура вс. Основные модули и интерфейсы

Архитектура ВС определяет основные функциональные возможности системы, сферу применения (научно-техническая, экономическая, управление и т.д.), режим работы (пакетный, мультипрограммный, разделения времени, диалоговый и т.д.), характеризует параметры ВС (быстродействие, набор и объем памяти, набор периферийных устройств и т.д.), особенности структуры (одно-, многопроцессорная) и т.д. Составные части понятия «архитектура» можно определить следующей схемой

Вычислительные и логические возможности ВС обусловливаются системой команд (СК), характеризующей гибкость программирования, форматами данных и скоростью выполнения операций, определяющих класс задач, наиболее эффективно решаемых на ВС. Система команд ВС, базирующихся на архитектуре фон Неймана. Анализ показывает, что в различных программах чаще всего встречаются достаточно простые команды: команды пересылки и команды процессора с использованием регистров и простых режимов адресации. Не нашли широкого применения и нетрадиционные способы кодирования данных, несмотря на значительные возможности их в плане разработки быстродействующих алгоритмов арифметических операций. Среди них знакоразрядные системы, системы в коде вычетов и др.

Аппаратные средства простой ВС включают в себя модули пяти типов: центральный процессор, основная память, каналы, контроллеры и внешние устройства.

Процессор, в состав которого входят устройство управления (УУ), арифметико-логическое устройство (АЛУ) и память, управляет работой системы и обеспечивает вычисления непосредственно по программе. Так же при помощи процессора организуется выполнение машинных команд, команд ввода-вывода {I/O), обращение к памяти, управление состоянием устройств.

Каналы - специальные устройства, управляющие обменом данных с внешними устройствами. Каналы инициируют свою работу с помощью процессора и затем переходят в автономный режим работы. Это, по сути, спецпроцессор ввода-вывода, обеспечивающий работу внешних устройств, контроль информации и т.д.

Контроллеры ввода-вывода служат для подсоединения внешних устройств (ВнУ) к каналам и обеспечивают обмен управляющей информацией с внешними устройствами, присвоение приоритетов и выдачу информации о состоянии ВнУ для канала, т.е. это устройства управления ВнУ. ВнУ служат для ввода-вывода информации с различных носителей.

Память может быть организована как многоуровневая с различным объемом и временем доступа к ней - сверхоперативная (СОЗУ), оперативная (ОП), внешняя (ВнП) , так и одноуровневая, виртуальная.

Существенное влияние на производительность ВС оказывают каналы ввода-вывода.

Для повышения пропускной способности каналов используют некоторые дополнительные меры, например буферизацию ВнУ путем введения памяти в состав самого устройства или контроллера.

Программное обеспечение является составной частью архитектуры компьютера и существенно влияет на весь вычислительный процесс, в частности позволяет эффективно эксплуатировать аппаратные средства системы.

Операционная система (ОС) управляет ресурсами, разрешает конфликтные ситуации, оптимизирует функционирование системы в целом.