- •Оглавление

- •Сети эвм: понятие, становление, преимущества сетевой обработки данных.

- •Распределение адресного пространства для архивной среды хранения информации.

- •Арифметико-логические устройства и блок ускоренного умножения. Схемы наращивания алу при последовательном и параллельном переносах.

- •Основные характеристики вычислительных сетей.

- •Распределения адресного пространства для физической оперативной памяти с переменными страницами.

- •Архитектура и схемотехника бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры).

- •Классификация вычислительных сетей. Отличия классических lan и gan, тенденция их сближения.

- •1. По территориальной рассредоточенности

- •2. Масштаб предприятия или подразделения, кому принадлежит сеть

- •Организация и принцип работы кэш-памяти. Способы организации кэш-памяти. Обновление информации.

- •Типовые структуры вычислительных сетей.

- •Задача размещения для виртуального адресного пространства.

- •Методы защиты оперативной памяти

- •Методы коммутации в вычислительных сетях. Способы мультиплексирования каналов связи.

- •2. Коммутация сообщений

- •3. Коммутация пакетов

- •Основные задачи управления виртуальной оперативной памятью и их характеристики.

- •Особенности работы с памятью мп I 386. Механизм дескрипторов. Назначение.

- •Задачи системотехнического проектирования сетей эвм

- •Сегментно-страничная схема функционирования виртуальной оперативной памяти

- •Микропроцессоры: общая структура, назначение основных блоков, принцип работы, применение

- •Анализ задержек передачи сообщений в сетях передачи данных

- •Сегментная схема функционирования виртуальной оперативной памяти

- •Способы организации вычислительных систем. Классификация вычислительных систем

- •Задача оптимального выбора пропускных способностей каналов связи (прямая и обратная постановки).

- •Страничная по требованию схема функционирования виртуальной оперативной памяти.

- •Способы организации памяти вычислительных систем.

- •Семиуровневая модель взаимодействия открытых систем. Функции уровней

- •Страничная схема функционирования виртуальной оперативной памяти

- •Система прерываний программ. Функции и назначение.

- •Прохождение данных через уровни модели osi. Функции уровней

- •Сегментно-страничная структуризация памяти

- •Поддержка мультизадачности в мп i386. Сегмент состояния задачи

- •Протоколы и функции канального уровня.

- •Сегментная структуризация памяти.

- •Классификация триггерных схем, примеры, параметры. Основные структуры запоминающих устройств (2d, 3d), структурные методы повышения быстродействия запоминающих устройств.

- •Протоколы повторной передачи. Анализ производительности.

- •Страничная структуризация памяти с переменными страницами

- •Регистры – общие принципы построения, сдвиг информации, способы записи и считывания, параметры.

- •Сдвигающие регистры

- •Универсальные регистры

- •Протоколы и функции сетевого уровня. Таблицы маршрутизации.

- •Страничная структуризация памяти с фиксированными страницами

- •Принципы построения счетчиков, суммирующие и вычитающие счетчики, логическая структура, параметры

- •Классификация алгоритмов маршрутизации

- •По способу выбора наилучшего маршрута.

- •По способу построения таблиц маршрутизации

- •По месту выбора маршрутов (маршрутного решения)

- •По виду информации которой обмениваются маршрутизаторы

- •Многоочередная дисциплина обслуживания процессов с различными приоритетами в ос

- •Устройства кодирования и декодирования цифровой информации, примеры практической реализации схем и их функционирование

- •5. Кодирование текстовой информации

- •Задача оптимальной статической маршрутизации

- •Многоочередная дисциплина обслуживания процессов с равными приоритетами в ос.

- •Логическая основа построения сумматоров, способы организации переноса, пример практической реализации

- •Стек тср/ip. Протоколы прикладного уровня.

- •Дисциплины распределения ресурсов в ос: fifo, lifo и круговой циклический алгоритм, их достоинства и недостатки.

- •Классификация системы логических элементов, типовые схемы, параметры и характеристики

- •Вопрос 2.

- •Системы адресации в стеке тср/ip.

- •Концепция "виртуализации" в ос

- •1.Паравиртуализация

- •2.Трансляция двоичного кода

- •3.Виртуализация процессора

- •4.Виртуализацимя памяти

- •5.Виртализация ввода/вывода

- •1 Подход:

- •2 Подход:

- •Принципы построения счетчиков, суммирующие и вычитающие счетчики, логическая структура, параметры

- •Простейший суммирующий асинхронный счётчик

- •Простейший вычитающий асинхронный счётчик

- •Протокол ip. Протокол ip – internetprotocol

- •Структура информации заголовка ip

- •Понятие "ресурс" в ос. Классификация ресурсов.

- •Классификация триггерных схем, примеры, параметры. Основные структуры запоминающих устройств (2d, 3d), структурные методы повышения быстродействия запоминающих устройств.

- •Классификация триггеров

- •Структура 2d

- •Структура 3d

- •Структурные методы повышения быстродействия запоминающих устройств

- •Свойства и классификация процессов в ос.

- •Микропроцессоры: общая структура, назначение основных блоков, принцип работы, применение

- •Десятичный корректор, аккумулятор, регистр аккумулятора и временного хранения и регистр признаков.

- •Протокол tcp.

- •Смена состояний процессов в ос. Диспетчеризация и управление процессами.

- •Организация и принцип работы кэш-памяти. Способы организации кэш-памяти. Обновление информации

- •Алгоритм выполнения операции передачи слова из кэш в процессор

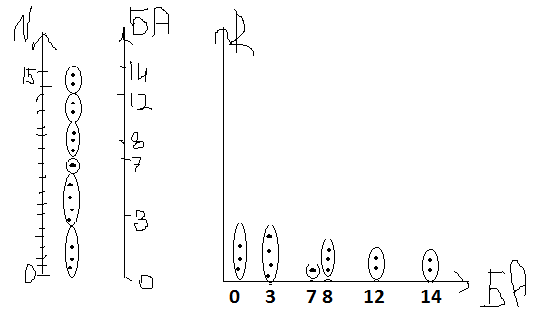

Распределения адресного пространства для физической оперативной памяти с переменными страницами.

Схема структурирования страницами переменной длины

Первое адресное пространство по тем же правилам, что и в первом случае.

Другие ограничения на размеры страницы. Размер страницы может изменяется, то есть каждая страница 1≤l≤L. При этом верхняя граница диапазона L=2m<n.

На первом этапе структуризации: адреса из ИАП группируются в страницы, при этом страницы имеют различный размер.

На втором этапе: перенумерация адресов внутри страницы. Поскольку в данном случае адреса страниц не будут кратны двум, нумерация страниц не имеет смысла. Вместо номеров каждой страницы присваиваются уникальные имена (и цифры, и буквы). При этом в каждой странице в соответствие ставится базовый адрес, то есть адрес начала страницы в исходном адресном пространстве. Как и в предыдущем случаем, получаем двухмерное адресное пространство, но это АП характеризуется другими показателями А= (БА,R). Реальный исходный адрес А = БАi+R. Прямого преобразования не существует.

В данном варианте структуризации нет однозначного соответствия между исходных и структурированным пространствами. Единственный корректный переход возможен от структурированного пространства к исходному A=БАi+R. Обратный переход возможен только в момент структуризации исходного адресного пространства.

Архитектура и схемотехника бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры).

Сложные программируемые логические устройства (CPLD)

Структура CPLD

CPLD состоят из программируемой матрицы соединений ПМС, множества функциональных блоков ФБ, подобных ПМЛ (PAL), и блоков ввода/вывода БВВ.

В целом, CPLD представляет собою объединение нескольких PAL (ПМЛ) в единое устройство средствами программируемой коммутационной матрицы. Кроме основных блоков CPLD на схеме показаны контроллеры интерфейса JTAG и ISP, используемые для конфигурирования и тестирования создаваемых структур.

Число ФБ, сходящих в состав CPLD, изменяется в широких приделах в зависимости от сложности данной микросхемы. Каждый ФБ получает по m сигналов от ПМС, выходы ФБ, число которых n, подключены как к программируемой матрице соединений ПМС, так и к блокам ввода/вывода БВВ. БВВ связаны с внешними двунаправленными выводами. Три вывода специализированы и предназначены для глобальных, т.е. общих для всей схемы, сигналов тактирования GCK (Global Clock), сброса/установки GSR (Global Set/Reset), управления третьим состоянием GTS (Global Tri State). Возможно и иное использование специализированых выводов, если они не применяются по назначению. Число контактов ввода/вывода может быть меньше числа выводов всех ФБ. В этом случае часть макроячеек может быть использована только для выработки внутренних сигналов устройства, потребность в которых типична для многих видов устройств.

CPLD – более простые устройства в сравнении с FPGA и другими ПЛИС высшего уровня сложности. На них удобно строить относительно несложные устройства высокого быстродействия, в которых не требуется реализации сложных вычислительных алгоритмов. Примерами таких устройств могут служить интерфейсные схемы или управляющие автоматы.

Программируемые пользователем вентильные матрицы (FPGA)

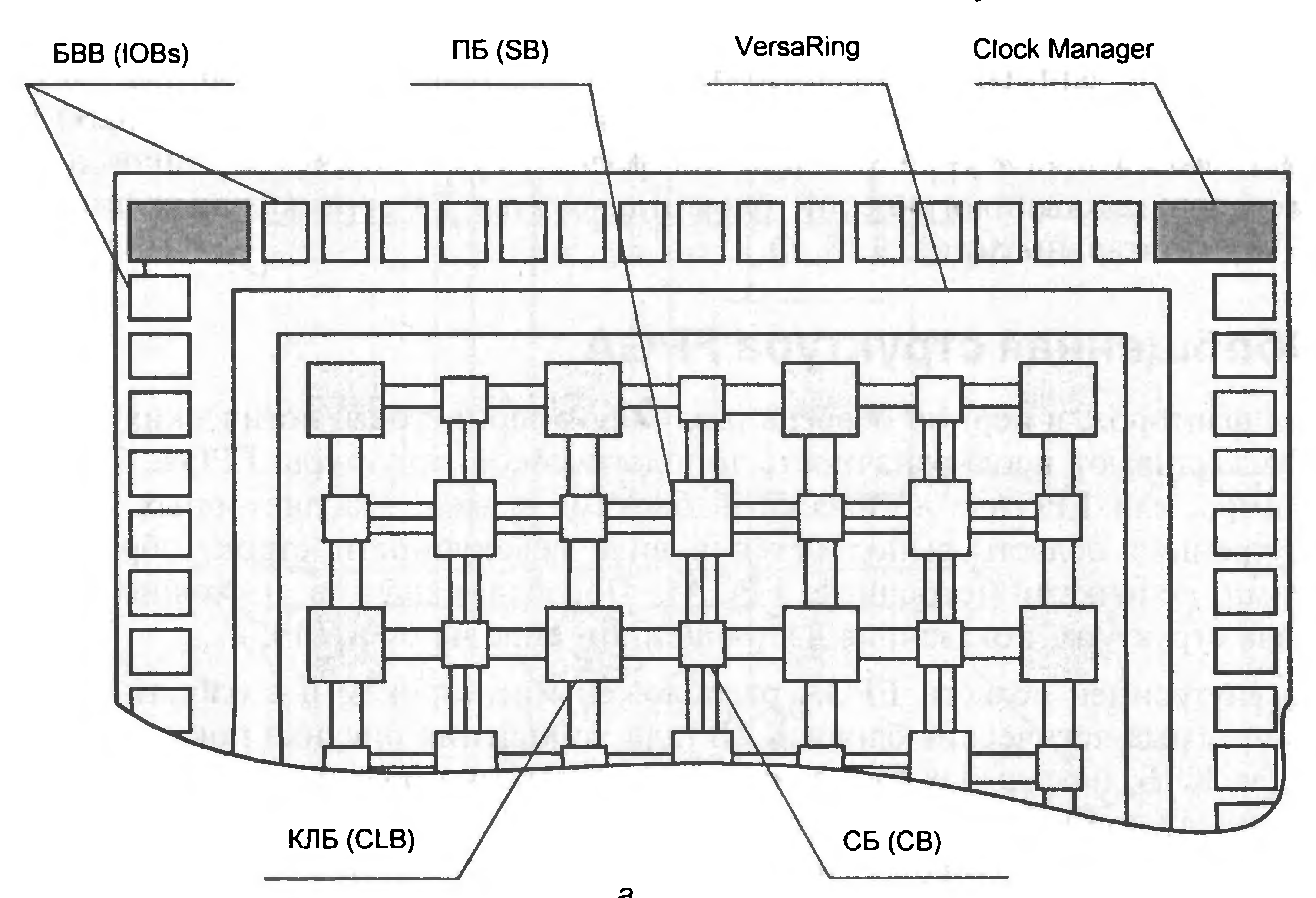

Ряд факторов, в первую очередь различия в зернистости логических блоков, обуславливают неоднородность топологической структуры FPGA. Преобладающей в настоящее время стала структура, показанная в упрощённом виде на рис. 9.19, а.

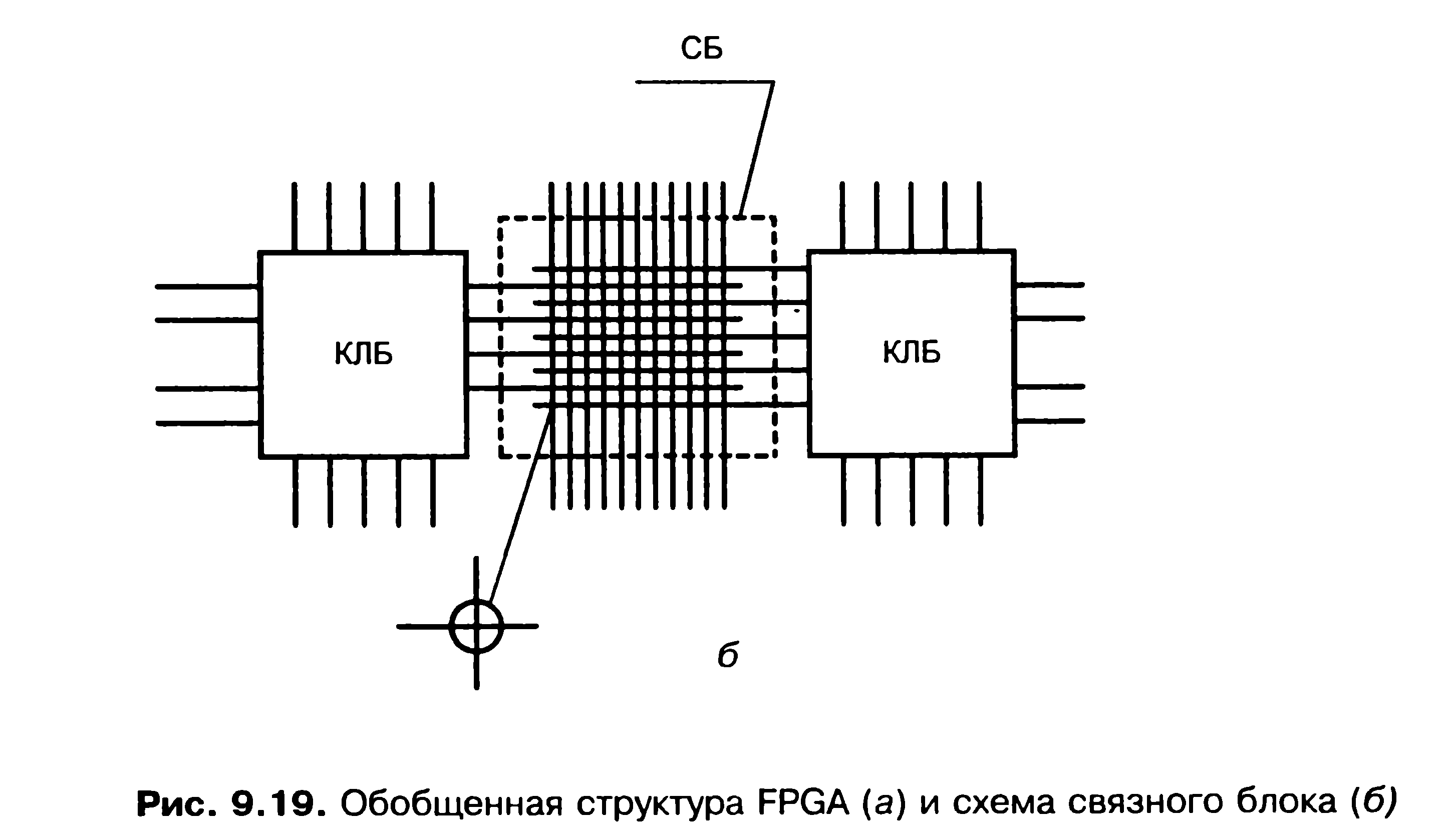

Во внутренней области FPGA расположены по строкам и столбцам конфигурируемые логические блоки КЛБ. Кроме КЛБ FPGA содержит переключательные блоки ПБ и связанные блоки СБ, обеспечивающие коммутацию КЛБ.

Связные блоки реализуют соединения выводов КЛБ с линиями вертикальных и горизонтальных трассировочных каналов общего назначения. Схема СБ показана увеличено на рис. 9.19, б на примере связей двух соседних по горизонтали КЛБ с вертикальным трассировочным каналом. На пересечении линии выводов КЛБ с линиями каналов размещаются программируемые точки связей, одна из которых показана кружком в укрупнённом виде. Программируемые точки связей имеются во всех пересечениях, но во избежание загромождения рисунка они не изображены. С помощью СБ сигналы КЛБ выводятся в трассировочные каналы.

Переключательные блоки коммутируют линии трассировки каналов. Они позволяют переключить линии передачи сигналов, поступающих в блок, на любое направление (прямо, влево, вправо).

Средства коммутации, связанные с БВВ, сведены в так называемый VersaRing, окружающий внутреннюю область кристалла. Они связывают БВВ с каналами трассировки КЛБ. С помощью средства VersaRing можно перераспределять внешние контакты микросхемы относительно выводов, сформированных во внутренней области кристалла. Это повышает функциональную гибкость и универсальность FPGA, при модификациях проекта позволяет сохранять неизменной распайку контактов микросхемы на плате.

СБИС программируемой логики с комбинированными архитектурами

Стремление объединить достоинства CPLD и FPGA привело к разработке микросхем комбинированной архитектуры.

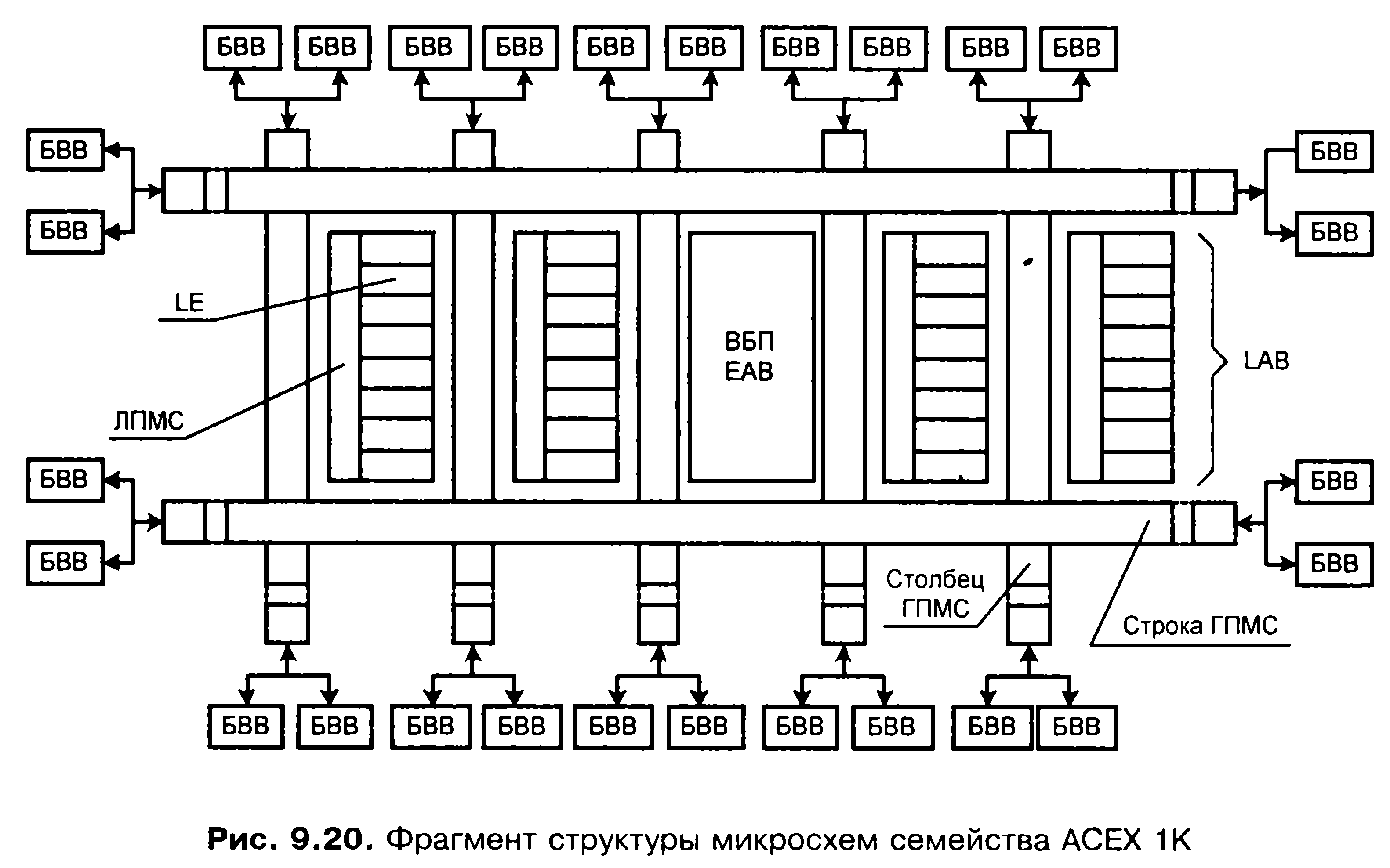

Структура СБИС ПЛ с комбинированными архитектурами

В микросхему входят логические блоки LABs, содержащие логические элементы Les и локальную программируемую матрицу соединений (ЛПМС) для внутриблочной коммутации логических элементов. Межблочная коммутация реализуется строками и столбцами глобальной программируемой матрицы соединений (ГПМС). При большом числе логических элементов применение единой одноуровневой системы коммутации было бы затруднительным, что и объясняет двухуровневый характер принятой в микросхеме коммутации. К концам строк и столбцов ГПМС подключаются блоки ввода/вывода.

Блоки ВБП могут быть ориентированы на реализацию буферов FIFO, иногда на построение двухпортовой памяти, ассоциативной памяти и др. Отдельные ВБП могут объединяться для создания более ёмкой памяти и применяться не только для хранения данных, но и как табличные преобразователи для воспроизведения сложных функций с числом аргументов 8 – 10.

Комбинирование признаков CPLD и FPGA в структуре микросхем ACEX 1K выражается в следующем:

Логические блоки расположены по строкам и столбцам и содержат логические элементы LUT-типа (табличные функциональные преобразователи), что характерно для FPGA;

Коммутация логических элементов в пределах логического блока осуществляется с помощью программируемой матрицы не сегментированных соединений, что характерно для CPLD, а коммутация самих логических блоков LAB производится с помощью ГПМС, относящийся к числу специальных трассировочных средств, называемых FTI, которые хотя и имеют горизонтальные и вертикальные каналы, но не используют в них сегментированных линий.