- •Оглавление

- •Сети эвм: понятие, становление, преимущества сетевой обработки данных.

- •Распределение адресного пространства для архивной среды хранения информации.

- •Арифметико-логические устройства и блок ускоренного умножения. Схемы наращивания алу при последовательном и параллельном переносах.

- •Основные характеристики вычислительных сетей.

- •Распределения адресного пространства для физической оперативной памяти с переменными страницами.

- •Архитектура и схемотехника бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры).

- •Классификация вычислительных сетей. Отличия классических lan и gan, тенденция их сближения.

- •1. По территориальной рассредоточенности

- •2. Масштаб предприятия или подразделения, кому принадлежит сеть

- •Организация и принцип работы кэш-памяти. Способы организации кэш-памяти. Обновление информации.

- •Типовые структуры вычислительных сетей.

- •Задача размещения для виртуального адресного пространства.

- •Методы защиты оперативной памяти

- •Методы коммутации в вычислительных сетях. Способы мультиплексирования каналов связи.

- •2. Коммутация сообщений

- •3. Коммутация пакетов

- •Основные задачи управления виртуальной оперативной памятью и их характеристики.

- •Особенности работы с памятью мп I 386. Механизм дескрипторов. Назначение.

- •Задачи системотехнического проектирования сетей эвм

- •Сегментно-страничная схема функционирования виртуальной оперативной памяти

- •Микропроцессоры: общая структура, назначение основных блоков, принцип работы, применение

- •Анализ задержек передачи сообщений в сетях передачи данных

- •Сегментная схема функционирования виртуальной оперативной памяти

- •Способы организации вычислительных систем. Классификация вычислительных систем

- •Задача оптимального выбора пропускных способностей каналов связи (прямая и обратная постановки).

- •Страничная по требованию схема функционирования виртуальной оперативной памяти.

- •Способы организации памяти вычислительных систем.

- •Семиуровневая модель взаимодействия открытых систем. Функции уровней

- •Страничная схема функционирования виртуальной оперативной памяти

- •Система прерываний программ. Функции и назначение.

- •Прохождение данных через уровни модели osi. Функции уровней

- •Сегментно-страничная структуризация памяти

- •Поддержка мультизадачности в мп i386. Сегмент состояния задачи

- •Протоколы и функции канального уровня.

- •Сегментная структуризация памяти.

- •Классификация триггерных схем, примеры, параметры. Основные структуры запоминающих устройств (2d, 3d), структурные методы повышения быстродействия запоминающих устройств.

- •Протоколы повторной передачи. Анализ производительности.

- •Страничная структуризация памяти с переменными страницами

- •Регистры – общие принципы построения, сдвиг информации, способы записи и считывания, параметры.

- •Сдвигающие регистры

- •Универсальные регистры

- •Протоколы и функции сетевого уровня. Таблицы маршрутизации.

- •Страничная структуризация памяти с фиксированными страницами

- •Принципы построения счетчиков, суммирующие и вычитающие счетчики, логическая структура, параметры

- •Классификация алгоритмов маршрутизации

- •По способу выбора наилучшего маршрута.

- •По способу построения таблиц маршрутизации

- •По месту выбора маршрутов (маршрутного решения)

- •По виду информации которой обмениваются маршрутизаторы

- •Многоочередная дисциплина обслуживания процессов с различными приоритетами в ос

- •Устройства кодирования и декодирования цифровой информации, примеры практической реализации схем и их функционирование

- •5. Кодирование текстовой информации

- •Задача оптимальной статической маршрутизации

- •Многоочередная дисциплина обслуживания процессов с равными приоритетами в ос.

- •Логическая основа построения сумматоров, способы организации переноса, пример практической реализации

- •Стек тср/ip. Протоколы прикладного уровня.

- •Дисциплины распределения ресурсов в ос: fifo, lifo и круговой циклический алгоритм, их достоинства и недостатки.

- •Классификация системы логических элементов, типовые схемы, параметры и характеристики

- •Вопрос 2.

- •Системы адресации в стеке тср/ip.

- •Концепция "виртуализации" в ос

- •1.Паравиртуализация

- •2.Трансляция двоичного кода

- •3.Виртуализация процессора

- •4.Виртуализацимя памяти

- •5.Виртализация ввода/вывода

- •1 Подход:

- •2 Подход:

- •Принципы построения счетчиков, суммирующие и вычитающие счетчики, логическая структура, параметры

- •Простейший суммирующий асинхронный счётчик

- •Простейший вычитающий асинхронный счётчик

- •Протокол ip. Протокол ip – internetprotocol

- •Структура информации заголовка ip

- •Понятие "ресурс" в ос. Классификация ресурсов.

- •Классификация триггерных схем, примеры, параметры. Основные структуры запоминающих устройств (2d, 3d), структурные методы повышения быстродействия запоминающих устройств.

- •Классификация триггеров

- •Структура 2d

- •Структура 3d

- •Структурные методы повышения быстродействия запоминающих устройств

- •Свойства и классификация процессов в ос.

- •Микропроцессоры: общая структура, назначение основных блоков, принцип работы, применение

- •Десятичный корректор, аккумулятор, регистр аккумулятора и временного хранения и регистр признаков.

- •Протокол tcp.

- •Смена состояний процессов в ос. Диспетчеризация и управление процессами.

- •Организация и принцип работы кэш-памяти. Способы организации кэш-памяти. Обновление информации

- •Алгоритм выполнения операции передачи слова из кэш в процессор

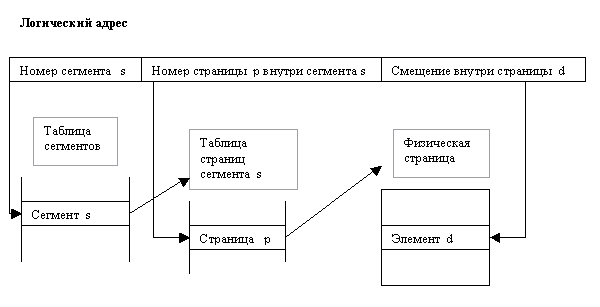

Сегментно-страничная структуризация памяти

Исходное непрерывное адресное пространство сначала подвергается структурированию фиксированными страницами. Далее сегмент рассматривается уже как некоторая непрерывная последовательность номеров страниц в промежуточном странично-структурированном адресном пространстве. Размер сегмента — это количество страниц, входящих в состав сегмента. Каждый сегмент также имеет свой уникальный номер s. Затем в пределах каждого сегмента происходит перенумерация страниц, начиная с нуля в возрастающем порядке. Поскольку размеры сегментов (в количестве страниц) различны, то по номеру сегмента (если проводить нумерацию сегментов в возрастающем порядке) невозможно определить его базовый адрес. Поэтому при формировании сегмента в адресном пространстве ему должен быть назначен базовый адрес As0. Адрес в полученном сегментно-структурированном адресном пространстве задается с помощью четырех координат: s — номер сегмента; Аs0 — базовый адрес сегмента; R' — номер страницы в пределах сегмента; R — смещение в пределах страницы.

Для перехода от такого структурного адреса к непрерывному необходимо сначала выполнить операцию соответствия, т. е. назначить сегменту базовый адрес Аs0. Затем, используя операцию «база — плюс — смещение», найти базовый адрес страницы в составе сегмента: AR’=As0 + R'L. Далее, к найденному базовому адресу страницы необходимо применить операцию конкатенации — присоединить значение смещения, если размер страницы был кратен 2.

При сегментно-страничной организации виртуальной памяти происходит двухуровневая трансляция виртуального адреса в физический. В этом случае виртуальный адрес состоит из трех полей: номера сегмента виртуальной памяти, номера страницы внутри сегмента и смещения внутри страницы. Соответственно, используются две таблицы отображения - таблица сегментов, связывающая номер сегмента с таблицей страниц, и отдельная таблица страниц для каждого сегмента.

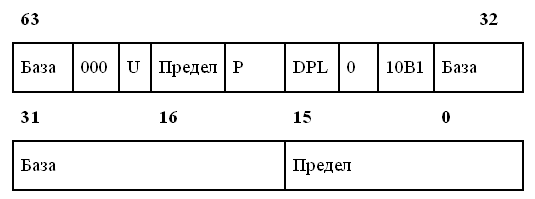

Поддержка мультизадачности в мп i386. Сегмент состояния задачи

В процессорах i386+ поддерживается аппаратные средства мультизадачности. Процедура переключения задач во многом аналогична процедуре прерываний.

Мультизадачность однопроцессорной среды реализуется через механизм разделения времени, т.е. каждой задаче выделяется квант времени и создаётся иллюзия параллельности выполняющихся программ. Переключение задач в общем случае похоже на вызовы, но при этом хранится больше информации. Для поддержки мультизадачности в МП i386+ используется: TSS, дескриптор TSS, регистр задач и дескриптор шлюза задач. TSS служит для сохранения информации о задаче. Это сегмент данных для считывания и записи, к которому может обратиться только МП (доступ программы к нему запрещен). TSS определяется дескриптором.

U – User. B – бит занятости (Busy) – активна ли задача в данный момент. Предел-процессор может интерпретировать это поле двумя способами в зависимости от значения поля G (гранулярность).Если G = 0, то предел задает размер сегмента в байтах (от 1 байта до 1 Мбайта).Если G = 1, то предел задает размер сегмента в 4-Кбайтных параграфах (от 4 Кбайт до 4 Гбайт). DPL определяет того, кто имеет возможность переключения задач (обычно = 0). Бит присутствия сегмента в физической памяти. В-Бит размерности присутствует в дескрипторах сегментов данных. Он управляет следующими аспектами операций.Размерностью регистра указателя для стековых сегментов. Если B = 1, используется 32-битный указатель ESP. Если B = 0 — 16-битный указатель SP. База-задает положение сегмента в 4 Гбайтном (16М для Intel286) адресном пространстве.

Верхней границей расширяемого вниз сегмента. В расширяемых вниз сегментах нижняя граница задается полем LIMIT, а верхняя равна FFFFFFFFh, если B = 1, и FFFFh, если B = 0. Дескрипторы TSS размещается только в GDT и выбирается селектором, который находится в регистре TR.

Одновременно реализуется одна задача (процесс). Ей соответствует контекст (среда). Специальных команд переключения задач нет. Используются команды межсегментного перехода (JMP) или межсегментного вызова (CALL), а также прерывания, в том числе, особые случаи. JMP и CALL могут быть прямые — сразу с выходом на дескриптор TSS (сегмента состояния задачи) в GDT или косвенные — черезшлюз задачи ШЗ (в IDT). Переключение задач по прерываниям — только косвенное — через ШЗ. Обычный вызов подпрограммы CALL сохраняет содержимое нужных регистров в стеке, программы могут быть реентрантными (обладающими свойством повторной входимости). При переключении задач по CALL создается новая среда, содержимое EFLAGS сохраняется, но не в стеке, а в сегменте TSS. Задачи нереентрантны.

Различают два варианта сегмента TSS — 16- и 32-битный. В 16-битном размещается содержимое 8 регистров общего назначения (AX, BX, CX, DX, BP, SP, SI, DI), 4 сегментных регистров (CS, SS, DS, ES), 2 регистров IP, FLAGS, системного регистра LDT (LDTR), селектора адреса возврата («Обратная связь»), 3 пары (SS, SP) для 3 стеков. Три стека используются в связи с четырьмя уровнями (кольцами) привилегий так называемой защиты памяти по привилегиям — 0, 1, 2, 3.

Процедура переключения задач («выходящая» задача сменяется «входящей» задачей) связана с изменением содержимого системного регистра TR. Там будет находиться селектор виртуального адреса TSS. Индекс из этого селектора адресует дескриптор TSS (в GDT), сначала старый, потом — новый. Под управлением старого DTSS происходит выгрузка регистрового контекста в сегмент TSS выходящей задачи, а затем — под управлением нового DTSS — загрузка в регистры содержимого соответствующих элементов сегмента TSS входящей задачи.