- •Оглавление

- •Сети эвм: понятие, становление, преимущества сетевой обработки данных.

- •Распределение адресного пространства для архивной среды хранения информации.

- •Арифметико-логические устройства и блок ускоренного умножения. Схемы наращивания алу при последовательном и параллельном переносах.

- •Основные характеристики вычислительных сетей.

- •Распределения адресного пространства для физической оперативной памяти с переменными страницами.

- •Архитектура и схемотехника бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры).

- •Классификация вычислительных сетей. Отличия классических lan и gan, тенденция их сближения.

- •1. По территориальной рассредоточенности

- •2. Масштаб предприятия или подразделения, кому принадлежит сеть

- •Организация и принцип работы кэш-памяти. Способы организации кэш-памяти. Обновление информации.

- •Типовые структуры вычислительных сетей.

- •Задача размещения для виртуального адресного пространства.

- •Методы защиты оперативной памяти

- •Методы коммутации в вычислительных сетях. Способы мультиплексирования каналов связи.

- •2. Коммутация сообщений

- •3. Коммутация пакетов

- •Основные задачи управления виртуальной оперативной памятью и их характеристики.

- •Особенности работы с памятью мп I 386. Механизм дескрипторов. Назначение.

- •Задачи системотехнического проектирования сетей эвм

- •Сегментно-страничная схема функционирования виртуальной оперативной памяти

- •Микропроцессоры: общая структура, назначение основных блоков, принцип работы, применение

- •Анализ задержек передачи сообщений в сетях передачи данных

- •Сегментная схема функционирования виртуальной оперативной памяти

- •Способы организации вычислительных систем. Классификация вычислительных систем

- •Задача оптимального выбора пропускных способностей каналов связи (прямая и обратная постановки).

- •Страничная по требованию схема функционирования виртуальной оперативной памяти.

- •Способы организации памяти вычислительных систем.

- •Семиуровневая модель взаимодействия открытых систем. Функции уровней

- •Страничная схема функционирования виртуальной оперативной памяти

- •Система прерываний программ. Функции и назначение.

- •Прохождение данных через уровни модели osi. Функции уровней

- •Сегментно-страничная структуризация памяти

- •Поддержка мультизадачности в мп i386. Сегмент состояния задачи

- •Протоколы и функции канального уровня.

- •Сегментная структуризация памяти.

- •Классификация триггерных схем, примеры, параметры. Основные структуры запоминающих устройств (2d, 3d), структурные методы повышения быстродействия запоминающих устройств.

- •Протоколы повторной передачи. Анализ производительности.

- •Страничная структуризация памяти с переменными страницами

- •Регистры – общие принципы построения, сдвиг информации, способы записи и считывания, параметры.

- •Сдвигающие регистры

- •Универсальные регистры

- •Протоколы и функции сетевого уровня. Таблицы маршрутизации.

- •Страничная структуризация памяти с фиксированными страницами

- •Принципы построения счетчиков, суммирующие и вычитающие счетчики, логическая структура, параметры

- •Классификация алгоритмов маршрутизации

- •По способу выбора наилучшего маршрута.

- •По способу построения таблиц маршрутизации

- •По месту выбора маршрутов (маршрутного решения)

- •По виду информации которой обмениваются маршрутизаторы

- •Многоочередная дисциплина обслуживания процессов с различными приоритетами в ос

- •Устройства кодирования и декодирования цифровой информации, примеры практической реализации схем и их функционирование

- •5. Кодирование текстовой информации

- •Задача оптимальной статической маршрутизации

- •Многоочередная дисциплина обслуживания процессов с равными приоритетами в ос.

- •Логическая основа построения сумматоров, способы организации переноса, пример практической реализации

- •Стек тср/ip. Протоколы прикладного уровня.

- •Дисциплины распределения ресурсов в ос: fifo, lifo и круговой циклический алгоритм, их достоинства и недостатки.

- •Классификация системы логических элементов, типовые схемы, параметры и характеристики

- •Вопрос 2.

- •Системы адресации в стеке тср/ip.

- •Концепция "виртуализации" в ос

- •1.Паравиртуализация

- •2.Трансляция двоичного кода

- •3.Виртуализация процессора

- •4.Виртуализацимя памяти

- •5.Виртализация ввода/вывода

- •1 Подход:

- •2 Подход:

- •Принципы построения счетчиков, суммирующие и вычитающие счетчики, логическая структура, параметры

- •Простейший суммирующий асинхронный счётчик

- •Простейший вычитающий асинхронный счётчик

- •Протокол ip. Протокол ip – internetprotocol

- •Структура информации заголовка ip

- •Понятие "ресурс" в ос. Классификация ресурсов.

- •Классификация триггерных схем, примеры, параметры. Основные структуры запоминающих устройств (2d, 3d), структурные методы повышения быстродействия запоминающих устройств.

- •Классификация триггеров

- •Структура 2d

- •Структура 3d

- •Структурные методы повышения быстродействия запоминающих устройств

- •Свойства и классификация процессов в ос.

- •Микропроцессоры: общая структура, назначение основных блоков, принцип работы, применение

- •Десятичный корректор, аккумулятор, регистр аккумулятора и временного хранения и регистр признаков.

- •Протокол tcp.

- •Смена состояний процессов в ос. Диспетчеризация и управление процессами.

- •Организация и принцип работы кэш-памяти. Способы организации кэш-памяти. Обновление информации

- •Алгоритм выполнения операции передачи слова из кэш в процессор

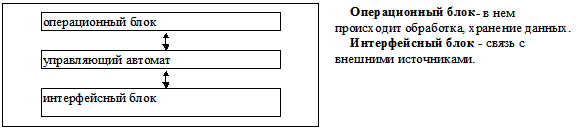

Микропроцессоры: общая структура, назначение основных блоков, принцип работы, применение

Назначение. Принцип работы.

Процессором - называется устройство, непосредственно осуществляющее процесс обработки данных и программное управление этим процессом. Процессор дешифрует и выполняет команды программ, организует обращение к ОП, инициирует работу ПУ, воспринимает и обрабатывает внешние события.

Процессор осуществляет управление взаимодействием всех устройств ЭВМ. (при наличии специальных процессоров эти функции рассредотачиваются).

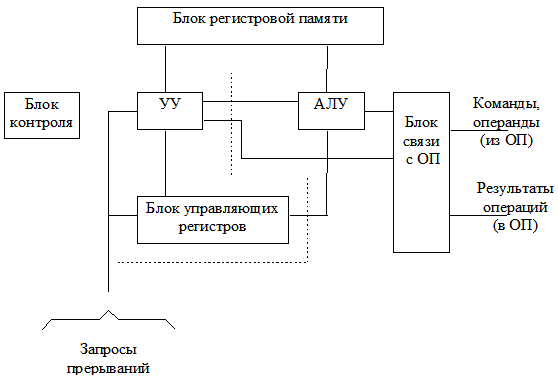

Общая функциональная структура МП.

Структурная схема процессора:

Разъяснения к структурной схеме:

- ОП обычно не входит в состав МП и реализуется внешними схемами, но в небольших ЭВМ, ОЭВМ может совмещаться с ЦП.

- АЛУ процессора выполняет логические, арифметические операции над данными. В МП может имеется одно универсальное АЛУ для всех операций или несколько специальных АЛУ для отдельных видов операций.

- УУ вырабатывает последовательность управляющих сигналов, инициирующих выполнение соответствующей последовательности микроопераций обеспечивающей реализацию текущей команды.

- Блок управляющих регистров предназначен для временного хранения управляющей информации. Он содержит регистры и счетчики, участвующие в управлении вычислительным процессом: состояние МП, регистр - счетчик адреса команды, счетчики тактов, регистр запросов прерываний.

- Блок регистровой памяти - местная память более высокого быстродействия чем ОП. Регистры этого блока служат для хранения операндов, в качестве аккумуляторов, базовых и индексных регистров, указателя стека.

- Блок связи с ОП организует обмен информацией процессора с ОП и защиту участков ОП от недозволенных данной программе обращений, а также связь МП с ПУ.

- Блок контроля и диагностики служит для обнаружения сбоев и отказов в аппаратуре МП, восстановление работы программы после сбоев и поиска места неисправности при отказах.

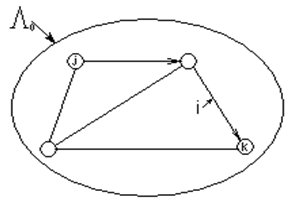

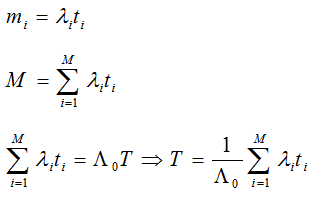

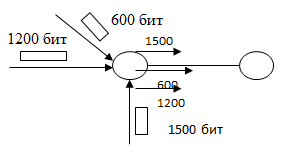

Анализ задержек передачи сообщений в сетях передачи данных

Сеть передачи данных (СПД) – это совокупность средств вычислительной техники, центров коммутации (ЦК) + совокупность средств передачи данных, каналов связи (КС). СПД – ядро вычислительной сети, она обеспечивает взаимодействие между абонентами сети, в качестве которых могут выступать как отдельные вычислительные сети, так и отдельные пользователи.

Анализ средних задержек передачи данных в СПД.

Дано:

Количества и места размещения ЦК (N)

Топология

Количество каналов связи (M)

l – средняя длина пакета

γjk – интенсивность передачи пакетов абонентами узла j абонентам узла k

стратегия маршрутизации – фиксированная. Это значит, что абонент J передает K информацию только по одному маршруту.

При этом предполагаем, что все КС бесшумные и надежные. Все ЦК надежные и время обработки в ЦК ť≈0 (прием пакета и обработка заголовка) Буферная память в ЦК не ограничена.

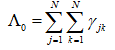

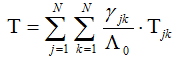

-

суммарная интенсивность внешнего

потока, поступающего в сеть.

-

суммарная интенсивность внешнего

потока, поступающего в сеть.

Обозначим:

λi – интенсивность поступления пакетов в i-ый КС. I=1,M

-

суммарная интенсивность внутренних

потоков.

-

суммарная интенсивность внутренних

потоков.

Определить среднее время передачи пакетов в СПД T - ?

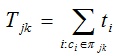

Tjk – среднее время передачи пакетов из узла j в узел k, тогда

pjk – маршрут из j в k (p - это которая 3,14)

сi pjk – маршрут из j в k проходит через iый канал связи

ti – время задержки в этом КС (время ожидания передачи пакета + время передачи пакета)

Тогда

-

сумма времен задержек в каналах, по

которым проходит пакет.

-

сумма времен задержек в каналах, по

которым проходит пакет.

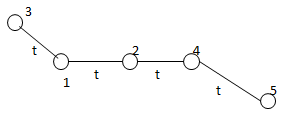

![]() -

сумма потоков, проходящих через i-ый

КС

-

сумма потоков, проходящих через i-ый

КС

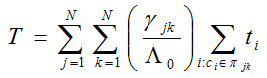

меняем сумму с одновременной заменой условий

T12=t2 T13=t1 T14=t2+t3 T15=t2+t3+t4 …

Пусть Λ0=1

Для системы в целом: среднее число пакетов в сети

![]()

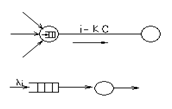

Для i-го КС

Как определить ti - ?

bi=l/Ci

i-КС G/G/1 – не можем рассчитать=> М/М/1

Предположения Клейнрока

Считать, что поток сообщений, поступающий в i-КС образует простейший поток. (Если складывать непростейшие потоки, то в сумме получится поток, близкий к простейшему )

G/G/1 => M/G/1

Каждый раз, когда сообщение приходит в ЦК разыграть его новую длину в соответствии с экспоненциальным распределением со средним значением 1.