- •Оглавление

- •Глава 1. Техническая часть. Разработка циклического таймера 10

- •Глава 2. Охрана труда 40

- •Введение

- •Глава 1. Техническая часть. Разработка циклического таймера

- •1.1Аналитический обзор по теме

- •1.1.1 Постановка задачи

- •1.1.2 Таймер

- •1 .1.3 Функциональная схема устройства

- •1.1.4Элементная база устройства

- •Р асположение выводов aTtiny2313:

- •Микросхема m74hc595

- •Индикатор gnq-5641

- •Сглаживающие фильтры

- •Псофометрический коэффициент помех

- •Коэффициент сглаживания

- •Индуктивный сглаживающий фильтр

- •Стабилизатор напряжения

- •Линейный стабилизатор

- •Трансформатор

- •Базовые принципы действия трансформатора

- •Катушки индуктивности

- •Характеристики катушки индуктивности

- •1.1.5 Принципиальная схема устройства

- •1.2 Практическая часть

- •1.2.1 Построение печатной платы в Sprint Layout

- •1.2.2Перенос схемы из программы на глянцевую бумагу

- •1.2.3 Подготовка текстолита

- •Нанесение рисунка на текстолит

- •1.2.4 Монтаж компонентов на печатную плату

- •Глава 2. Охрана труда Меры безопасности при техническом обслуживании электронной техники

- •2.1 Характеристики санитарно-гигиенических условий труда Гигиеническая оценка условий и характера труда

- •Анализ условий труда

- •2.2 Электробезопасность. Требования безопасности при работе с электрооборудованием

- •Требования безопасности при работе с электрооборудованием

- •2.3 Требования пожарной безопасности

- •Заключение

- •Список литературы

Р асположение выводов aTtiny2313:

Рис.2. расположение ножек микросхемы

Общее описание:

ATtiny2313 – низкопотребляющий 8 битный КМОП микроконтроллер с AVR RISC архитектурой. Выполняя команды за один цикл, Attiny2313 достигает производительности 1 MIPS при частоте задающего генератора 1 МГц, что позволяет разработчику оптимизировать отношение потребления к производительности.

AVR ядро объединяет богатую систему команд и 32 рабочих регистра общего назначения. Все 32 регистра непосредственно связаны с арифметико-логическим устройством (АЛУ), что позволяет получить доступ к двум независимым регистрам при выполнении одной команды. В результате эта архитектура позволяет обеспечить в десятки раз большую производительность, чем стандартная CISC архитектура.

Attiny2313 имеет следующие характеристики: 2 КБ программируемой в системе Flash память программы, 128 байтную EEPROM память данных, 128 байтное SRAM (статическое ОЗУ), 18 линий ввода – вывода общего применения, 32 рабочих регистра общего назначения, однопроводный интерфейс для встроенного отладчика, два гибких таймера/счетчика со схемами сравнения, внутренние и внешние источники прерывания, последовательный программируемый USART, универсальный последовательный интерфейс с детектором стартового условия, программируемый сторожевой таймер со встроенным генератором и три программно инициализируемых режима пониженного потребления. В режиме Idle останавливается ядро, но ОЗУ, таймеры/счетчики и система прерываний продолжают функционировать. В режиме Power-down регистры сохраняют свое значение, но генератор останавливается, блокируя все функции прибора до следующего прерывания или аппаратного сброса. В Standby режиме задающий генератор работает, в то время как остальная часть прибора бездействует. Это позволяет очень быстро запустить микропроцессор, сохраняя при этом в режиме бездействия мощность.

Прибор изготовлен по высокоплотной энергонезависимой технологии изготовления памяти компании Atmel. Встроенная ISP Flash позволяет перепрограммировать память программы в системе через последовательный SPI интерфейс или обычным программатором энергонезависимой памяти. Объединив в одном кристалле 8- битное RISC ядро с самопрограммирующейся в системе Flash памятью, Attiny2313 стал мощным микроконтроллером, который дает большую гибкость разработчика микропроцессорных систем.

Attiny2313 поддерживается различными программными средствами и интегрированными средствами разработки, такими как компиляторы C, макроассемблеры, программные отладчики/симуляторы, внутрисхемные эмуляторы и ознакомительные наборы.

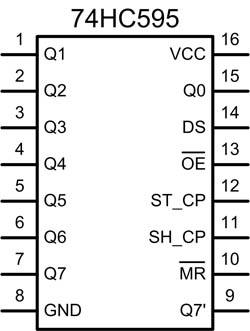

Микросхема m74hc595

Микросхема 74HC595 содержит 8 битный регистр хранения и 8 битный сдвиговый регистр. Данные последовательно передаются в сдвиговый регистр, затем фиксируются в регистре хранения. К регистру хранения подключены 8 выходных линий. На картинке ниже показано расположение выводов микросхемы 74HC595.

Р ис.3.

Микросхема 74HC595

ис.3.

Микросхема 74HC595

Вывод 14 (DS) это вывод данных. В некоторых описаниях он обозначается как «SER».

Когда уровень на выводе 11 (SH_CP, иногда обозначается как SRCLK) переходит из низкого в высокий, значение на выводе DS сохраняется в сдвиговом регистре, при этом данные сдвигаются на один разряд, чтобы предоставить место для нового бита.

Пока на выводе 12 (ST_CP, иногда обозначается как RCLK) низкий уровень, данные записываются в регистр сдвига. Когда уровень переходит в высокий, данные из сдвигового регистра фиксируются в регистре хранения, из которого поступают на выводы Q0…Q7.

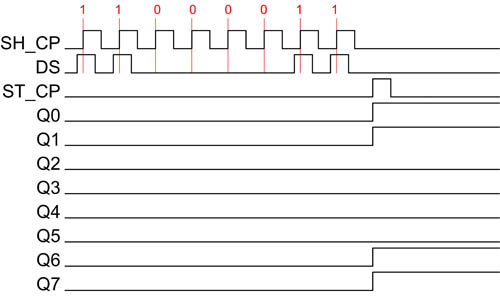

Н а

представленной ниже временная диаграмме,

показано, каким образом можно установить

на выходах Q0…Q7 микросхемы значение

11000011, учитывая что изначально там было

значение 00000000.

а

представленной ниже временная диаграмме,

показано, каким образом можно установить

на выходах Q0…Q7 микросхемы значение

11000011, учитывая что изначально там было

значение 00000000.

Рис.4. Вывод сигнала