- •Оглавление

- •Введение

- •Обзор литературы по твердотельным моп-структурам

- •Разновидности полупроводниковых моп-структур. Развитие моп технологии

- •1.2 Моделирование процессов

- •1.2.1 Одномерная программа suprem

- •1.2.2 Система sentaurus tcad

- •1.3 Комплементарные моп-схемы

- •1.3.1 Особенности проектирования кмоп-схем

- •1.3.2 Защелкивание в кмоп-структурах и его предотвращение

- •1.3.3 Методы межкомпонентной изоляции в кмоп технологических процессах

- •1.4 Анализ обзора литературы и постановка цели исследования

- •2 Методы формирования межкомпонентной locos изоляции субмикронного кмоп технологического процесса

- •2.1 Технология изготовления locos изоляции

- •2.2 Структура locos изоляции

- •2.2.1 Обычная заглубленная locos изоляция

- •2.2.1.1 Электроизоляционная способность

- •2.2.1.2 Структурная изоляция материала

- •2.2.1.3 «Птичий клюв»: влияние параметров процесса

- •2.2.2 Встраиваемая locos изоляция

- •2.2.3 Расширенная locos изоляция

- •2.2.3.1 Silo изоляция

- •2.2.3.2 Полибуферный locos (pbl)

- •2.2.3.4 Боковые спейсеры locos структуры

- •2.2.4 Изоляция, ограниченная нитридом (nppbl)

- •2.2.4.1 Структура nppbl изоляции

- •2.2.4.2 Геометрические и электрические характеристики nppbl изоляции

- •2.3 Выводы

- •3 Маршруты создания передовых видов locos изоляции

- •3.1 Ls_locos изоляция

- •3.1.1 Выводы

- •3. 2 Pelox изоляция

- •3.2.1 Выводы

- •4 Экономическая часть

- •4.1 Краткое описание объекта

- •4.2 Расчет заработной платы

- •4.3 Калькуляция полной себестоимости

- •4.4 Выводы

- •5 Охрана труда

- •5.1.1 Опасные производственные факторы при термодиффузионных операциях

- •5.1.2 Вредные химические вещества

- •5.1.3 Метеорологические условия

- •5.1.4 Вентиляция

- •5.1.5 Производственное освещение

- •5.1.7 Электробезопасность

- •5.1.8 Пожарная безопасность

- •5.2 Техника безопасности

- •5.3 Расчет искусственного освещения

- •Заключение

- •Список используемой литературы

- •Приложение а – задание на преддипломную практику приложение б графический материал

1.4 Анализ обзора литературы и постановка цели исследования

Хотя основу технологии МОП ИС составляет планарная технология, первоначально разработанная для производства ИС на биполярных транзисторах, с целью улучшения рабочих характеристик МОП-транзисторов в нее был внесен целый ряд важных усовершенствований.

Существуют КМОП-технологии с карманами как p- так и n-типа, каждая со своими достоинствами и недостатками. С помощью КМОП технологии можно строить цифровые инверторные схемы, которые практически не потребляют мощности в статическом режиме, так как единственная цепь для тока источника напряжения питания — это малые постоянные токи утечки переходов. Такая особенность КМОП-схем играет особенно важную роль в создаваемых в настоящее время полупроводниковых ЗУ большой информационной емкости. Специфическая проблема проектирования КМОП-схем состоит в том, чтобы избежать защелкивания, при котором регенеративное срабатывание биполярных элементов вызывает переход паразитных биполярных транзисторов (всегда существуют в большинстве КМОП-схем) в режим насыщения. Путем тщательного и аккуратного проектирования схем и, возможно, некоторого усложнения технологии производства ИС эффект защелкивания можно устранить. Технологические требования, предъявляемые при производстве КМОП-схем, задержали разработку и освоение КМОП-технологии по сравнению с n-канальной МОП технологией, однако благодаря последним достижениям технологии кремниевых ИС КМОП-технология стала высокоразвитой и перспективной технологией СБИС.

Анализ литературных источников показал, что технология КМОП ИС, которая вобрала в себя все преимущества и достижения технологии n-канальных МОП ИС, стала одной из наиболее важных технологических схем формирования СБИС.

Целью данного дипломного проекта является изучение методов межкомпонентной субмикронной изоляции, которые позволят улучшить характеристики ИС.

Для реализации поставленной цели решаются следующие задачи:

- анализ и исследование свойств различных межкомпонентных изоляций;

- анализ структур наиболее перспективных методов изоляции;

- анализ методов формирования межкомпонентной субмикронной изоляции;

- улучшение качеств межкомпонентной изоляции.

2 Методы формирования межкомпонентной locos изоляции субмикронного кмоп технологического процесса

Необходимость в минимизации расстояния между устройствами в интегральных схемах привело к развитию методов изоляции. Рассмотрим наиболее важные тенденции в развитии технологии изоляции, начиная с обычной – LOCOS структуры. Данная структура изоляции используется как передовая. Она позволяет снижать потери в активной области и предотвращать утечки через переход.

2.1 Технология изготовления locos изоляции

До изобретения планарной технологии, транзисторы и диоды, как правило, изготавливались как мезаструктуры. Поверхностные токи утечки были большой проблемой в данных устройствах. Открытие компании Atalla и соавторов показало, что термически выращиваемый оксид кремния на поверхности, может резко уменьшить ток утечки. Это привело к развитию первой структурной изоляции для интегральных схем, а именно процессу PLANOX. Прорыв в области технологии изоляции произошел в 1970 году, когда компания Appels поняли, что Si3N4, устойчив к окислению. Они применили эту концепцию и развили «локальное окисление кремния», или LOCOS –– процесс электрической изоляции устройств.

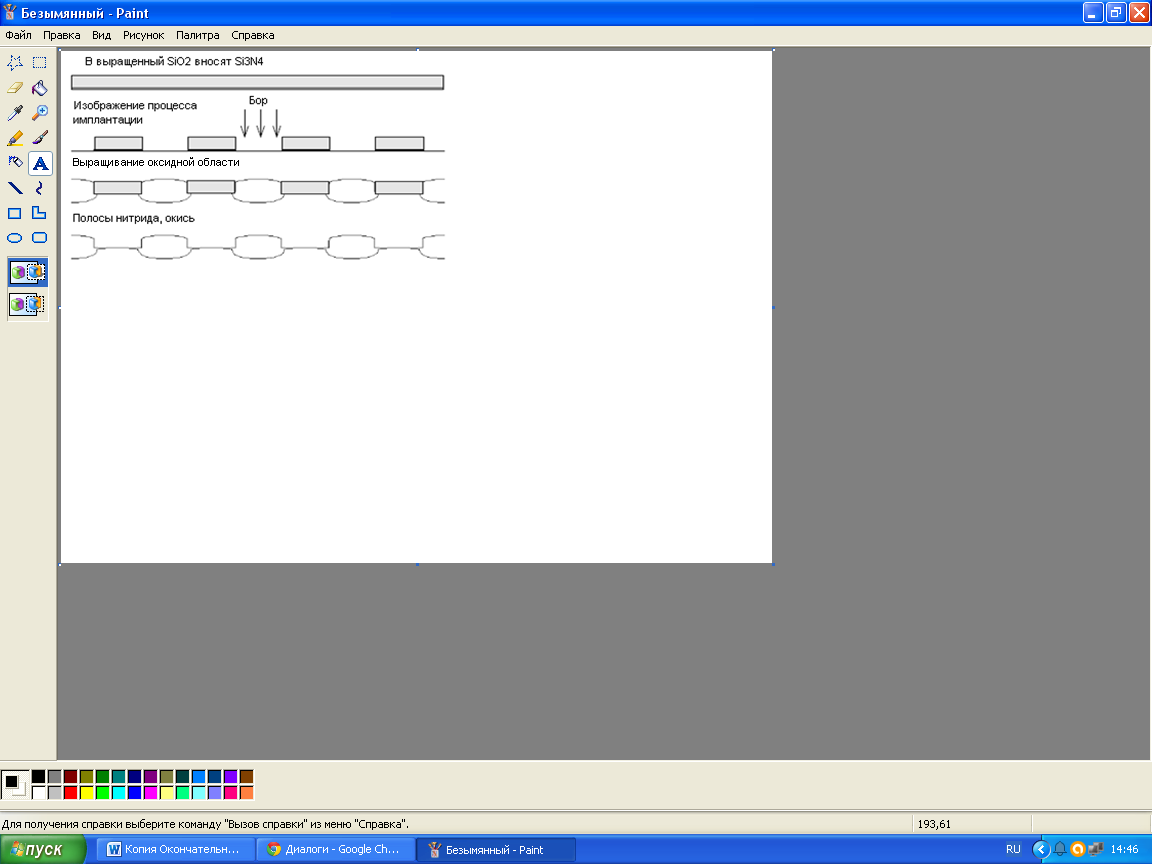

Обычная изоляция LOCOS представлена на рисунке 2.1

Рисунок 2.1 –– Последовательность процесса локального окисления кремния

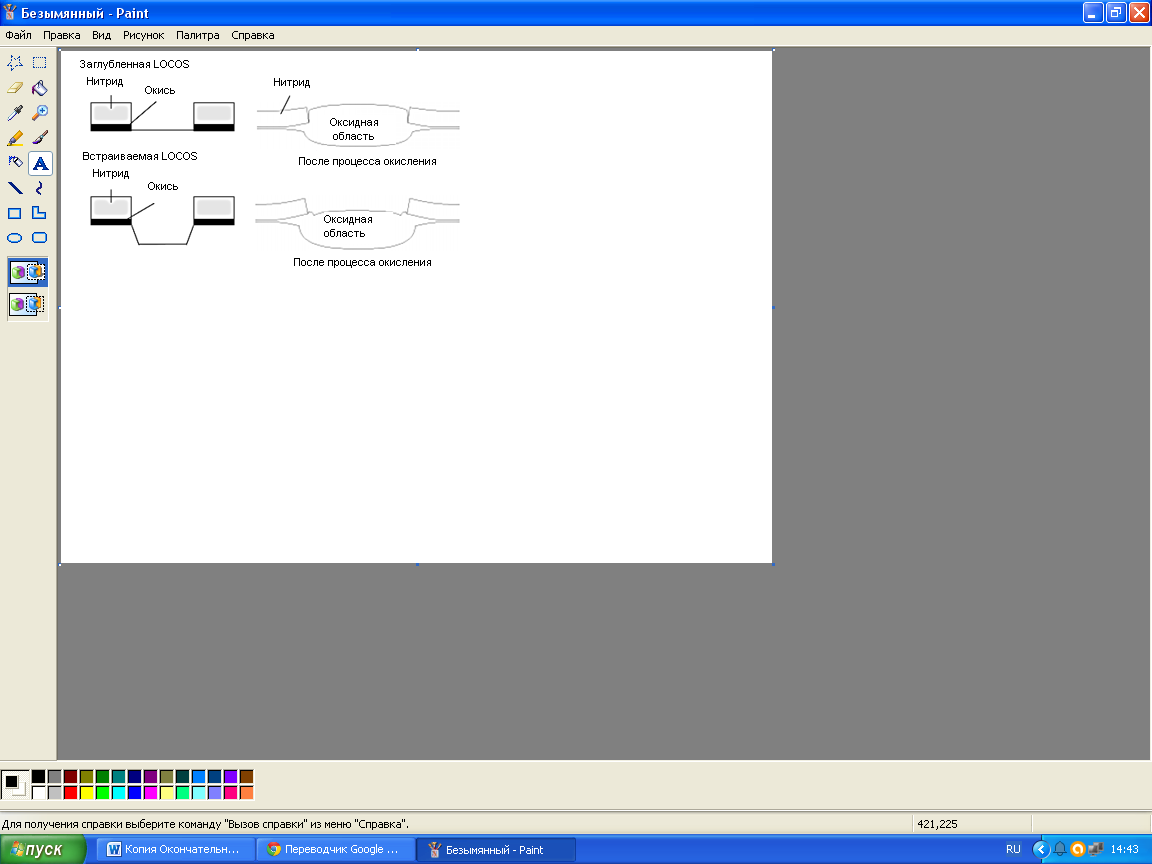

После роста тонкого оксида (10-20 нм), осаждается слой LPCVD Si3N4 (100-200 нм). Нитридная маска служит для формирования активных областей устройства. Поскольку Si3N4 устойчив к окислению, оксид будет расти только в тех направлениях, которые не имеют нитридных масок. Перед выращиванием оксидной области, происходит имплантация бора в p-область (1∙1013 - 1∙1014 см -2). ИЛ p-области происходит через локальный окисел на больших энергиях (0,5-0,35 мкм КМОП). Локальное окисление необходимо выполнять при температуре ниже температуры пластической текучести SiO2 (1025 ˚С). При окислении на температуре 1025 ˚С и выше «клюв» будет короче, но механические напряжения больше. Изоляция структуры завершается снятием плёнки Si3N4 горячей (150-175 ˚С) H3PO4, и оксидной подложки в растворе HF. Поскольку локальный окисел после снятия маски нитрида и поднитридного окисла значительно выше кремниевой подложки, этот процесс часто называют заглубленной LOCOS изоляцией. Когда мелкие канавки травятся в кремнии до области окисления, получаем встраиваемую LOCOS изоляцию. Разница между этими структурами показана на рисунке 2.2.

Рисунок 2.2 –– Иллюстрация разности в форме и рельефе заглубленной и встраиваемой LOCOS структурах

Во встраиваемой структуре, большая часть оксидной области значительно ниже кремниевой подложки, отсюда и название. Этот класс структурной изоляции будет более подробно обсуждаться в разделе 2.2.2.

Возможность локально окислять кремний является неотъемлемой частью любой структурной изоляции. Через несколько лет в литературе был предложен ряд альтернатив обычной LOCOS технологии. Большинство из них, однако, были отклонены и лишь ограниченное число используются в настоящее время. Проведены работы по модернизации способа изоляции методом локального окисления. Эти способы используются вплоть до 0,5 мкм, 0,35 мкм КМОП технологиях производства ИС, в том числе и ИС ДОЗУ (динамических оперативных запоминающих устройств). Общая тенденция в конструкции изоляции структуры состоит в том, чтобы внести изменения в состав активной зоны маски стека (области изоляции, иногда выполняется травление кремния, чтобы уменьшить боковой уход и заглубить локальный окисел). Изменение свойств растущей оксидной области необходимо для того, чтобы влиять на характеристики структуры изоляции, и уменьшить клюв, т.е. выход изоляции за маску фотолитографии, но до настоящего времени, единственный способ, которым это удалось сделать, было увеличение температуры окисления. Следует отметить, что, несмотря на это, LOCOS до сих пор активно используется, хотя и существует четкая тенденция перехода к более продвинутой изоляции, такой как канавочная изоляция. Изоляция является одним из технологических процессов, которые серьезно ограничивают плотность элементов в ULSI технологии (количество транзисторов на одной микросхеме). Поэтому фундаментальное понимание параметров, которые влияют на форму LOCOS изоляции, и ее взаимодействие со структурой прибора необходимо для того, чтобы быть в состоянии предсказать пределы масштабируемости этой технологии. В следующих пунктах представлены результаты экспериментального и теоретического исследования пределов масштабируемости LOCOS технологии [9].