- •8. Микроэлектронды құрылымдарды құрудың базалық физика – химиялық әдістері.

- •16. Гибридті интеграл микросхемалар конструкциясын түсіндіріңіз

- •18. Жұқа кабықтарды алу әдістерін түсіндіріңіз

- •19. Интеграл микросхемалар үшін төсенішке (подложка) сипаттама беріңіз

- •20. Жұқа қабықты резисторларды түсіндіріңіз

- •21. Жұқа қабықты конденсаторларды түсіндіріңіз

- •22. Жұқа қабықты интеграл микросхемалардағы индуктивті элементтерге сипаттама беріңіз

- •23. Гибридті интеграл микросхемалар үшін корпустарға сипаттама беріңіз

- •24. Интеграл микросхемаларды жобалауда бастапқы және схематикалық деректерді түсіндіріңіз

- •25. Интеграл микросхемаларды жобалауда технологиялық және конструкциялық деректерді түсіндіріңіз

- •26. Жобалау топологиясы және гибридті интеграл микросхемалар конструкциясын түсіндіріңіз

- •27. Үлкен интегралдық микросхемалар негізгі параметрлері және жалпы сипаттамасын түсіндіріңіз

- •28. Үлкен интегралдық микросхемаларды қолдану және классификациясын түсіндіріңіз

- •29. Үлкен интегралдық микросхемалардағы база элементтерін түсіндіріңіз

- •30. Шалаөткізгіштік үлкен интегралдық микросхемаларды алу технологиясы және конструкциясын түсіндіріңіз

- •31. Жеке кристаллдардағы үлкен интегралдық микросхемаларды түсіндіріңіз

- •32.Гибридті үлкен интегралдық микросхемаларды алу технологиясы және конструкциясын түсіндіріңіз

- •33 Жұқа қабықты гибридті үлкен интегралдық микросхемаларды алу технологиясын түсіндіріңіз

- •34. Қалың қабықты гибридті үлкен интегралдық микросхемаларды алу технологиясын түсіндіріңіз

- •35. Көп қабатты керамика негізіндегі гибридті үлкен интегралдық микросхемаларды алу технологиясын түсіндіріңіз

- •37. Үлкен интегралдық микросхемаларды жобалаудың негізгі этаптарын түсіндіріңіз

- •38. Үлкен интегралдық микросхемаларды жобалау ерекшеліктерін түсіндіріңіз

- •39 .Үлкен интегралдық микросхемаларды жобалаудың негізгі мәселелері және кедергілерін түсіндіріңіз

- •40 .Интегралдық микросхемалардың схематехникалық ерекшеліктерін түсіндіріңіз

- •41 .Биполярлы транзисторлы сандық интегралды микросхемалардың негізгі типтерін түсіндіріңіз

- •42 .Микроқуатты логикалық интегралдық микросхемаларға сипаттама беріңіз

- •43 .Сандық микросхемалар дамуына сипаттама беріңіз

- •44 .Шалаөткізгіштік сандық электрониканың элементтерін түсіндіріңіз

- •45 .Импуьсті сигнал және оның негізгі сипаттамаларын түсіндіріңіз

- •1. Сурет. Кернеуді резистивті бөлгіштің (а), rс буындарын (звеньев) дифференциялдаушы (б) және интегралдаушы (в) схемалары

- •2. Сурет. Шығысында тізбектерді әр түрлі уақытпен τ : дифференциялдаушы (а) және интегралдаушы (б) ұзақтықпен идеалды тікбұрышты импульстің графиктері.

- •1. Сурет. Уго Шеффердің (а) және Пирстің (б) элементтері.

- •2 Сурет. Шеффердің элементтерінде және (а), немесе (б) және емес (в) функцияларын жүзеге асыру.

- •3. Сурет. Пирстің элементтерінде және (а), немесе (б), емес (в) логикалық функцичяларын жүзеге асыру.

- •4.Сурет. Және элементін кілт ретінде қолдану: а – схема; б – уақытша диаграммалар.

- •48.Интегралды схемалардың базалық логикалық элементтерін түсіндіріңіз

- •1 Сурет. Ттл сериясының базалық логикалық элементі: а – принципиальді схема; б – кіріс каскадының эквивалентті схемасы

- •50. Мультиплексор және демультиплексорға сипаттама беріңіз

- •51. Шифраторлар және дешифраторларға сипаттама беріңіз

- •53.Санды-аналогтық түрлендіргіштерді түсіндіріңіз

- •54.Аналогты-сандық түрлендіргіштерді түсіндіріңіз

- •55.Электрондық есте сақтау құрылғыларын түсіндіріңіз

- •56.Аналогтық интеграл микросхемалардың негізгі типтерін түсіндіріңіз

- •57.Микропроцессор. Микропроцессорлы жүйе туралы түсіндіріңіз

- •58.Өте жоғары жиілікті диапазонда интегралдық микросхемаларға сипаттама беріңіз

- •60.Интегралдық микросхемалар және үлкен интегралдық микросхемаларды қолдану негіздерін түсіндіріңіз

53.Санды-аналогтық түрлендіргіштерді түсіндіріңіз

САТ – тің схемалық жүзеге асуының кейбір нұсқаларын қарастырайық.Мысал үшін п = 4 разрядтылықпен шектелеміз. 1, а – суретте көрсетілген инверттеуші суммалаушы операциялық күшейткішті қарастырамыз.

Оның артықшылығы мынада, Хі кірістері бір біріне әсер етпейді. ОК кірісінде кедергісі 2п еселі өлшеуші резисторлар қосылған. Соған орай, күшейту коэффициенті әр кірістен әртүрлі болып алынады және белгілі екілік разрядтың «салмағына» сай келеді. Егер Хі кірістеріне екілік код берсек, онда ОК шығысындағы кернеу бұл кодтың мөлшеріне пропорционал болады. Инверттеуші ОК – тің күшейту коэффициенті мына формуламен есептеледі

![]()

Мұндағы, Rо.с. – кері байланыс резисторының кедергісі; Rі – кірістегі сигнал көзіне жүйелі қосылған резистор кедергісі.

1 – сурет. ОК – те сумматор қолданылатын САТ схемалары (а) және ИОН мен транзисторлы кілттерді қолданатын ОК негізіндегі САТ (б)

Суперпозиция принципін кіріс сигналдарға қолдана отырып алатынымыз

![]()

U1 – логикалық «1» деңгейі.

1, б – суретте келтірілген схема талаптарды логикалық сигналдар деңгейінің минимумына дейін түсіруге мүмкіндік береді. Ол өз алдына тірек кернеуінің көзі (ТКК) мен униполярлы транзисторда кілт қолданатын операциялық күшейткіш негізіндегі САТ- ті білдіреді. Х0...Х3 кірісіне түмуші сигналдар бұл схемада сәйкес келетін резисторлар қосу үшін қызмет етеді. Схеманың шығыс кернеулері мына формула бойынша анықталады

![]()

Uо.п. – тірек кернеу.

Схеманың артықшылығы – барлық разрядтар үшін «1» бірдей деңгей, кемшілігі – резисторларға және ТКК шығыс кедергісіне қатал талаптар. Өлшеуші резиторы бар жүйенің ең маңызды кемшілігі – ол жоғарыдәлдікті кедергі матрицасында қолданылатын кең диапазон.

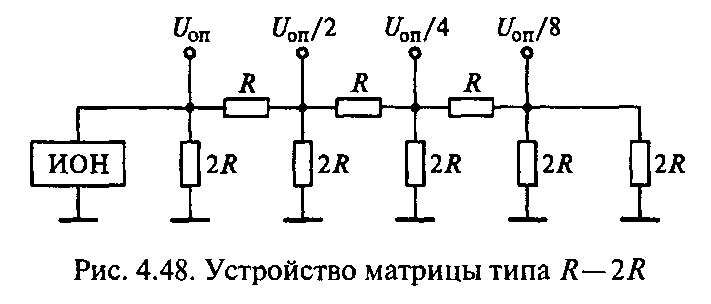

2 – суретте көрсетілген, бірдей Г – бейнелі түйіндерден құралған схеманы қарастырамыз. 2 – суретте осындай түйіндердің бірі түспен ерекшеленген, ал тізбектің кірісінде және шығысында симметриялаушы резисторлар кірістірілген. Ом заңын қолдана отырып әрбір келесі түйіннің шығысында кірісіне қарағанда кернеу деңгейі екі есе аз болатындығын көз жеткізу оңай.

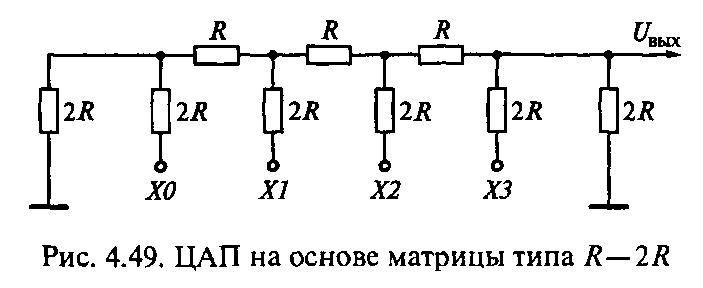

R – 2R тізбегі қарапайым САТ ретінде қолданылған болуы мүмкін. 3 – суретті қарайық. Егер Х0...Х3 кірісіне кіріс сигналға сәйкес келетін екілік код беретін болсақ, Кирхгоф заңын қолдана отырып, схеманың шығысындағы кернеу Uвых бұл кодтың мөлшеріне пропорционал болатынын көрсетуге болады.

Шығыс сигнал тудырудағы үлкен разрядқа сәйкес келетін Х3 кірісіндегі кернеу үлесі Х2 кірісіндегі үлеске қарағанда едәуір анық. Схеманың кемшілігі - Х0...Х3 кірісінде «0» және «1» логкалық деңгейлерге деген жоғары талаптар. Бұл кемшіліктерді жою үшін алда келтірілген схеманы қолдануға болады.

2 – сурет. R – 2R типті матрица құрылғысы

3 – сурет. R – 2R типті матрица негізіндегі САТ

Кілт ретінде МДШ – транзисторларын қолдануға болады

Өзінің тура мағынасына орай САТ – ті ерікті периодты функцияны синтезтеуші генератор ретінде қолдануға болады. Қарапайым нұсқада синтездеуші генератор мыналардан тұрады: счетчик, G тактілік импульстің генераторы, дешифратор, кірісте резистивті матрицасы бар ОК.