- •Verilog & system verilog

- •I бөлім. Жобалау

- •Сандық жүйелердің жүзеге асырылулар

- •Сандық жүйелерді жасауға арналған аппараттық құралдар

- •Сандық жүйелердің технологиялық шешімдері (конструктивы)

- •Сандық жүйелерді тестілеу және жасау технологиясы

- •1.5. Аппараттың сипатталу тілдері

- •1.5 1. SoC жобалауы мен верификациясының тілдері.

- •1.5.2. Tlm әдістемесінің негізі.

- •1.6. SoC жүзеге асыру технологиялары бойынша қорытындылар

- •1.7. SoC компоненттерінің hdl-модельдерін верификациялау және тестілеу

- •1.8. Бағдарламалық-аппараттық өнімдердің тестқа жарамдылығы

- •1.13 Сурет. Бағдарламалық-аппараттық комплекстың өмірлік циклының графигі

- •1.14 Сурет. Валидация және верификация процесстерінің әрекеттестігі

- •1.16 Сурет. Жобаны верификациялау ортасы

- •1.17 Сурет. Жобаның верификациясы үшін ассерцияларды қолдану технологиясы

- •1.18 Сурет. Жобаның верификация маршруты

- •1.10. Верификация инфрақұрылымының аналитикалық моделі

1.5.2. Tlm әдістемесінің негізі.

TLM (Transaction Level Modeling) тұжырымдамасының негізіне жүйенің компоненттерін жобалаудың жеткілікті шешімін, талдау дәрежесінің модельін жасау жатады. Жеке бөлшектердің анализі ғана модельді анықтаудың жылдамдығын айтарлықтар арттыра алады. TLM тұжырымы қандай да бір тілге тәуелді болмайды, алайда, жоғарға дәрежелі бағдарламалық тілдерге сүйенеді. Мысалы: SystemC немесе System Verilog. Transaction Level Modeling bit-true, address-map accurate, cycle-less модельін ұсынады. TLM транзакцияны (SoC – оқиға) мағлұматты жылдам таратушы немесе hardware/software спецификациялық жүйемен анықталатын, екі модуль арасында синхрондаушы оқиға ретінде анықтайды. TLM термині ESL(Electronic System Level) жобалануының дәрежесімен сәйкес анықталған [17-21]. Жоғарғы тұжырымдамалық дәрежедесіндегі аппараттық модельдеуде бағдарламалық тілдің жоғары дәрежесі қолданылады. Ондай тілдерге SystemC, SpecC, Hpascal, System Verilog, Hard wareC жатқызуға болады. Абстрактілі модельдер. TLM тұжырымдамасының негізі- жүйелер мен ішкі жүйелер арасындағы байланысы мен олардың функционалдығы бір-бірінен тәуелсіз дайындалып, құрылымы талдап тексеріліп отырады.

Талдап тексерудің такты бойынша функцияналдығы мен байланысын сипаттауды қолдайтын модельдері мәліметтерді тарату деңгейінің (RTL-register-transfer level) құрылымына жатады. Кері жағдайды қолдайтын модельдерді SAM (System Architectual Model) деп атайды. SAM - модельдерді алгоритмдерді, бағдарламалық қамсыздандыруды және аппаратты жобалаушы мамандар топтарының арасында байланыс амалы болып табылады. 1.11 суретте көрсетіліп, TLM түрінде белгіленген, 4 құрылымға уақыт бойынша аппроксимацияланған модельдер тән (approximatly - timed). Онда статикалық және есептелу уақыты немесе ішкі жүйелердің уақытқа байланысты талаптарын қолданылады.

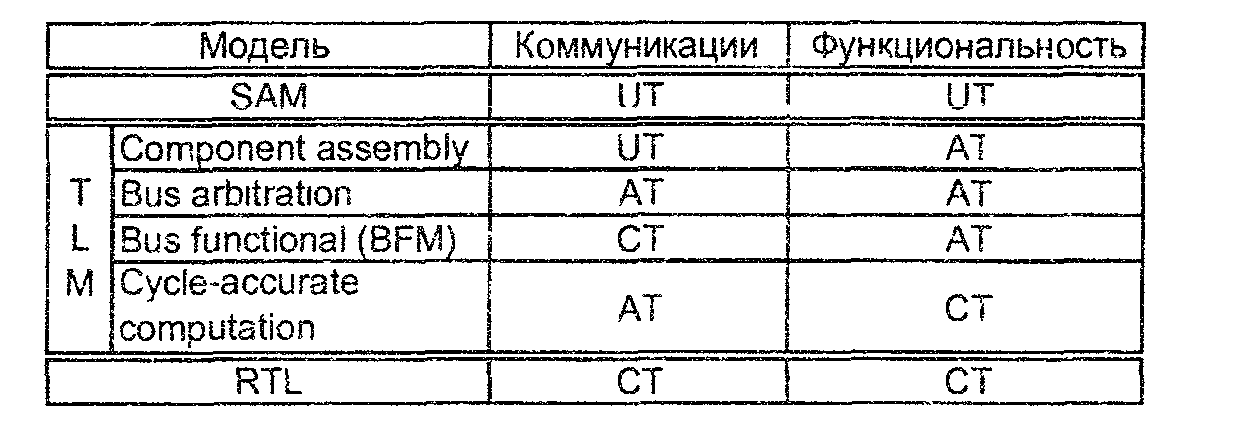

1.4 кестеде SoC жобалауында қолданылатын абстракция модельдерінің тізімі көрсетілген. BFM (Bus Functional Model ) - модельі TLM- модельдерінің арасындағы ең таралған түрі. Қалған үшеуінде жалпыға ортақ атауы жоқ. Оларды Gajski және Cal басылымдарында ғана атаумен қолданған. Практикада бұл модельдердің барлығын қолдану міндетті емес, олардың арасынан екеуі немесе үшеуі таңдалып, қолданылса жеткілікті. Жобалаудың бастапқы кезеңінде шиналар арқылы мәліметтердің таралу үрдісінің дәл сипаттамасы қажет емес, сондықтан бұл қадамның бір оқиға түрінде орындалуын көрсететін модель немесе транзакция қолданылады (component -assembly model).

1.11 -сурет. Сандық құрылғылардың абстракциялы модельдері

1.4 - кесте. Сандық құрылғылардың модельдері

Жобалаудың келесі кезеңінде блоктардың ішіндегі әр сигнал үшін ақпаратты тарату кезінде, такттардың нақты санын білудің маңызы арта түседі. Дегенмен, шинадағы ақпаратты тарату үрдісі бір транзакция немесе оқиға түрінде қарастырылады (bus- arbitration немесе cycle-accurate модельдері). Спецификация толық анықталғаннан кейін, шиналар сигналды өзгерту үшін, транзакцияның немесе оқиғалардың көмегімен модельденеді (bus functional or RTL model).

1.4-кестеде component assembly модельі бір оқиғаны қолданады (1 cvent), оған bus- arbitration модельінің 5 оқиғасы (5 cvent), ал RTL - модельдерінің шамамен 75 оқиғасы (75 cvent) сәйкес келеді. Тракттардың нақты саны модельдеу алгоритімдеріне тәуелді.

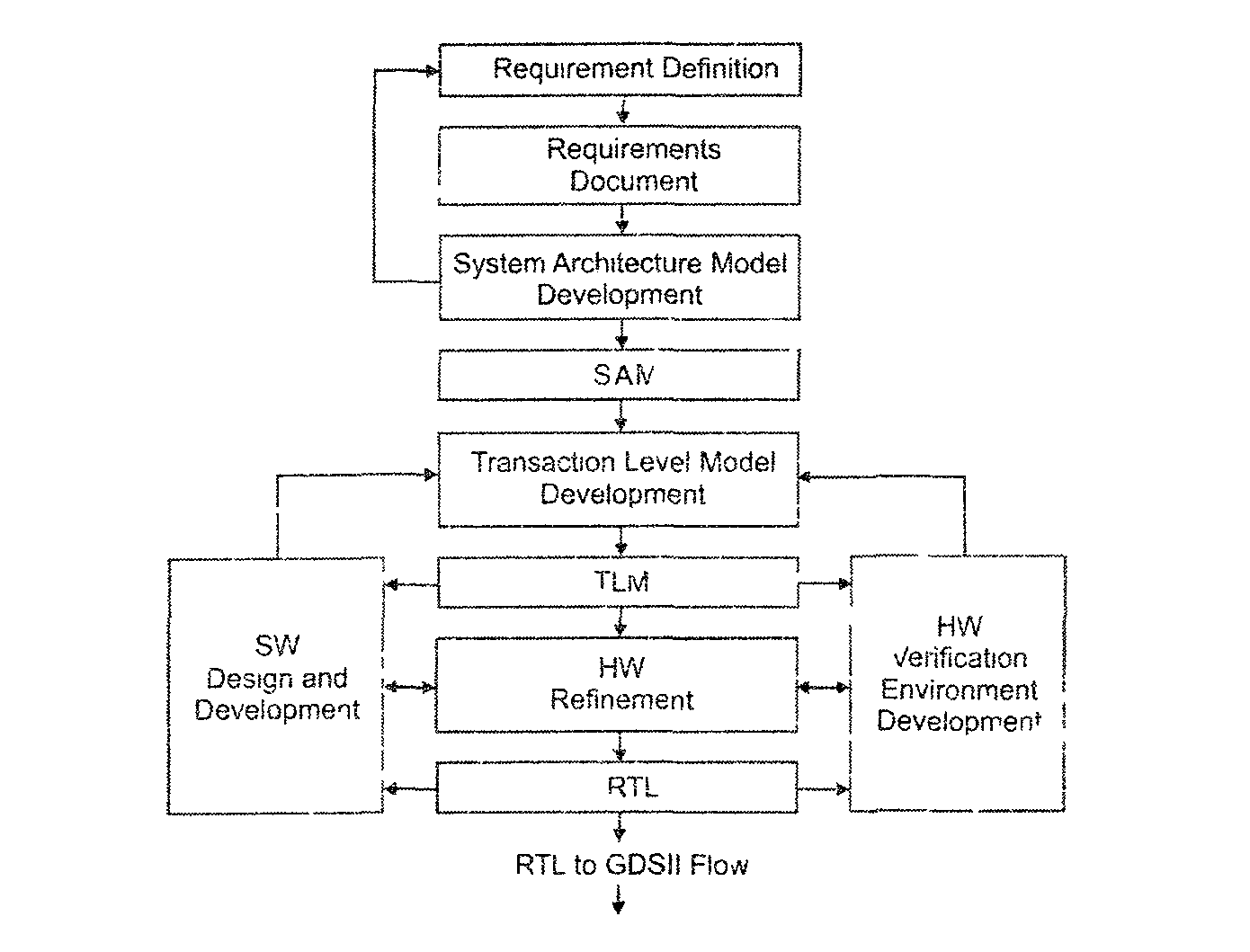

TLM-мен жобаланудың әдіснамасы. Жобалаудың жаңа технологиясы екі бөліктен құралған: стандартты - RTL-дан бастап, микросұлбаның дайындалуына дейін (layout flow) және қосымша- жүйелік деңгейден RTL-ға дейін. Жобалау қағаздағы құжат түрінде көрсетілетін, жүйелік спецификацияны жасаудан басталады. Осы спецификацияларға негізделіп, жүйелік жобалаушы құрылғының архитектурасын software/hardware құраушыларына бөледі. Келесі кезең TLM болып табылады. TLM software/hardware параллельді құрылымдарын фазамен қамту қызыметін атқарады. Бұл жағдайда TLM software және architecture үшін жобалау командасының бастапқы әмбебеп түрінде болады. Олар сонымен қатар, верификация мен тесттер аймағын жүзеге асыруда да тестілеу командаларымен қолданылап, осылайша, олардың RTL -платформасын әзірлеуге дайындығын қамтамасыз етеді. Осы арлық кезеңде, RTL -платформасының негізінде пайда болған, hardware өндірушілері жүйеге арналған RTL-жобасын ұсынады. Осылайша, software/hardware біріккен жобасы орындалады, бұл жаңа әдіснаманың классикалықпен салыстырғанда негізігі артықшылықтырының бірі болып табылады. Сондықтан, жобалаушыға RTL -платформасы да рұқсатталып, сол арқылы күтілетін параметрлерімен жобаны модельдеудің сәйкестігін тексеру, hardware -мен бірге төмен деңгейлі software интеграциясындағы hardware верификациясы тәрізді мәселелердің шешімін табады. Бұл тапсырмалар эмуляция қадамына синтез жасау мен имплементация нәтижелерінің талдануымен параллельді шешіледі.

Үштік абстракция. Жобалаудың жаңа әдіснамасы үштік абстракциялық құрылымын анықтайды: SoC функционалды түрі; архитектуралық SoC; микрархитектуралық түрдегі SoC 1) Функционалды SoC ( SoC Funetional View). Абстракцияның ең жоғары деңгейі, қолданушының көзқарасына негізделген жүйенің күйін зерттейді. Функционалды түрі ешқандай жүзеге асырушы құрылымсыз орындалады (архитектуралар немесе адрес аймағы). Жүйенің өндіруші параметрлері қағаздағы спецификация түрінде сипатталады. 2) Архитектуралық түрде (SoC Architecture View). TLM -үлгіде орындалған, жобалаудың төменгі деңгейі болып табылады. Одан басқа, архитектуралық түрі верификациялаушы инженерлерде анықтаушы модель ретінде қолданысқа ие. Бұл жағдайда функционалдық тесттерді генерациялау үшін алтын эталоны есебінде табылып, жобалаудың келесі кезеңдерінде құрылғыларды верификациялауда да қолданылады. 3) Микрархитектуралық түрдегі SoC- үштік абстракцияның ең төменгі деңгейі. Синхротакт бойынша уақыттық модельдеу туралы толық ақпарат береді (cycle-accurate). Бұл деңгейдің жалпылыма практикасында аппаратураны сипаттаушы тілдерінің көмегімен жасалған RTL- модельдерінің қолданылуы саналады (VHDL[13-15] немесе Venlog [15,16] [19] [20] тілдері).

Жалпы жағдайда жобалаудың заманауи үрдісіне 1.12 суретте көрсетілгендей сұлба түрінде құрастырылуы мүмкін. Жобалау тапсырыс берушімен немесе маркетингті топтармен құрылған Product Requirement Document (PRD) -дан басталады. PRD негізінде SAM жүзеге асады, бұл кезеңде PRD -ға қажетті өзгертулер мен белгілеулер енгізіледі. Кейін SAM TLM- модельдерінің біріне түрленеді, мысалы, бастапқыда component assembly модельі болып, кейін bus arbitration модельіне айналады. SAM үшін сәйкес тілді таңдағанда бұл үлгі қайта қолданылып (reuse), тестілу жолымен TLM-ға түрлену мүмкіндігіне ие болуы керек.

1.12 - сурет. SoC- жобалауының заманауи кезеңдері

TLM-моделдері арқылы мына мәселелердің шешімдері табылады: 1) HW/SW partitioning сияқты имплементацлардың құрамын анықтау; ASIC-пен HW partitioning аралығы, FPGA және board жүзеге асыру; шинаның архитектурасын жүзеге асыру; қосымша проссесорды таңдау және сипаттау; 2) Жүйелік программалық қамсыздандыру үшін платформаны дайындау. 3) Аппаратты функционалды верификациясы үшін алтын модельін жасау. 4) Бөлшектік спецификация hardware жасау үшін микроархитектуралық аппаратты және негізді ойлап табу.