- •Verilog & system verilog

- •I бөлім. Жобалау

- •Сандық жүйелердің жүзеге асырылулар

- •Сандық жүйелерді жасауға арналған аппараттық құралдар

- •Сандық жүйелердің технологиялық шешімдері (конструктивы)

- •Сандық жүйелерді тестілеу және жасау технологиясы

- •1.5. Аппараттың сипатталу тілдері

- •1.5 1. SoC жобалауы мен верификациясының тілдері.

- •1.5.2. Tlm әдістемесінің негізі.

- •1.6. SoC жүзеге асыру технологиялары бойынша қорытындылар

- •1.7. SoC компоненттерінің hdl-модельдерін верификациялау және тестілеу

- •1.8. Бағдарламалық-аппараттық өнімдердің тестқа жарамдылығы

- •1.13 Сурет. Бағдарламалық-аппараттық комплекстың өмірлік циклының графигі

- •1.14 Сурет. Валидация және верификация процесстерінің әрекеттестігі

- •1.16 Сурет. Жобаны верификациялау ортасы

- •1.17 Сурет. Жобаның верификациясы үшін ассерцияларды қолдану технологиясы

- •1.18 Сурет. Жобаның верификация маршруты

- •1.10. Верификация инфрақұрылымының аналитикалық моделі

Сандық жүйелердің технологиялық шешімдері (конструктивы)

Сандық жүйелерді жасауға қолданылатын, олардың күрделілігінің өсуіне байланысты электрондық технологиялар нарығына арналған негізгі қазіргі шешімдер келтірілген. Функционалды блоктардың сервистік диагностикалық қызмет ету бөлігінде шешілетін мәселелер көрсетілген.

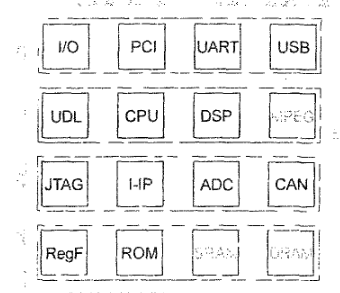

Кристалдағы жүйе – System on Chip (SoC) – силиконды кристалда

конструктивті жасалған (1.2-сурет), энергияны аз тұтынумен, өлшемдері кішкентай, жоғары тез әрекет етушілікпен сипатталатын мамандандырылған сандық бұйым және келесі компоненттерді құрайды: (CPU) процессорі, (RegM, ROM, SRAM, DRAM) есте сақтау жадысы, (UDL) логика, (I/O, PCI, UART, USB, CAN) енгізу-шығару интерфейстері, (ADC, DSP, MPEG) мәліметті түрлендіргіштер, мәліметтердің алмасу шинасы және IEEE 1500 стандарты және JTAG технологиясы негізінде сервистік қызмет ету инфраструктурасы (I-IP).

SoC функционалдық блоктары кез келген мәселелердің универсалды есептеуіші болатын микроконтроллерге қарағанда өзекті мәселелерді эффективті түрде шешуге бағытталған. SoC артықшылықтары: кірістірілген деструктивті компоненттер туралы мөлдірлік (прозрачность); энергияны аз тұтынуда жоғары өнімділік; өте кішкентай өлшемдер; есте сақтау жадысының әртүрлі типін эффективті қолдану, жоғары сенімділік; дайын бұйымның төмен бағасы және функционалдылықтарды қолданудың жоғарғы коэффициенті. Суреттелген артықшылықтар үшін ақысы: жобаны тестілеу және верификациялаудың маңызды уақыты (жоба периодынан 70%); жасаудың және пішімдеудің жоғары құны; ретке келтірудің және өндірістің күрделілігі; әртүрлі көздерден IP-cores (интеллектуалды меншік) интеграциясы.

1.2-сурет. SoC-тың қазіргі құрылымы

IP-Core – күрделі, тестілеуден өткен, аса күрделі сандық бұйымдардың (изделие) жобалануының жасау уақытын қысқарту мақсатында компонент ретінде көп ретті қолданылатын верификацияланған және тиімді функционалды модуль [3]. IP-Core қолдану бізге: 1) нарықта сандық бұйым пайда болған моментке дейін уақыттың маңызды қысқартылуын; 2) IP-Core-мен байланыс жүйесі үшін интерфейстің жасалу жолымен жобалау процесін жеңілдетуді; 3) тестілеуден өткен модульдердің арқасында жобалау тәуекелділігін минимизациялауды; 4) барлық жүйенің верификация уақытының азайтылуын береді.

SoC-тың қолданылу облыстары: конфигурацияланған мамандандырылған ашық кері бағдарламаланған бұйымдар, есептеуіш процессорлардың құпиясын сақтауға бағытталған жеке мамандандырылған өте кішкентай серверлер және аппаратты кілтпен қорғалатын мәліметтердің сақталуы, интеллектуалды RAM; ұялы телефондар үшін архитектуралар; мультимедиалық, сымсыз және телекоммуникациондық функционалдылықтар, нейронды, аналогтық және кванттық есептеуіштер. Нарықтың ерекше қызығушылығы мәліметтерді құпиялы түрде сақтауға ғана емес, сонымен қатар есептеуіш процесстерді рұқсат етілмеген доступтан қорғауға бағытталған кристалдағы жеке серверлердің пайда болуында көрсетіледі. Персоналды компьютердің USB портына Flash Memory өлшемінен кішкене асатын серверді қосып, қолданушы өзінің профессионалды қызметіне тән есептеулерді орындап, кейін серверде сақтайды. Сөйтіп, кристалдағы микросерверді профессионалдық міндеттерді қолданушымен жасауға бағытталған, кеңейтілген функциялары бар Flash Memory қорғалған карта ретінде қарастыруға болады. Мұндай концепцияның өзектілігі сондай-ақ универсалды персоналды компьютердің қолданылуының төмен коэффициентімен (5-10%-ға тең) расталады.

Бар мәселелер: 1) Жарамды өнімнің шығуын үлкейту жолымен SoC кристалдарының жасалу бағасының төмендеуі. 2) нарықтағы дайын бұйымның пайда болу периодының қысқартылуы (time-to-market) және дайын бұйымның өмірлік циклінің қысқарылуы. Егер әрбір 18 айда технологиялар өзгертіліп отырылса, онда бұйымның эффективті қызметінің мерзімін (3-4жыл) 2 жылға дейін жақындатып қысқарту қажет. Бұл жағдайда компаниялар әлем нарығында өзінің өніміне деген қызығушылықты танытатын аз шамада жоғарытехнологиялы өнімдерді пайдаланатын болады. 3) Уақытша осьта (15 айда) жарамды өнімнің эффективті шығарылуына жету үшін дәстүрлі шешімдерді қарастыра, келесі қорытындыны шығаруға болады: 15 айдан көп жасалатын өнім (time-to-market) нарыққа ешқашан түспейді. Бұл периодтың қысқарылуы (абсцисса осі бойынша сызықтың солға жылжуы) жоба қателіктерінің азаю санына тең (ордината осі бойынша сызықтың жоғарыға көтерілуі), жоғары нарықтық қызығушылыққа кепілдік бергендіктен, компанияға қосымша кіріс әкеледі. Бұйымның сенімділігі мен сапасына қарауды Design for Manufacturability кезеңіне жататын, процесстерге тиімді етілген, жаңа және эффективті әдістер мен тестілеу және верификациялау құралдарын жасау жолымен жобалаудың жүйелік кезеңінен бастау керек. Yield Learning Curve сандық бұйымдардың өндірісін ұлғайтуға арналған резервтерді көрсетеді (production ramp up). Мұнда негізгі болып кристалда ақаулар бар кезінде де жарамды өнімнің шығарылуын біршама ұлғайтатын, кірістірілген тестілеуге, диагностика жасауға және ремонтқа арналған жобаға стандарттар имплементациясының тестке жарамдылығы көрсетіледі [4].

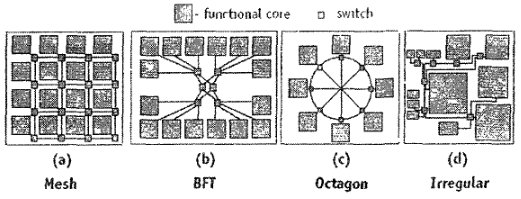

Кристалдағы желі – Network on Chip (NoC) – мамандандырылған

мультиядерлі кристалдағы жүйелердің барлық қасиеттерін иеленген, коммуникацияның интеллектуалды құрылымымен толықтырылған, кеңсе желісінің параллельді алмасуының протокол деңгейлерін және барлық арзитектурасын қолдайтын конвейерлі типті сандық бұйым.

Ядро ретінде масштабталған сегменттерге ұйымдастырылатын IP-core (процессор немесе жад блогы) алынады. Мұндай иерархия ретінде сәйкес коммуникацияның және конвейеризацияның екі деңгейлі жүйесі болады. Мәліметтер алмасу протоколының барлық деңгейлерінің қолдауы жоғары тез әрекет етушілік пен мәліметті каналдардың өткізу қабілетін қамтамасыз етеді. Интеллектуалды мультиядорлы архитектураның және коммутаторлардың бар болуы есептеуіш процессорларының және мәліметтерді қабылдау/тарату қиғашталуының жоғары деңгейін қамтамасыз етеді. Ең жақсы таралған архитектуралар 1.3-суретте келтірілген: а – бірдей ядро санына тең коммутатор санымен байланысқан процессорлардың желісі немесе матрицасы; b – желінің екі деңгейлі иерархиясының блокты-функционалды саралануы (сегментация); с – процессорлық жұптар арасында мәліметтердің эффективті алмасуына бағытталған көпбұрышты жұлдыз; d – әртүрлі приоритеттері мен функционалдылығы бар процессорларға қызмет етуге бағытталған екі деңгейлі иерархияның жүйелі емес құрылымы.

1.3-сурет. NoC-тың типтік құрылымдары

Кристалдағы типтік жүйеде 15-20 (IP-cores) функционалдылықтар бар. Бұл оның күрделілігінің және практикалық қолданудағы шегі болып табылады. Кейін желінің эффективті түрде қолданылуы жүреді. NoC кристалында SoC–қа қарағанда көпдеңгейлі архитектурасы бар.

NoC стандартында глобалды (локалды) желі сияқты мәліметтерді алмастыру протоколының жеті деңгейі бар. NoC құрылымы есептеуіш процестер мен мәліметтерді алмастыру позициясынан ғана емес, сонымен қатар жалпы сандық жүйенің сенімділігі мен энергияны сақтау жағынан эффективті. Транзакциялар, транспорттық және физикалық үш деңгейлер IP-ді шина арқылы таратылатын мәліметтерден бөлу үшін қолданылады. Біріншісі пакеттелген сигналдарды таратуға арналған. Екіншісі коммутатор жүйесі арқылы өтетін пакеттің маршрутын ұйымдастырады. Үшіншісі сымдар бойынша екілік мәліметтердің алмасуына бағытталған. Артықшылық жүйелерінің бар болуы, кристалдағы желінің қателіктерін түзету, интеллектуалды меншіктің (IP-core) жоғары қорғалуы, үлкен өлшемді масштабталған жүйелердің жобасын жасауға арналған бағыт, мәліметтер алмасу эффективтілігі, энергияны тұтыну төменділігі, операцияларды орындаудың жоғары жылдамдығы, кеңселік желіге тән жобалаудың көп емес бағасы және басқа сервистер технологиясын әлемдік нарыққа өте қызықты қылады, мұнда жақын арада 5 жыл ішінде желілік кристалдардың сату деңгейі 1 млрд. Долларға жетеді.

Кристалдағы жүйе есептеуіштердің (IP-cores) көп санымен және бір чиптегі жад блоктарының мүмкін болатын интеграция жолымен жобалаушыларға қызықты парадигма болып келеді. SoC технологиясының NoC құрылымына адаптациялану жолы және желінің кристалға өтуінің практикалық имплементациясы жасаушыларға жобалау әдістемесіне, тестілеуге, сонымен қатар CAD құрылғыларын жасауға қатысты маңызды, көп және әлі шешілмеген мәселелерді көрсетеді [5]. Функционалдылықтардың интеграция деңгейінің көтерілуінің нәтижесінде коммуникацияның инфрақұрылымын жасау жолымен модуль аралық байланыстардың эффективтілігін арттыру мәселесі пайда болды. Қазіргі уақытта TV–тюнерлерде, сымсыз базалық станцияларда, жоғары шешілімді сандық теледидарда, ұялы телефондарда, суреттерді жөндеу құрылғыларында (set-top boxes, wireless base stations, HDTV, mobile handsets and image processing) қолданылатын мультипроцесерлерді құрайтын SoC жобалар бар. Келтірілген құрылғылар жасаушылардан кристалдағы мультиядорлы жүйелерде параллельді есептеулерді ұйымдастыруға арналған тұрақты және тез әрекет етуші коммуникационды архитектураның жобалау облысында эффективті шешімдерді қажет етеді.

Коммуникацияның әртүрлі архитектуралары кристалдағы желілік шешімдердің типтік спецификалық шаблондарын қалыптастырады. Ең қызықтылары 1.3-суретте көрсетілген. SoC күрделі кристалы зерттеушілер желілік модульдер мен параллельді есептеулердің мүмкіндік беретін көптеген функционалды блоктардың микрожелісі ретінде қарастырылуы мүмкін екенін байқау керек. Коммутаторлары, маршрутизаторлары, байланыстары мен интерфейстері бар NoC «жаңа» компоненттер кітапханасы жасаушыға процессорлік модуль және жад блоктары (processor/storage cores) негізіндегі NoC архитектурасын жобалауда қосымша икемділікті (гибкость) қамтамасыз етеді. Әрине, бұған мәліметтерді алмасуының барлық деңгейлері, физикалықтан гранзакциондыға дейін қолдайтын синтез маршрутының да және сандық желілік жүйелер анализінің де сәйкес келетін және жеткілікті тексерілген құралдары бар болуы керек.

Жобаның маңызды сипаттамалары болып байланыс аралық архитектурасының энергетикалық шығындары, олардың өткізу қабілеті, кідіріс уақыты, сонымен қатар олардың жүзеге асырылуы үшін арналған аппараттық артықтығы табылады. NoC барлық негізгі қасиеттері абстракцияның жоғары деңгейімен коммуникациялық байланыстарды туғызатын интеллектуалды коммутаторлар негізіндегі процессорлық компоненттер мен жад модулі арасында туатын жоғарыөнімділікті байланыс аралығының мәселесін эффективті түрде шешуге бағытталған. Дегенмен желі компоненттер арасындағы мәліметтер алмасу мәселесі жүйенің өлшемінің өсуіне және байланыс арасындағы жалпы кідіріс есебінен аса күрделі болып келеді. Мүмкін болатын шешімдердің бірі байланыс аралық жүйесін әрбір коммуникационды модуль барлық жүйенің жұмыс істеуінің уақытша параметрлерін қанағаттандыратын мультимодульді конвейерлі платформа ретінде көрсету болып табылады. Сонымен бірге NoC архитектурасы байланыс орнату конвейеризациясымен, ауыстырылумен, NoC тестілеу желі компоненттерінің кідірсімен анықталатын байланыс модульдерінің ішкі сегменттердің ауыстырылу сияқты, құрылымның блоктар арасындағы контактілердің конвейерлі типін қолдайды.

NoC тестілеу. Желі кристалдағы жүйеден болғандықтан, тестілеуге жарамды жобалау құралдары(DFT) мен міндетті әдістерін пайдалану сияқты ұқсас мәселелер тестілеудің (ТАМ) бар SoC технологиялары мен механихмдердің адаптациясын ұсынады. NoC тестілеуінің стратегиясы негізгі үш мәселені шешуге бағытталған: 1) функционалды модульдер мен жады блоктары және сәйкес интерфейс желілерін тестілеу. ТАМ механизмі сәйкес жадыдан немесе тестіленетін модуль мен жады блогы генераторынан тесттік жинақтарды транспортирлеу үшін қолданылады. Желінің тұрақтылығы есебінен бір мезеттік және параллель әрбір модуль үшін тестік ресурс жүктеу мүмкіндігі бар. Осыдан кейін, функционалды блоктарға тест беру және оларды тестілеу процестерді параллельдеу мүмкіндігін береді және желінің кеңістіктік сипаттамасын қолдануынан тестілеу уақыты азаюы мүмкін. Байланыстар арасындағы қадағалау салыстырмалы түрде төмен, ойткені олар кристалда неғұрлым терең орналасқан. Кристалдардағы сыртқы қысқыштардың санына шектеу тестілеу процесі кезіндегі байланыстардың кіріс-шығыс санына әсер етеді. NoC инфрақұрылымы өзнің компоненттерін рекурсивті процедурада - тексерілген модульдер әлі тексерілмеген блоктардың тесттік жинағын транспортиртлеу үшін тестілеуде пайдалануы керек. Тестілеу стратегиясы қосымша мехнизмдерді мәліметтерді желі компоненттеріне транстпортирлеу үшін қолданылуды минимизациялайды және топтық мәлімет тарату үшін параллель жолдарды пайдалану арқылы тестілеу уақытын азайтады. Байланыс арасындағы инфрақұрылым мен функционалды блокты бөлек тестілеу тест сапасын қажетті талаптарға жету үшін жеткілікті болып табылмайды. 2) Байланыстар арасындағы инфрақұрылымды тексеру(блоктар арасындағы және блоктардың ішіндегі). Функционалды модульдар мен коммуникация құрылымы арасындағы өзара әрекет толық функционалды тесттермен тексеріледі. 3) интеграцияланған жүйені тестілеу тұтаста й әрбір процессорлық элементтің кіріс-шығыс функцияларды тексеруін, сонымен қатар мәліметтердің өту маршрутының барлық функцияларын қамту қажет.

SoC I-IP-мен ұқсас, NoC сапасы мен кепілділігін қамтамасыз ету үшін IEEE 11.49 және 1500 стандартын қолдану негізінде желінің сервистік қызмет ету(I-IP) инфрақұрылымын құру қажет және келесідей компоненттері болуы қажет: 1) IEEE 1500 шекаралық сканерлеу стандартын пайдалану негізіндегі блоктардың қызмет атқару, верификация, және тестілеу процесінде ішкі және шығыс желілерінің күйлер мониторингі[3]. 2) Дефекттерді тексеру немесе жөнделетін тәртіпке бағдарланған функционалды модульдерді тестілеу. 3) IEEE 1500 [3] негізіндегі тестілеу кезінде және орнатылған қателерді анықтаудың арнайы әдістерін қолданудан алынған ақпарат анализі жолымен тоқтау диагностикасы. 4) диагностика жасауда дефект түрін және орнын анықтаудан кейін кристалдардағы сандық жүйелердің жадыларын және функционалды модульдерін жөңдеу. 5) функционалды блоктарды диверсификация және қосарланушылық сандық құралдың қызмет атқару кепілділігімен қамтамасыз ету.

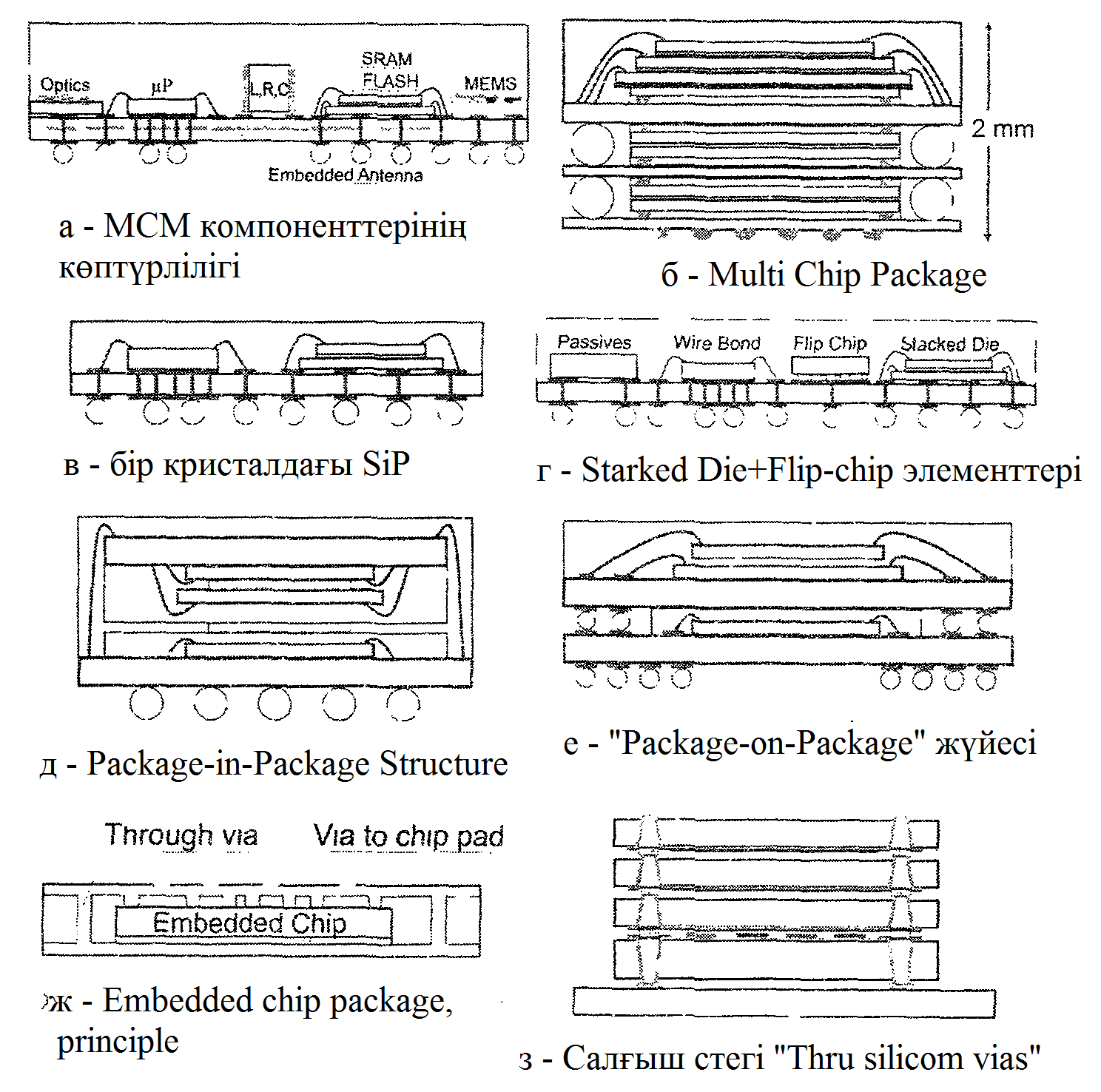

1 2 3 System in Package(SiP) пакетіндегі жүйе - бір корпуста жүзеге асу қызметін атқаруды көрсететін, жалпы салғышта орналасқан кристалдардың жиынтығы, SiP өзіне осындай пассивті компоненттерін қосады: дискретті элементтер; интегралды пассивті схемалар; подложкаға орналастырылған пассивті элементтер; беттік-акустикалық толқындағы фильтр түріндегі электромагниттік экрандар (EMI shield) арнайы белгіленген компоненттер; пакеттелген кристалдар, сыртқы байланыс және механикалық элементтер.

Пакеттегі жүйелерді дәстүрлі пайдалану: қорек көзін басқару, сонсорлық құрылғылар, ұялы телефония үшін RF және wireless қосымшалар, жоғары өндіргішті есептеулер үшін құрылғылары, қалта компьютерлері – PDA, жаһандық навигация жүйелері және түрғылыұты орнын анықтау –GPS, Wi-Fi және Bluetooth құралдары.

Цифрлық құрылғыларды жасау үшін силиконды кристалдардың функционалды ерекшеліктері келесі қасиетіне байланысты классификациялануы мүмкін [6,7,10] 1) Технологиялар: сандық, аналогтық, RF, оптоэлектронды, MEMS, пассивті; 2) Жиілік: сандық құрылғылар және RF үшін МГц бастап микротолқын компоненттері үшін ГГц-ке дейін; 3) кіші және үлкен қуатты аналогты құрылғылар архитектурасы; мәліметтермен және жағдайлармен басқарылатын нақты уақыттың сандық құрылымы; 4) Энергияны пайдалану: энергияны аз пайдаланатын прототипті құрылғы; 5) Басқа факторлар: формалар факторы, салмағы, жылу бөліну. Кристалдарды қаптаудың дәстүрлі әдістері келесі сипаттамалары бойынша шектеулермен сипатталады[7]. 1) Кристалдар арасындағы сигнал таратудың кідірулерімен, сигналдың ұлғаю уақыты, таралуымен анықталатын кристалдағы жүйенің өндіргіштігі. 2) кристалдағы жүйе корпусындағы отырғызатын орын ауданымен, өткізгіштер арасындағы саңылау және топология қабаттары санымен анықталатын миниартюрлеу. Кристалдар пакетіндегі жүйе ауданын кішірейту және оның өндіргіштігін арттыру міндеті өзекті болып табылады.

SiP бұрынғы MCM(Multichip Module), MCP-Multi-Chip-Package технологиялардын дамуын қамтиды және бір немесе одан көп кристалдардың болуымен сипатталады, өткізгіштік монтаж және кері кристалл әдісі монтажы технологияларымен алмастырылады , салңыштағы(подложка) қысқыштар, бір салғыш пассивті компоненттермен, фильтрлармен және антенналармен бірге логика мен жадының орналасуы. МСМ модульдің көптүрлі компоненттері 1.4, а суретте көрсетілген.

Қазіргі уақытта электронды технология нарығы кристалдарды үшөлшемді ораудың бес концепциясын ұсынады:

«Multichip Package» [7.10]. Кристалдар горизонталь жазықтықта орналасады, форма-фактордың минималды мәнін қамтамасыз ету мақсатында бір-біріне қабатты түрде немесе алмастырылған 3D құрылымын құруы мүмкін. «Multichip Package» конструкциясы жоғары өндіргіштікпен, кіші өлшемі мен салмағымен, сонымен қатар, сигнал таралуының минималды кідіруімен сипатталады.

1.4-сурет. Пакеттердегі сандық жүйелердің конструктивтері

2. «System-in-Package»[7,9,10] SiP көптүрлілігі метрикасына негізделген. 1) горизонталь жазықтықта орналастыруға болатын компоненттерді пайдалану(side-by-side)(1.4в сурет); сымды монтаж технологиясы мен термокомпрессорлы микродәнекерлеу Wire Bond; Tape Automated Bonding(TAB) полимерлі материалынан және/немесе кері кристалл flip-chip әдісімен жөнделетін компоненттерден жасалатын икемді таспа жолақтағы кристалдар монтажы. 2)шар сияқты қышқыштары немесе Wire Bond технологиясымен жөнделетін, сонымен қатар flip-chip компоненттері бар BGA(Ball Grid Array) модульдері түріндегі «құрамды кристалл» түрін көрсететін құрастыратын бірліктеріне ие компоненттерін пайдалану(1.4г сурет) 3) салғышқа орналастырылған компонеттерді пайдалану. Горизонталь жазықтыққа орналастырумен салыстырғанда Stacked Die түріндегі құрастыратын бірлікте жылдам әрекеттілікті арттыру, пайдаланатын қуат пен габаритті өлшемді кішірейту және жұмыстық зонадағы температуралық режимді жақсартуға мүмкіндік береді. Жеке кристалдарды штатты режимнен автономды тестілеу режиміне ауыстыру жеткілікті болуы мүмкін. Кері кристалл компоненттер монтажы технологиясын пайдалану форма-факторды жақсартуға, паразитті сыйымдылықты кішірейтуге және топология элементтері арасындағы индуктивтілік мүмкіндік береді.

3. «Package-in-Package»(PiP)[9,10]. Пакет толық тексерілген модульдің(Internal Stacking Module, ISM) жинағы мен стегінен тұрады, бірыңғай конструктивті құрал жасау мақсатында базалық құрастыратын пакетте (Base Assembly Package) орналасқан(1.4 д сурет)

4. «Package-on-Package»(PoP) [8,9,10]. Толығымен тексерілген пакеттер бір-бірімен вертикал орналасқан құрылымды көрсетеді. Осының нәтижесінде интеграция деңгейі әртүрлі болуы мүмкін. Берілген концепция төменгі базалық пакетте орналастырылған ораудың жоғары тығыздығымен және жоғарғы пакетте орналастырылатын жоғары сыйымдалықты бір немесе бірнеше есте сақтау құрылғысымен сандық немесе аналогты-сандық логикалық құрылғыларды құру үшін ең көп қолданыс тапты. Amkor Tefhnology компаниясы кристалдың үш өлшемді орау технологиясын (3D packaging technologies) енгізу және оны жасаудағы көшбасшысы болып табылады. жоғарғы пакет – жады модулі- FBGA(Fine Pitch BGA) корпусында немесе Stacked CSP(Chip Scale Package) орналасады, ал төменгі-логикалық модуль-PSvfBGA(Package Stackeble Very thim Fine Pitch BGA) корпусында орналасуы кезінде PoP конструктивті шешімінің мысалы болып табылады. (1.4 е сурет).

5. «Embedded chip technologies», «Subtrate Technology» [7,10]. Байланыстар арасы микросаңылау арқылы жүзеге асырылатын активті және пассивті кристалдар салғышқа орналасады(1.4,ж сурет). «Water Level» технологиясы кристалды салғышта, салғыш салғышқа ретімен орналасуына(1.4, з сурет) және Thru Silicon Vias(TSV) байланыстар арасы технологиясын жүзеге асыруға мүмкіндік береді. Water Level технологиясы интеграцияның жоғары деңгейімен сипатталады және кемшілік қатарына ие: жобалаудың жоғары құны және кристалл пакеттеріндегі сандық жүйелердің өндірісі; түрлі өндірушілер және түрлі технологиямен жасалатын компоненттерді пайдалану; жүйенің жұмысқа қабілеттілігін қалпына келтіру процесінің күрделілігі; басқа технологиялармен салыстырғанда жарамды құралдардың шығуына қатысты төмен проценті. Көпкристалды модульді IPC-VC-790(Guidelines for Multichip ModuleTechnologyUtilization) қолдану бойынша стандарты салғышты жасаудың үш түрлі технологиясын анықтайды: көп қабатты(Laminated); жұқа пленка технологиясы пайдалану арқылы керамикалық(Confired) және шаңдату технологиясы арқылы құрылатын салғыш.

Салғышты активті пайдалану негізіндегі кристалды үш өлшемді орау ерекшеліктері. 1) миниатюрлеу – топология мен орау тығыздығын арттыру және ол келесі түрде анықталады. Peff=TotalActiveSiliconArea/TotalActiveSiPArea(%), мұндағы Peff - орау тығыздығы; TotalActiveSiliconArea – кристалдың активті ауданы, TotalActiveSiPArea – SiP кристалдардың пакетіндегі сандық жүйенің активті ауданы; WiringDensity=Wiring Length/SiliconArea(cm/cm2), мұндағы WiringDensity – топология тығыздығы; Wiring Length – байланыстардың суммарлы ұзындығы; SiliconArea – кристал ауданы. 2) Өндіргіштікті арттыру. Жүйелік деңгейде оны бағалау үшіін келесі «цикл уақыты» параметрі қолданалады.

CycleTime= Time for Semiconductor / Time for Package,

Мүндаңы CycleTime – цикл уақыты, Time for Semiconductor – жартылай өткізгіш үшін цикл уақыты; Time for Package – кристалл пакеті үшін цикл уақыты.

3) жарамды құралдар шығару процентін жоғарылату есебінен пакет құнын төмендету және жүйені корпуска орау кезеңін шеттету, бұл деген өндіріс процесінен сәйкес операцияларды алып тастауды білдіреді.

4) Байланыстардың суммарлы ұзындығын кішірейту арқылы жүйенің кепілділігін жақсарту және тікелей көп қабатты салғышта корпусы жоқ кристалдарды орналастыру есебінен пакеттегі қабаттар саны.

Салғыш технологиясын пайлану мәселелері: 1) өндірістің жоғары құны; 2) шешім қабылдау процесінің күрделілігі(Decision Making Processз); 3) бар модельдерді қолданудын мүмкін еместігі 4) корпусы жоқ кристалдардың кепілсіз сапасы; 5) кристалдардың пакетін жинау операциясынан кейін жарамды құралдардың шығуының төменгі проценті; 6) жұмысқа қабілеттілікті қалпына келтіру күрделі процесі; 7) жобалау автоматизациясы құралдарының шектелген жиынтығы(CAD Tools); 8) оптимальды жылу режимімен қамтамасыз ету күрделілігі.

SiP негізіндегі пайдаланылатын өнімдерге қатысты заманауи нарықтың статистикасы: 33% - арнайы тапсырыспен алынған заттар; 20% - телекоммуникация құралдары; 20% - компактті энергия сақтайтын есептеуіштер, 10% - әскери немесе авиағарыштық белгілеу.

Салғыш технологиялары: 58% - керамикалық; 39- көп қабатты; 3% -шаңдату Deposited монтаж технологиясы. WireBond, TAB, FlipChip. Тестке жарамдылықты қамтамасыз ететін технологиялар: 50% - Boundary-Skan; 54% - схема ішіндегі бақылау нүктелерін зондтау(Internal Test Points Probed), 69% - дефектті SiP жұмысқа жарамдылығын қалпына келтіру.

Жарамсыздық түрлері: дефекттердің көп проценті кристалдардың жұмыс қабілетімен байланысты. Тестілілеудің автоматизация технологиясы: 46% - арнайы тесттік жинақ(Custom Test Sets), 37% - тестерлерді пайдалану(IC Testers). Пакеттік технологияларды дамыту бағыттары, кристалл күрделілігін кристалдағы 700 млн транзисторға дейін арттыру; кристал ауданын кішірейту; түйіндер санын 10К дейін ұлғайту; шар қысқыштарын 50 мкм кадамымен пайдалану.