- •Введение

- •Архитектура микроконтроллера.

- •1.1 Структурная организация микроконтроллера i8051.

- •Назначение выводов микроконтроллера 8051.

- •1.2 Память

- •Память программ

- •Масочная память

- •Однократно программируемая память

- •Репрограммируемая память

- •Память с электрическим стиранием

- •Флэш-память

- •Память программ микроконтроллера 8051 (пзу).

- •Память данных

- •Статическая память

- •Память с электрическим стиранием

- •Память данных микроконтроллера 8051 (озу).

- •Специализированные ячейки флэш-памяти

- •Работа с внешней памятью микроконтроллера 8051.

- •1.3 Процессорное ядро

- •Регистр инструкций

- •Программный счетчик

- •Арифметико-логическое устройство

- •Арифметико-логическое устройство микроконтроллера 8051.

- •Регистры общего назначения

- •Регистр состояния

- •Регистр флагов (psw) микроконтроллера 8051.

- •Регистры ввода/вывода, специальные регистры.

- •1.4 Тактовый генератор

- •1.5 Система сброса

- •Источники сброса

- •1.6 Система прерываний

- •Алгоритм обработки прерываний

- •Система прерываний микроконтроллера 8051.

- •Регистр масок прерывания (ie).

- •Регистр приоритетов прерываний (ip).

- •Выполнение подпрограммы прерывания.

- •Вектора прерываний

- •1.7 Порты ввода/вывода организация ввода/вывода

- •Алгоритмы обмена данными

- •Асинхронный обмен

- •Симплексный обмен

- •Устройство портов.

- •Особенности электрических характеристик портов.

- •1.8 Таймеры-счетчики.

- •Таймеры-счетчики микроконтроллеров семейства 8051.

- •1.9 Последовательный порт микроконтроллера 8051.

- •Регистр управления/статуса приемопередатчика scon.

- •Функциональное назначение бит регистра управления/статуса приемопередатчика scon.

- •Скорость приема/передачи информации через последовательный порт.

- •Регистр управления мощностью pcon.

- •1.10 Режимы работы микроконтроллера 8051 с пониженным энергопотреблением.

- •Режим хх.

- •Режим внп.

- •1.11 Устройства ввода/вывода дискретных сигналов

- •1.12 Устройства ввода/вывода аналоговых сигналов

- •Интегрирующий преобразователь

- •Сигма-дельта преобразователь

- •1.13 Устройства обмена данными с другими микроконтроллерами

- •2. Программирование микроконтроллера

- •2.1 Система команд Мнемонические обозначения

- •Типы команд

- •Типы операндов

- •Группы команд.

- •Oбозначения, используемые при описании команд.

- •Команды пересылки данных микроконтроллера 8051.

- •Команды арифметических операций 8051.

- •Команды логических операций микроконтроллера 8051.

- •Команды операций над битами микроконтроллера 8051.

- •Команды передачи управления микроконтроллера 8051.

- •2.2 Язык ассемблера

- •Операнды

- •Операторы

- •Директивы ассемблера.

- •Командная строка

- •2.3 Особенности программирования микроконтроллеров общие особенности.

- •Типы инструментальных средств разработки и отладки программ для микроконтроллеров.

- •Внутрисхемные эмуляторы.

- •Классификация внутрисхемных эмуляторов.

- •Функциональные возможности внутрисхемных эмуляторов.

- •Достоинства и недостатки внутрисхемных эмуляторов.

- •Программные симуляторы.

- •Платы развития.

- •Отладочные мониторы.

- •Эмуляторы пзу.

- •Типичные функциональные модули средств разработки и отладки.

- •Отладчик.

- •Узел эмуляции микроконтроллера.

- •Эмуляционная память.

- •Подсистема точек останова.

- •Процессор точек останова.

- •Трассировщик.

- •Профилировщик.

- •Интегрированная среда разработки.

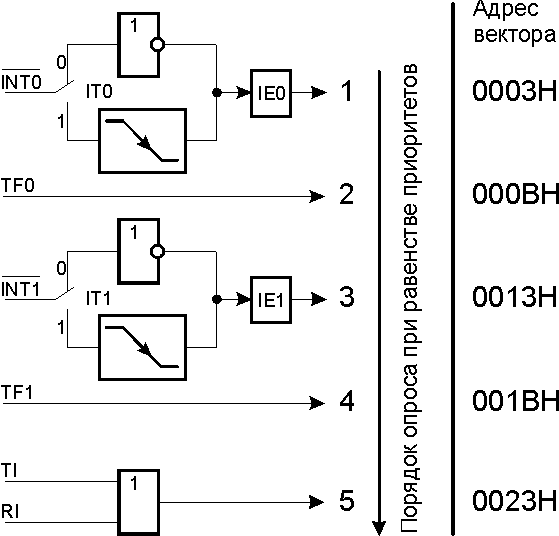

Система прерываний микроконтроллера 8051.

Исходная система прерываний в архитектуре MCS-51 включает пять источников - два внешних и три внутренних.

Из пяти источников прерываний внешними являются входы INT0# и INT1#, а внутренними - два счетчика/таймера и последовательный порт. Активные сигналы на входах INT0#, INT1# устанавливают флаги IE0, IE1 регистра TCON. Таймер 0 и Таймер 1 используют для выработки запросов прерываний флаги переполнения TF0, TF1 в регистре управления TCON, а последовательный порт использует для этого два флага - приемника RI и передатчика TI в регистре управления SCON. Каждый из флагов последовательного порта может вызвать прерывание, а конкретный источник определяет процедура обслуживания посредством опроса.

Упрощенная схема прерываний микро-ЭВМ 8051 показана на рисунке.

Рисунок 1.5 Схема прерываний.

Внешние прерывания INT 0 и INT 1 могут быть вызваны либо уровнем, либо переходом сигнала из 1 в 0 на входах 8051 в зависимости от значений управляющих бит IT0 и IT1 в регистре TCON. От внешних прерываний устанавливаются флаги IE0 и IE1 в регистре TCON, которые инициируют вызов соответствующей программы обслуживания прерывания. Сброс этих флагов выполняется аппаратно только в том случае, если прерывание было вызвано по переходу (срезу) сигнала. Если же прерывание вызвано уровнем входного сигнала, то сбросом флага I должна управлять соответствующая подпрограмма обслуживания прерывания путем воздействия на источник прерывания с целью снятия им запроса.

Флаги запросов прерывания от таймеров TF0 и TF1 сбрасываются автоматически при передаче управления подпрограмме обслуживания. Флаги запросов прерывания RI и TI устанавливаются блоком управления приемопередатчика аппаратно, но сбрасываться должны программным путем.

Прерывания могут быть вызваны или отменены программой, так как все названные флаги программно доступны и могут быть установлены/сброшены программой с тем же результатом, как если бы они были установлены/сброшены аппаратными средствами.

В блоке регистров специальных функций есть два регистра, предназначенных для управления режимом прерываний IE и уровнями приоритета IP. Возможность программной установки/сброса любого управляющего бита в этих двух регистрах делает систему прерываний 8051 исключительно гибкой.

В более сложных модификациях микроконтроллеров семейства MCS-51 количество периферийных устройств увеличено, что приводит к необходимости использовать один вектор прерывания для нескольких устройств (разделение подпрограмм обслуживания прерываний в этом случае необходимо реализовать программно), либо добавить еще два регистра - режима (маски) и приоритета прерываний.

Каждый из источников прерываний может быть разрешен или запрещен с использованием соответствующего бита регистра IE. Кроме того, в этом регистре есть бит общего запрета всех прерываний.

Регистр масок прерывания (ie).

Символ |

Позиция |

Имя и назначение |

EA |

IE.7 |

Снятие блокировки прерывания. Сбрасывается, программно для запрета всех прерываний независимо от состояний IE.4 - IE.0 |

|

IE.6 |

Не используется |

|

LE.5 |

Не используется |

ES |

IE.4 |

Бит разрешения прерывания, от приемопередатчика Установка/сброс программой для разрешения/запрета прерываний от флагов TI или RI . |

ET1 |

IE.3 |

Бит разрешения прерывания от таймера. Установка/сброс программой для разрешения/запрета прерываний от таймера 1 |

EX1 |

IE.2 |

Бит разрешения внешнего прерывания 1. Установка/сброс программой для разрешения/запрета прерывания 1 |

ET0 |

IE.1 |

Бит разрешения прерывания от таймера 0. Установка/сброс программой для разрешения/запрета прерываний от таймера 0 . |

EX0 |

IE.0 |

Бит разрешения внешнего прерывания 0. Установка/сброс программой для разрешения/запрета прерывания 0 |

Таблица 1.6 Регистр масок прерывания.

При появлении запросов от нескольких источников очередность их обслуживания определяется с помощью механизма приоритетов прерываний. В архитектуре MCS-51 имеет место двухступенчатый механизм определения приоритетов. В исходной системе прерываний микроконтроллеров 8051 АН приоритеты на первой ступени имеют два уровня: «высокий» и «низкий», и определяются значениями битов регистра IP.