- •1.Компоненты и задачи архитектуры ртк

- •2. Требования к архитектуре ртк

- •3. Су с одним управляющим модулем.

- •4.Распределенные системы управления(рсу).

- •5.Многоуровневые системы управления.

- •6. Общие сведения о промышленных сетях

- •7.Модель osi.

- •9. Интрефойс rs-485

- •10. Интерфейс rs-422

- •11. Интерфейс rs-232.

- •12. Интерфейс токовая петля.

- •13.Hart-протокол

- •14. Интерфейс Profibus

- •15. Интерфейс Modbus

- •16. Беспроводные локальные сети (блс)

- •17. Пк в качестве контроллера.

- •18. Промышленные компьютеры.

- •19. Конструктивные характеристики плк

- •20. Эксплуатационные характеристики плк

- •21. Архитектура плк.

- •22. Характеристика основных компонентов плк.

- •23. Особенности мк.

- •24. Типы мк.

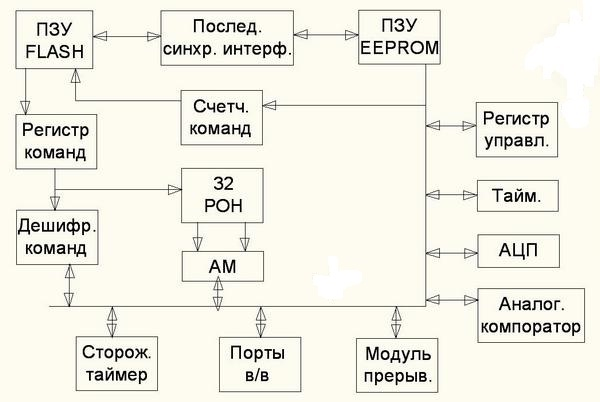

- •25. Архитектура мк.

- •26. Характеристика основных компонентов мк.

- •27. Структура устройств аналогового ввода

- •28. Структура устройств аналогового вывода

- •29. Структура устройств дискретного ввода.

- •30. Структура устройств дискретного вывода

- •31. 32. Ввод частоты и периода

- •33. Особенности плк, мк для управления движением.

- •36. Структура учпу.

- •37. Составные части учпу.

- •40. Полуавтоматические загрузочные устройства.

- •41. Автоматические загрузочные устройства.

- •42. Типы накопителей.

- •43. Типы транспортных модулей.

- •44. Колесные транспортные модули

- •45. Системы ориентации транспортных модулей.

25. Архитектура мк.

Перифер. уст-ва имеет:

- 8 бит. таймер – счетчик;

- 16 бит. таймер – счетчик;

- сторожевой таймер;

- одно- и двухканальные генераторы 8 бит. ШИМ сигнала;

- генераторы ШИМ сигнала регулир. разрядности;

- аналоговые компараторы;

- последовательный двунаправленный интерфейс;

- до 4х полудуплексных синхронных/асинхронных приемопередатчиков;

- универсальный последовательный интерфейс.

Ядро МК имеет вид:

АЛУ выполняет все вычисления подключ. непосред. к 32-м рабочим регистрам, объедененным в регистровый файл. Благодаря этому АЛУ может выполнять одну операцию, т.е. чтение содержимого регистра, выполнение операций, запись рез-та обратно в регистровый файл и всё это за один такт.

В этих МК реализована гарвардская архитектура, характеризующаяся разделение памяти программ и данных, каждый из которых имеет собственные шины доступа. Такая организация позволяет одновременно работать как с памятью программ, так и с памятью данных. Разделение информационных шин позволяет использовать для каждого типа памяти шины различной разрядности, причем способы адресации и доступа к каждому типу памяти также различны. Всё это позволяет достичь быстродействия 1 млн. опер./с при частоте 1 МГц.

Структура МК ATMega8:

1 – сторожевой таймер, 2 – узел супервизора питания, 3 – генератор сторожевого таймера, 4 – флеш память программ, 5 – ОЗУ, 6 – узел управления и синхронизации, 7 – ППЗУ с электрическим стиранием, 8 – таймер-счетчик 8 бит.(t0), 9 - таймер-счетчик 16 бит.(t1), 10 – АЦП, 11 - таймер-счетчик 8 бит.(t2), 12 – аналоговый компаратор, 13 – внутренний источник опорного напряжения, 14 - синхронно/асинхронный приемопередатчик, 15 – последовательный порт, 16 – двунаправленный приемопередатчик, 17 – порт D 8 бит., 18 – порт B 8 бит., 19 – порт C 7 бит..

МК ATMega8 ЭВМ фирмы Atmel явл. 8 бит. МК предназначенным для исп. во встраеваемых приложениях. Они изготовлены малопотребл. КМОП технологии, кот. в сочетании с усоверш. RISC архитектурой позволяет добиться наилучшего соотношения стоимость – быстродействие – энергопотребление.

26. Характеристика основных компонентов мк.

Обычно в составе МК присутствуют следующие периферийные устройства:

- универсальные цифровые порты;

- различные интерфейсы;

- АЦП и ЦАП;

- компараторы;

- ШИМ;

- таймеры;

- контроллеры безколлекторных двигателей;

- радиочастотные приемники и передатчики;

- встроенный тактовый генератор;

- контроллеры дисплеев и клавиатур.

Хар-ки процессора:

- АЛУ подлючается непосредственно к регистрам общ. назначения;

- больш. команд вып. за один такт;

- векторн. сист. прерываний;

- наличие аппаратного умножителя;

- полностью статическая архитектура (мин. такт частота = 0).

АЛУ выполняет все вычисления подключ. непосред. к 32-м рабочим регистрам, объедененным в регистровый файл. Благодаря этому АЛУ может выполнять одну операцию, т.е. чтение содержимого регистра, выполнение операций, запись рез-та обратно в регистровый файл и всё это за один такт.

Хар-ки подсистемы в/в:

- программн. конфигурирование и выбор портов в/в;

- входные буферы с триггером Шмидта на всех выводах;

- на всех входах имеются индукт. отключаемые внутренние подтягивающие регистры.

Порты в/в:

Каждый порт МК сост. из опред числа выводов через кот может осущ как прием , так и выдача инф. Задание направления передачи данных через любой контакт может быть произведено программно в любой момент времени. Выходные буферы портов симетр. нагрузочную характеристику обеспеч. высокую нагрузочную способность при любом уровне сигнала. Нагрузочной способности достаточно для непосредственного управления светодиодными индикаторами.

Широтно Импульсная Модуляция (PWM - Pulse Width Modulation) это способ задания аналогового сигнала цифровым методом, то есть из цифрового выхода, дающего только нули и единицы получить какие-то плавно меняющиеся величины. При ШИМ на выход подаётся сигнал состоящий из высоких и низких уровней (включаем и выключаем двигатель), то есть нулей и единицы. А затем это все пропускается через интегрирующую цепочку (в случае с двигателем интегратором является маховик). В результате интегрирования на выходе будет величина напряжения, равная площади под импульсами. ATMega8 имеет аппаратные средства для генерирования сигналов ШИМ. Для этого используется Таймер/Счётчик 1 (16 бит) или Таймер/Счётчик 2 (8 бит), включённый в соответствующем режиме.