Перепрограммируемые или многократно программируемые зу

Различаются элементы со стиранием информации ультрафиолетовыми лучами (EPROM - erasable programmable ROM- стираемое программируемое ЗУ) и с электрическим стиранием (EEPROM).

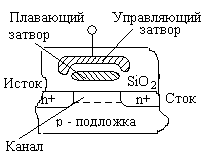

П ПЗУ

выполняются по ЛИПЗМОП – технологии

(лавинно-инжекционные элементы памяти

с плавающим затвором) (см. рис.). В исходном

состоянии плавающий затвор, изолированный

слоем окиси кремния, не заряжен и

транзистор работает как обычный полевой

с индуцируемым каналом n-типа.

В ЗУ исток транзистора обычно соединен

с общей шиной и при приложении высокого

потенциала к затвору (выше порогового

уровня ) транзистор открывается. На шину

данных выставляется логический ноль.

Для записи логической единицы повышают

напряжение между стоком и подложкой,

чтобы поднять энергию электронов,

движущихся в канале. Часть электронов

проходит через слой окиси кремния и

накапливается на плавающем затворе,

заряжая его отрицательно и экранируя

тем самым заряд управляющего затвора.

Теперь при считывании транзистор всегда

будет заперт. Для удаления заряда

плавающего затвора затворы транзисторов

облучают ультрафиолетовым светом в

течение 20 – 30 мин. Энергия электронов

в плавающем затворе повышается, окись

кремния ионизируется, уменьшая

сопротивление, и заряд затвора

рассасывается. Срок хранения информации

в таких ЗУ составляет 15000 – 25000 часов.

Количество циклов стирания – записи –

до 10000. Основная отечественная серия –

573. Емкость достаточно большая (573РФ2 –

2Кх8).

ПЗУ

выполняются по ЛИПЗМОП – технологии

(лавинно-инжекционные элементы памяти

с плавающим затвором) (см. рис.). В исходном

состоянии плавающий затвор, изолированный

слоем окиси кремния, не заряжен и

транзистор работает как обычный полевой

с индуцируемым каналом n-типа.

В ЗУ исток транзистора обычно соединен

с общей шиной и при приложении высокого

потенциала к затвору (выше порогового

уровня ) транзистор открывается. На шину

данных выставляется логический ноль.

Для записи логической единицы повышают

напряжение между стоком и подложкой,

чтобы поднять энергию электронов,

движущихся в канале. Часть электронов

проходит через слой окиси кремния и

накапливается на плавающем затворе,

заряжая его отрицательно и экранируя

тем самым заряд управляющего затвора.

Теперь при считывании транзистор всегда

будет заперт. Для удаления заряда

плавающего затвора затворы транзисторов

облучают ультрафиолетовым светом в

течение 20 – 30 мин. Энергия электронов

в плавающем затворе повышается, окись

кремния ионизируется, уменьшая

сопротивление, и заряд затвора

рассасывается. Срок хранения информации

в таких ЗУ составляет 15000 – 25000 часов.

Количество циклов стирания – записи –

до 10000. Основная отечественная серия –

573. Емкость достаточно большая (573РФ2 –

2Кх8).

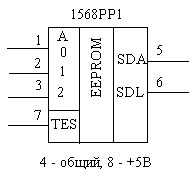

Э лектрически

стираемые программируемые ПЗУ (EEPROM)

также как предыдущие ЗУ выполняются по

ЛИПЗМОП – технологии, но изолирующая

окисная пленка между плавающим затвором

и каналом имеет меньшую толщину, что

позволяет электрически управлять не

только накоплением заряда плавающего

затвора, но и рассасыванием его. Как

запись, так и стирание происходят при

повышенном напряжении. ИС более ранних

выпусков имеют специальный вход для

подачи высокого (до 25 В) напряжения (см.

ИС 558РР1, 558 РР11), современные схемы

зачастую используют встроенные схемы

повышения напряжения (1568РР1, РР2).

Особенностью последних элементов

является последовательная организация

процессов передачи адреса и данных

(шина I2C),

что позволяет использовать корпус с

малым количеством выводов, наличие

внутреннего счетчика адреса и схемы

исправления внутренних единичных

ошибок. Для ИС 1568РР1, емкостью 256Х8 бит,

назначение выводов следующее: А0-А2

локальный адрес ИС, устанавливаемый

коммутацией выводов на шины «0», «+5В»,

и позволяющий подключать к одной шине

I2C до

8 ИС; TES – тактовый сигнал

при стирании; SDA –

информационный вход/выход; SDL

– тактовый сигнал.

лектрически

стираемые программируемые ПЗУ (EEPROM)

также как предыдущие ЗУ выполняются по

ЛИПЗМОП – технологии, но изолирующая

окисная пленка между плавающим затвором

и каналом имеет меньшую толщину, что

позволяет электрически управлять не

только накоплением заряда плавающего

затвора, но и рассасыванием его. Как

запись, так и стирание происходят при

повышенном напряжении. ИС более ранних

выпусков имеют специальный вход для

подачи высокого (до 25 В) напряжения (см.

ИС 558РР1, 558 РР11), современные схемы

зачастую используют встроенные схемы

повышения напряжения (1568РР1, РР2).

Особенностью последних элементов

является последовательная организация

процессов передачи адреса и данных

(шина I2C),

что позволяет использовать корпус с

малым количеством выводов, наличие

внутреннего счетчика адреса и схемы

исправления внутренних единичных

ошибок. Для ИС 1568РР1, емкостью 256Х8 бит,

назначение выводов следующее: А0-А2

локальный адрес ИС, устанавливаемый

коммутацией выводов на шины «0», «+5В»,

и позволяющий подключать к одной шине

I2C до

8 ИС; TES – тактовый сигнал

при стирании; SDA –

информационный вход/выход; SDL

– тактовый сигнал.

К этому же типу ЗУ относятся flash EEPROM («мигающее» ЗУ), позволяющее стирать память по отдельным блокам.

Лекция 15

Программируемые логические интегральные схемы (ПЛИС) или устройства (PLD)

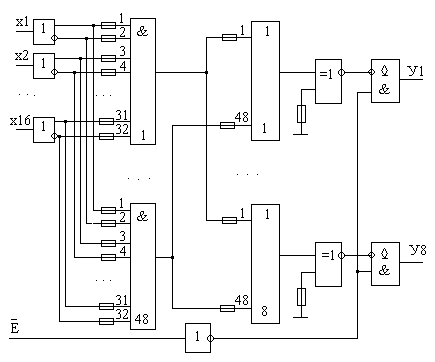

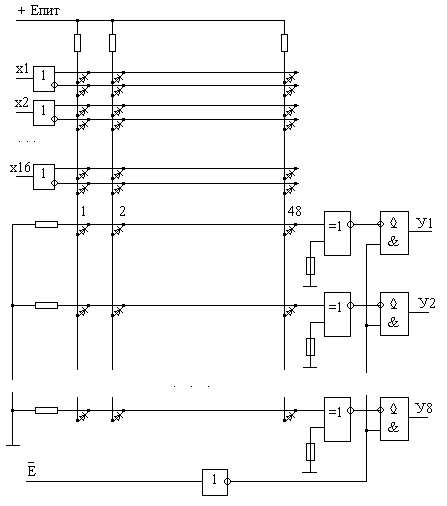

Программируемые логические матрицы (ПЛМ или FPLA – Field Programmable Logic Array, PLA, PAL - Programmable Array Logic) представляют собой комбинационную схему с программируемой структурой.

Структура не может быть полностью произвольной, наиболее часто ПЛМ состоит из программируемых матриц И и ИЛИ. Программирование осуществляется путем пережигания нихромовых или перемычек, разрушения переходов, либо путем программирования ЛИПЗМОП элементов. Структуру ПЛМ можно рассмотреть на примере ИС 556РТ1

К

ак

видно из схемы, программирование столбца

из 48 32-х входовых элементов И позволяет

получить 48 различных конъюнкций 16-и

разрядных входов х или их отрицаний.

Следующий столбец элементов ИЛИ дает

возможность сформировать 8 дизъюнкций

из полученных КНФ в прямом или инверсном

коде в зависимости от состояния

программируемых входов «исключающих

ИЛИ»: если на входе «0» – на выходе прямой

код дизъюнкции, если «1» - инверсный.

Передатчики с открытым коллектором

управляются сигналом разрешения Е.

ак

видно из схемы, программирование столбца

из 48 32-х входовых элементов И позволяет

получить 48 различных конъюнкций 16-и

разрядных входов х или их отрицаний.

Следующий столбец элементов ИЛИ дает

возможность сформировать 8 дизъюнкций

из полученных КНФ в прямом или инверсном

коде в зависимости от состояния

программируемых входов «исключающих

ИЛИ»: если на входе «0» – на выходе прямой

код дизъюнкции, если «1» - инверсный.

Передатчики с открытым коллектором

управляются сигналом разрешения Е.

Использование взамен перемычек прожигаемых диодов позволяет заменить элементы «И» «монтажным И» и «ИЛИ» - «монтажным ИЛИ».

Для прожига необходим специальный программатор.

В отличие от ПЗУ ПЛМ позволяет получать ДНФ для большего количества входных переменных (большей разрядности входа х), однако формируемые ДНФ могут использовать всего 48 элементарных конъюнкций из 65536.

В отечественной литературе зачастую термин ПЛИС относится к программируемым устройствам, описанным ниже.

GAL –Generic array Logic – базовая матричная логика

Имеют по сравнению с ПЛМ более широкие возможности за счет дополнения КС элементами памяти (обычно однобитовыми D-триггерами) и наличием обратных связей на матрицу И. Выполнены они по технологии EEPROM и допускают до 2000 стираний.

F PGA

– field programmable

gate arrays

- программируемые полем вентильные

матрицы

PGA

– field programmable

gate arrays

- программируемые полем вентильные

матрицы

Состоят из многих программируемых логических устройств, структура связей которых также программируется матрицей соединений. Используют в своем составе три типа устройств: собственно конфигурируемые (программируемые) логические блоки (КЛБ) с фиксацией информации на триггерах; программируемые устройства ввода/вывода и устройства коммутации с линиями связи (программируемые шины –ПШ).

Gate-Arrays – вентильные матрицы

Могут включать цифровые, аналоговые, смешанные модули.

В основном формируются из типовых устройств заданной структуры и исполнитель выполняет их соединение.