- •Часть 1. Микропроцессорные вычислительные машины.

- •Часть 2. Высокопроизводительные вычислительные системы.

- •Часть 3. Вычислительные сети.

- •1.4. Высокопроизводительные вычислительные системы.

- •.5. Вычислительные сети.

- •2. Курсовая работа

- •2.1. Общие указания по выполнению

- •2.2. Вопросы для изучения

- •2.3. Задание на курсовую работу

- •2.4. Исходные данные

- •2.5. Содержание отчёта

- •Задание на курсовую работу

- •2.6. Справочные материалы

- •2.6.1. Организация микропроцессорной системы

- •2.6.2. Элементная база

- •2.6.3. Описание основных используемых в работе команд

- •2.6.4. Дополнительная информация

- •Список литературы

2.5. Содержание отчёта

Отчёт о выполнении курсовой работы должен содержать:

Задание на курсовую работу

Функциональная схема микропроцессорной системы.

Программная модель микропроцессора.

Таблица распределения памяти и портов ввода/вывода.

Принципиальная схема микропроцессорной системы и схемы ее сопряжения с датчиками и исполнительными элементами.

Алгоритм и программа управления накопителем посылок.

Алгоритм и программа решающего устройства установки сортировки посылок.

Алгоритм и программа системы адресования установки сортировки посылок.

По пунктам 6–8 должны быть представлены следующие подразделы:

Алгоритм задачи

Программа задачи на языке ассемблер

Программа задачи в машинных кодах

Расчет быстродействия программы

Расчет требуемого объема памяти

2.6. Справочные материалы

Далее приведены базовые справочные данные, которые могут потребоваться в работе. Более подробную информацию можно найти в любом справочнике по цифровым микросхемам.

2.6.1. Организация микропроцессорной системы

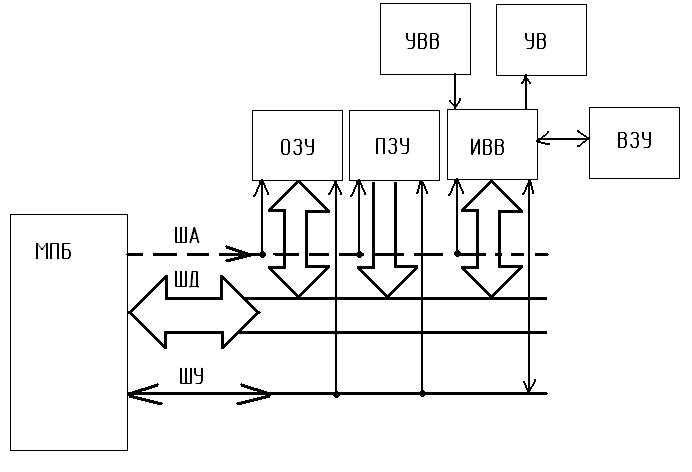

Обобщённая функциональная схема микро-ЭВМ состоит из микропроцессора (МП) с тремя шинами (адреса, данных, управления), генератора тактовых импульсов (ГТИ), постоянного (ПЗУ) и оперативного (ОЗУ) запоминающих устройств, интерфейсов ввода/вывода.

Выбран минимальный режим включения, так как максимальный режим ориентирован на применение микропроцессора в сложных одно- и многопроцессорных системах.

Система минимальной сложности состоит из ЦП КМ1810ВМ86, генератора тактовых импульсов КР1810ГФ84, двух или трёх буферных регистров КР580ИР82, обеспечивающих фиксацию 16- или 20-разрядного адреса. Подключение шины данных системы к выходам канала данных микропроцессора выполняется специальными схемами двунаправленных шинных формирователей КР580ВА86.

2.6.2. Элементная база

Далее приведены элементы, которые рекомендуется использовать при проектировании системы.

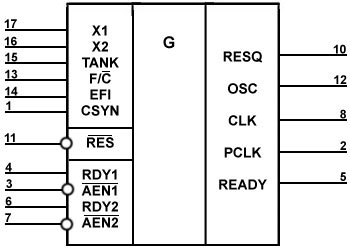

КР1810ГФ84

Схематическое обозначение |

Описание |

|

Тактовый генератор и задающее устройство для микропроцессора КМ1810ВМ86. Формирует тактовые сигналы для микропроцессора и периферийных устройств, а также сигналы «Установка» и «Готовность». В качестве источника частоты в микросхеме используется кварцевый резонатор, подключаемый к выводам Х1 и Х2. Выбранный источник должен генерировать на трехкратной частоте тактового сигнала CLK, требуемой для МП. Кроме того, возможно использование внешнего ТТЛ-сигнала для задания частоты (подается на EFI). |

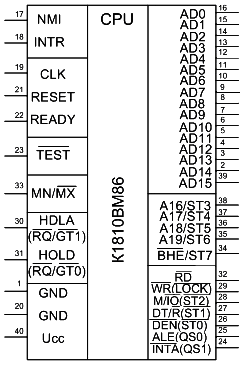

КМ1810ВМ86

Схематическое обозначение |

Описание |

|

Однокристальный 16-разрядный микропроцессор выполнен по n-МОП технологии и имеет архитектуру, однотипную с МП 8086 фирмы Intel. Обладает программной и аппаратной совместимостью с периферийными и контроллерными БИС серии КР580. Микропроцессор К1810ВМ86 реализован по традиционной архитектуре, в соответствии с которой производится последовательная выборка команд и данных из памяти с последующей обработкой данных в арифметическом устройстве в соответствии с выбранной командой. Работа МП осуществляется синхронно с тактовыми импульсами, поступающими на вход CLK. Характеризуется двумя режимами работы – минимальным и максимальным, которые отличаются способом формирования сигналов обмена и соответственно возможностями реализуемых систем. Режимы программируются входом MN/неMX. |

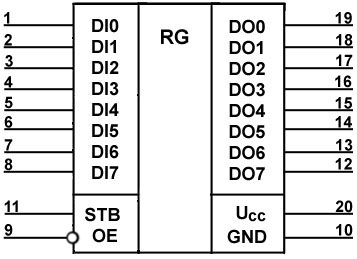

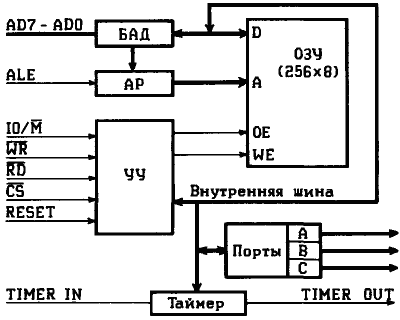

КР580ИР82

Схематическое обозначение |

Описание |

|

Буферный регистр. Данные регистры используются для организации запоминающих буферов, адресных защелок, портов ввода – вывода, мультиплексоров и т.п. При сигнале высокого уровня на входе STB состояние входных линий DI7-DI0 передается на выходные линии DO7-DO0. Запоминание в информационных триггерах осуществляется при переходе сигнала STB от высокого уровня к низкому (по срезу сигнала STB). |

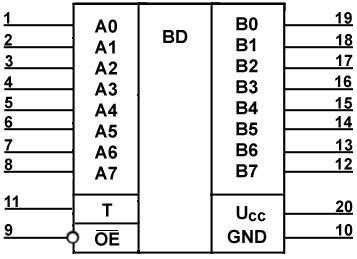

КР580ИР82

Схематическое обозначение |

Описание |

|

Буферное устройство шины данных. Большая выходная мощность и простота управления позволяют использовать его для построения двунаправленных согласующих буферов межмодульной связи либо как простые усилительные каскады. |

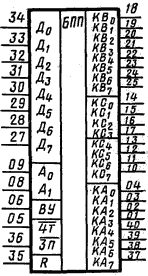

КР580ВВ55А

Схематическое обозначение |

Описание |

|

Программируемое устройство, используемое для ввода - вывода параллельной информации. Схема позволяет осуществлять обмен 8-разрядными данными по трем каналам: A, B, C. Направление обмена и режим работы для каждого канала задается программно. Каналы служат для передачи как данных, так и управляющих сигналов. Упрощенно схема состоит из регистра управления и трех регистров, предназначенных для ввода - вывода данных. Схема может выполнять следующие функции:

Режимы работы микросхемы К580ВВ55 задаются при её начальной установке. Четыре подадресных регистра схемы включают в себя три регистра каналов ввода - вывода данных (А, В, С) и регистр управления. Регистр канала С может быть подразделен на два четырехразрядных регистра ввода - вывода данных, к которым осуществляется доступ как к отдельным независимым регистрам. Имеется возможность подразделения трех каналов на две группы. В этих группах каналы A и B используются для обмена данными с микро-ЭВМ, а отдельные шины канала C - для записи управляющих сигналов. |

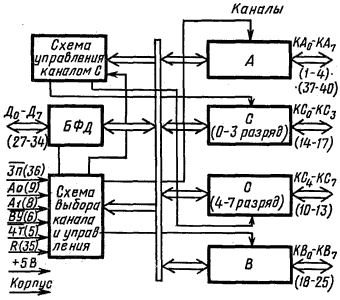

КР1821РУ55

Схематическое обозначение |

Описание |

|

БИС включает: статическое ОЗУ емкостью 2048 бит с организацией 256x8; два 8-ми битовых и один 6-и битовый порты; 14-и битовый программируемый таймер. Порты A и B одинаковы и каждый из них содержит 8-ми битовый регистр для буферного запоминания пересылаемого байта данных. Все разряды портов A и B используются для ввода или вывода параллельно. В зависимости от содержания РУС каждый порт A и B может работать в двух режимах: простого ввода-вывода (без обмена управляющими сигналами) или ввода-вывода с обменом УС.

|

К155ИД3

Схематическое обозначение |

Описание |

|

Дешифратор-демультиплексор 4 линии на 16. |

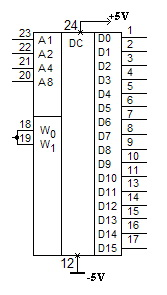

К155КП1

Схематическое обозначение |

Описание |

|

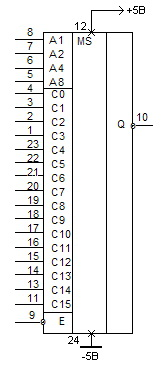

Селектор-мультиплексор данных на 16 каналов со стробированием. Позволяет с помощью четырех адресных входов A-F передать данные, поступающие на один из входов D0-D15 к выходу Y. Если на вход разрешения C подано напряжение высокого уровня, то на выходе Y также появится высокий уровень независимо от адреса остальных входов. Напряжение низкого уровня на входе E разрешает прохождение данных от входов D0-D15. |