- •1. Автоматическое и автоматизированное управление технологическими процессами горных предприятий.

- •2. Типовая схема микропроцессорной системы управления.

- •3. Микроконтроллеры и принципы их объединения в распределенные сети управления объектами.

- •4. Порты микроконтроллеров их назначение и типы. Протоколы обмена информацией между микроконтроллерами.

- •5. Основные функции и алгоритмы работы систем автоматического управления проходческими комбайнами.

- •6. Структура и функциональное назначение основных блоков микропроцессора.

- •7. Анализ вариантов автоматического регулирования нагрузки на приводе выемочных машин.

- •8. Структурная схема и принцип работы регулятора нагрузки на приводе выемочной машины типа саду-2.

- •9. Структурная схема и принцип работы импульсного пропорционального интегрального регулятора нагрузки на приводе выемочной машины типа ипир-3м.

- •10. Анализ способов автоматического направленного вождения проходческих комбайнов.

- •11. Структура и функциональное назначение основных блоков системы автоматического управления циклом бурения шпуров.

- •12. Основные требования к системам автоматического управления подземным конвейерным транспортом. Номенклатура технических средств реализации этих требований.

- •13. Основные требования к системам автоматического обеспечения безопасной работы подземного рельсового транспорта. Структурная схема аппаратуры «абсс».

- •14. Назначение, основные функции и структурная схема и принцип работы аппаратуры «нерпа».

- •15. Основные требования к системам автоматического управления шахтным подъемом. Номенклатура технических средств реализации этих требований.

- •Блокировка пуска подъемной машины.

- •Системы автоматизации шахтных подъемных установок должны обеспечивать блокировку запрещающую:

- •16. Принцип работы аппаратуры «азк-1» задания и контроля параметров шахтного подъема.

- •17. Основные требования к системам автоматизации проветривания шахт и реализация их в аппаратуре «уквг»

- •18. Основные требования к автоматизации шахтного водоотлива и реализация их в аппаратуре «уав».

- •19. Принципы автоматического поддержания давления на забой при бурении нефтяных и газовых скважин.

- •20. Принципы автоматического контроля дебита куста скважин.

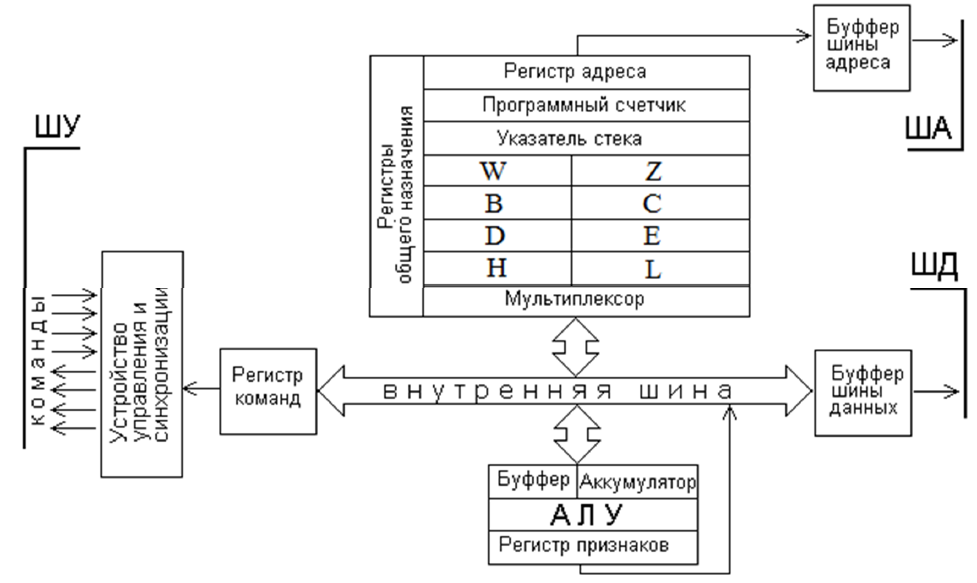

6. Структура и функциональное назначение основных блоков микропроцессора.

Микропроцессор (рис. 15) состоит из следующих структурных блоков:

─ внутренней шины;

─ регистров общего назначения;

─ арифметико-логического устройства (АЛУ);

─ буфера шины адреса;

─ буфера шины данных;

─ устройства управления и синхронизации;

─ регистра команд.

Для связи между собой структурных блоков микропроцессора предназначена внутренняя шина.

Регистры общего назначения (РОН) содержат регистр адреса; программный счетчик; указатель стека; оперативные парные регистры: W Z; D C. D E, H L,мультиплексор.

В состав АЛУ входят буфер и аккумулятор для промежуточного хранения исходной цифровой информации; арифметико-логическое устройство; регистр признаков.

Регистр адреса служит для промежуточного хранения адреса обращения микропроцессора к конкретному структурному блоку системы. Этот адрес в регистр заносится перед посылкой его в шину адреса.

Программный счетчик служит для формирования адреса обращения к ячейкам памяти, в которых хранятся команды программы управления микропроцессорной системы. При выполнении очередной команды алгоритма управления объектом содержание счетчика увеличивается автоматически на единицу, если этот алгоритм линейный.

Стеком называют часть оперативной памяти, в ячейки которой последовательно записывают оперативную информацию. При записи этой информации указатель стека автоматически увеличивается на число заполненных при записи ячеек памяти. И наоборот, при считывании информации из стека его ячейки последовательно очищаются, а указатель стека уменьшается на число таких очищенных ячеек.

Кроме того, для хранения оперативной информации служат парные оперативные регистры общего назначения W и Z, B и C, D и E, H и L, обращение к которым осуществляется через мультиплексор. Часть этих регистров предназначена для хранения адресной части команд, в то время как их исполнительная часть хранится в регистре команд.

Назначение каждого из элементов микропроцессора приведем в процессе описания принципа его работы.

Принцип работы микропроцессора при обработке команд Перед началом работы микропроцессора в его программный счетчик автоматически заносится адрес первой команды программы управления работой микропроцессорной системы.

Этот адрес через регистр адреса передается в буфер шины адреса, из которого он затем выставляется на шине адреса. Одновременно на шине управления устройством управления и синхронизации выставляется

команда «Чтение», при исполнении которой из ПЗУ или ОЗУ побайтно в шину данных пересылаются составные части этой команды.

Команда управления микропроцессорной системой состоит из двух частей: признака действия команды, который пересылается в регистр команд, и двух адресов этой команды, которые пересылаются в программно недоступные регистры общего назначения W и Z. В регистре команд исполнительная часть команды управления делится на ряд мелких команд, которые называются машинными циклами. Каждая из команд может содержать от 4 до 10 машинных циклов. Последовательностью машинных циклов производится непосредственное управление работой микропроцессора. Регистр команд через устройство управления и синхронизации формирует внешние команды, которые направляются в шину управления. После исполнения очередной команды при линейном алгоритме программный счетчик автоматически увеличивает свое содержание на единицу, в результате чего происходит естественный переход к следующей команде программы управления микропроцессором. Если обрабатываемая команда является командой ветвления, то в регистр адреса пересылается содержание регистра общего назначения W, в котором находится адрес перехода к следующей команде.

Принцип работы микропроцессора при обработке цифровых сигналов Обработка цифровых сигналов производится в арифметико-логическом устройстве микропроцессора. Это устройство может обрабатывать одновременно два цифровых сигнала. Для этой цели по командам машинного цикла последовательно сначала из регистра W, а потом из регистра Z в буфер шины адреса направляются адреса хранения этих сигналов. Одновременно на шине управления устройством управления и синхронизации микропроцессора выставляется команда «Чтение», по которой через шину данных в буфер шины данных пересылается сначала один, а затем и другой цифровой сигнал. Затем эти сигналы из буфера так же последовательно пересылаются для промежуточного хранения вначале в буфер АЛУ, а затем в его аккумулятор. В АЛУ методом арифметического сложения и логических сдвигов по командам машинных циклов производится совместная обработка этих сигналов. Цифровой результат обработки сигналов направляется для хранения в аккумулятор, при этом в регистре признаков устанавливаются признаки (или флаги) этого результата. К числу этих признаков (флагов) можно отнести: положительность или отрицательность цифрового результата, его четность или нечетность, равенство или неравенство его нулю и т. д. Эти признаки (флаги) используются командами ветвления для организации условия ветвления алгоритма. Для того чтобы полученный результат не был потерян при выполнении последующей команды, его необходимо переслать из аккумулятора в один из регистров общего назначения или в ячейку памяти ОЗУ.