- •Отличительные особенности микроконтроллеров at91 на базе ядра arm® Thumb®

- •. Описание

- •2. Краткий обзор конфигурации семейства at91sam7s

- •3. Структурная схема

- •4. Назначение выводов

- •5. Назначение внешних выводов для различных корпусов

- •6. Питание

- •7. Порты ввода-вывода

- •8. Архитектура ядра процессора

- •9. Память

- •10. Системный контроллер

- •10.1 Организация памяти системного контроллера

- •10.2 Контроллер сброса

- •10.3 Тактовый генератор

- •10.4 Контроллер управления потребляемой мощностью

- •Расширенный контроллер прерываний и модуль внутрисхемной отладки

- •Таймеры, контроллер портов ввода-вывода и контроллер режимов стабилизатора напряжения питания

- •11. Периферийные модули

- •11.1 Организация памяти периферийных модулей

- •11.2 Дополнительные функции портов ввода-вывода

- •11.3 Функции портов pa0…pa31

- •11.4 Идентификаторы периферийных модулей

- •11.5 Последовательный периферийный интерфейс

- •Двухпроводной интерфейс, usart, spi

- •11.9 Таймер-счетчик (tc)

- •Шим контроллер, usb, ацп

- •12. Обзор процессора arm7tdmi

- •13. Отличительные способности средств отладки и тестирования Описание и структурная схема

- •13.3 Примеры применения

- •13.4 Описание выводов для отладки и тестирования

- •13.5 Функциональное описание

- •14. Контроллер сброса (rstc) Обзор и структурная схема

- •14.3 Функциональное описание

- •14.4 Пользовательский интерфейс контроллера сброса

- •15. Таймер реального времени (rtt)

- •15.3 Функциональное описание

- •15.4 Пользовательский интерфейс таймера реально времени

- •16. Интервальный таймер (pit)

- •16.3 Функциональное описание

- •16.4 Пользовательский интерфейс интервального таймера

- •17. Сторожевой таймер (wdt)

- •17.3 Функциональное описание

- •17.4 Пользовательский интерфейс сторожевого таймера

- •18. Контроллер режимов стабилизатора напряжения (vreg)

- •19. Контроллер памяти (mc)

- •19.3 Функциональное описание

- •19.4 Пользовательский интерфейс контроллера памяти

- •20. Контроллер встроенной флэш-памяти (efc)

- •20.3 Пользовательский интерфейс контроллера встроенной флэш-памяти

- •21. Интерфейс программирования флэш-памяти (ffpi)

- •21.3. Последовательный интерфейс программирования флэш-памяти

- •22. Стартовый загрузчик at91sam7 (бут загрузчик)

- •23. Контроллер пдп (dma) периферийных модулей

- •23.3 Функционирование контроллера dma

- •23.4 Контроллер пдп (pdc). Интерфейс работы

- •24. Расширенный Контроллер Прерываний (aic)

- •24.6 Особенности контроллеров at91 серии

- •24.7 Функциональное описание

- •24.8 Контроллер прерываний aic. Интерфейс пользователя

- •25. Тактовый генератор

- •26. Контроллер управления потребляемой мощности (pmc)

- •26.5 Контроллер тактовых сигналов периферийных модулей (Peripheral Clock Controller)

- •26.6 Контроллер программно управляемых внешних тактовых сигнала

- •6.7 Последовательность программирования

- •26.8 Переключение тактовых сигналов

- •26.9 Регистры контроллера управления потребляемой мощности

- •27. Модуль внутрисхемной отладки (dbgu)

- •27.4. Работа уапп (uart)

- •27.5 Пользовательский интерфейс модуля внутрисхемной отладки

- •28. Контроллер параллельного ввода-вывода

- •8.5 Функциональное описание

- •28.7. Пользовательский интерфейс контроллера параллельного ввода - вывода

- •9. Последовательный периферийный интерфейс (spi)

- •29.6 Функциональное описание

- •29.7 Пользовательский интерфейс последовательно - параллельного интерфейса (spi)

- •30. Двухпроводной интерфейс

- •30.5 Функциональное описание

- •30.6. Пользовательский интерфейс двухпроводного интерфейса

- •33. Таймер-счетчик (тс)

- •33.5 Функциональное описание

- •33.6 Пользовательский интерфейс таймера-счетчика (тс)

- •34. Контроллер широтно-импульсной модуляции (шим)

- •34.5 Функциональное описание

- •34.6 Пользовательский интерфейс шим-контроллера (pwm)

- •35. Порт usb-устройства (udp)

- •35.5. Функциональное описание

- •35.5.2.8 Транзакция "Статус"

- •35.6. Пользовательский интерфейс usb порта (udp)

- •36. Аналогово-цифровой преобразователь (ацп)

- •36.5 Функциональное описание

- •36.6 Пользовательский интерфейс ацп

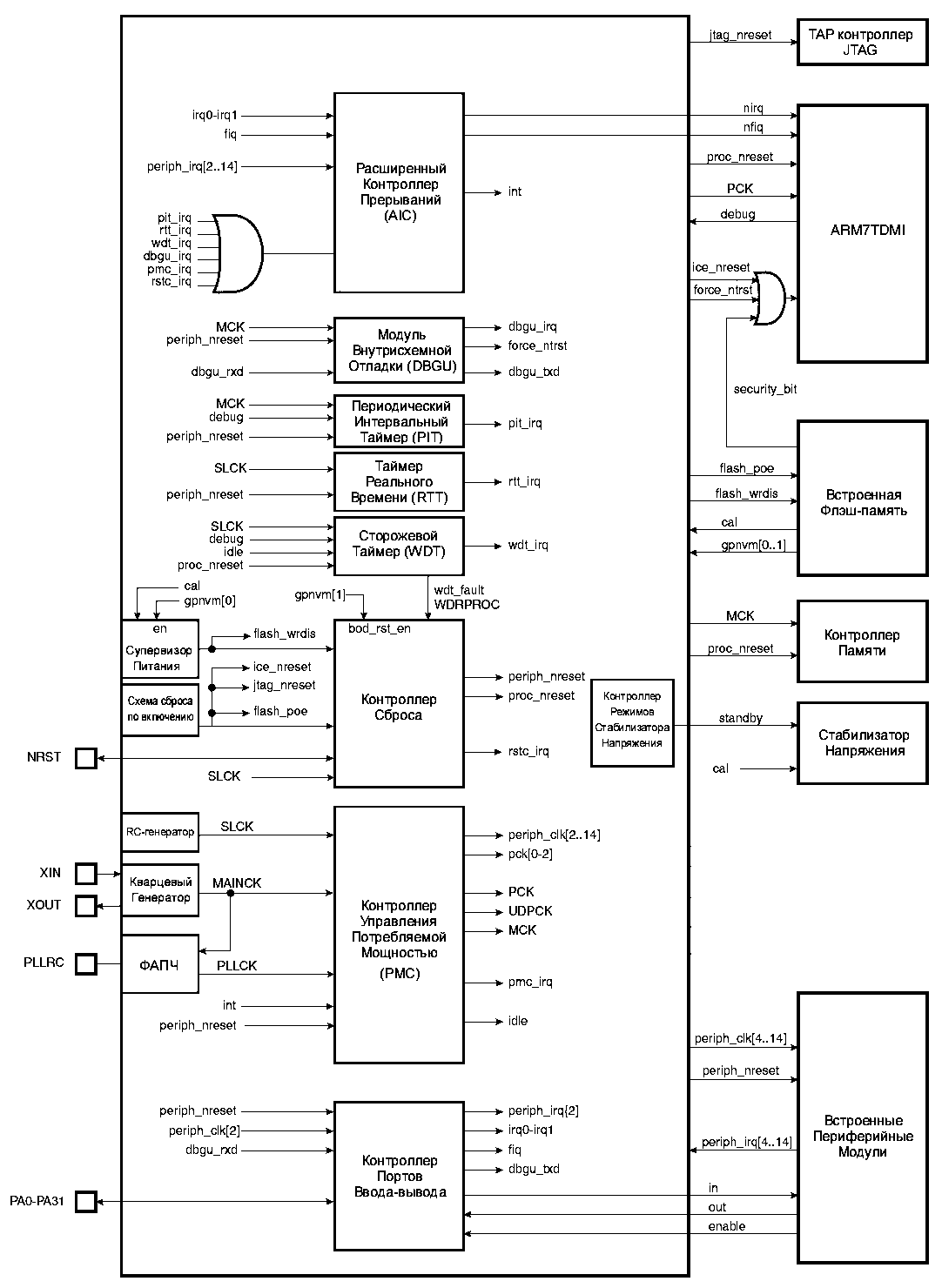

10. Системный контроллер

Системный контроллер управляет всеми основными модулями микроконтроллера: прерывания, тактовые сигналы, таймеры, питание, внутрисхемная отладка и сброс.

Рисунок

10-1. Структурная схема системного

контроллера (AT91SAM7S256/128/64/321)

Рисунок

10-1. Структурная схема системного

контроллера (AT91SAM7S256/128/64/321)

Рисунок

10-2. Структурная схема системного

контроллера (AT91SAM7S32)

Рисунок

10-2. Структурная схема системного

контроллера (AT91SAM7S32)

10.1 Организация памяти системного контроллера

Все регистры системного контроллера размещены в старших 4 Кбайт всего доступного адресного пространства, по адресам 0xFFFFF000…0xFFFFFFFF.

На рисунке 10-3 приведено карта распределения памяти регистров системного контроллера. Необходимо отметить, что регистры пользовательского интерфейса контроллера памяти размещены в этой же области памяти.

Рисунок

10-3. Распределение памяти системного

контроллера

Рисунок

10-3. Распределение памяти системного

контроллера

10.2 Контроллер сброса

Контроллер Сброса основан на Схеме Сброса при Подаче Питания и Супервизоре питания. Контроллер Сброса позволяет зафиксировать источник последнего произошедшего сброса: сброс по включению питания, программный сброс, внешний аппаратный сброс, сброс от сторожевого таймера, сброс от супервизора напряжения питания. В дополнение ко всему, Контроллер Сброса управляет разрешением и запретом сброса от всех внутренних источников сброса и выводом NRST с открытым стоком, формируя на нем импульс низкого логического уровня определенной длительности.

Примечание: если при возникновении провалов напряжения питания вывод NRST используется для формирования импульса сброса для внешних устройств, то для этого необходимо разрешить работу детектора провалов питающего напряжения.

10.2.1 Супервизор напряжения питания и схема сброса при подаче питания

В каждом микроконтроллере из семейства AT91SAM7S встроен супервизор питания и схема сброса при подаче питания. Оба модули получают питание от вывода VDDCORE и одновременно контролируют напряжение на нем. Кроме того, сигналы от обоих модулей управляют работой контроллера флэш-памяти, тем самым, предотвращая сбои и ошибки в работе флэш-памяти при сбоях в питании.

Схема сброса при подаче питания имеет порог 1,5В (это значение калибруется на этапе изготовления кристалла). Выход этого модуля остается на низком логическом уровне до тех пор, пока напряжение VDDCORE не превысит порог 1,5В. С помощью этого же сигнала производится полная инициализация всего устройства.

Супервизор питания следит за напряжением VDDCORE, постоянно сравнивая его значение с определенным уровнем. Это позволяет значительно уменьшить вероятность сбоев в работе программы микроконтроллера, тем самым, увеличивая надежность устройства в целом.

Провалы напряжения питания контролируются только на выводе VDDCORE, так как ни снижение напряжения на выводе VDDFLASH, ни снижение напряжения на других выводах питания микроконтроллера не может нарушить содержимое флэш-памяти.

В супервизор питания встроен аналоговый компаратор с гистерезисом hyst, равным примерно 50 мВ. На один вывод компаратора подано напряжение Vbot, а на другой - напряжение с вывода VDDCORE. Уровень напряжения Vbot составляет 1,68В и откалиброван с точностью +2% на этапе производства кристалла.

Если напряжение на этом выводе упадет ниже Vbot? = Vbot-hyst/2 и на время не менее 1 мкс, то на выходе супервизора возникнет сигнал сброса. Если напряжение на выводе VDDCORE возрастет выше уровня Vbot+ = Vbot+hyst/2, то выход Супервизора вернется в обычное состояние.

Супервизора питания потребляет ток не более 20 мкА (в статике). Однако, для повышения экономичности приложения супервизора может быть отключен (с помощью GPNVM бита 0), при этом его ток потребления снизится до уровня 1 мкА.