- •Отличительные особенности микроконтроллеров at91 на базе ядра arm® Thumb®

- •. Описание

- •2. Краткий обзор конфигурации семейства at91sam7s

- •3. Структурная схема

- •4. Назначение выводов

- •5. Назначение внешних выводов для различных корпусов

- •6. Питание

- •7. Порты ввода-вывода

- •8. Архитектура ядра процессора

- •9. Память

- •10. Системный контроллер

- •10.1 Организация памяти системного контроллера

- •10.2 Контроллер сброса

- •10.3 Тактовый генератор

- •10.4 Контроллер управления потребляемой мощностью

- •Расширенный контроллер прерываний и модуль внутрисхемной отладки

- •Таймеры, контроллер портов ввода-вывода и контроллер режимов стабилизатора напряжения питания

- •11. Периферийные модули

- •11.1 Организация памяти периферийных модулей

- •11.2 Дополнительные функции портов ввода-вывода

- •11.3 Функции портов pa0…pa31

- •11.4 Идентификаторы периферийных модулей

- •11.5 Последовательный периферийный интерфейс

- •Двухпроводной интерфейс, usart, spi

- •11.9 Таймер-счетчик (tc)

- •Шим контроллер, usb, ацп

- •12. Обзор процессора arm7tdmi

- •13. Отличительные способности средств отладки и тестирования Описание и структурная схема

- •13.3 Примеры применения

- •13.4 Описание выводов для отладки и тестирования

- •13.5 Функциональное описание

- •14. Контроллер сброса (rstc) Обзор и структурная схема

- •14.3 Функциональное описание

- •14.4 Пользовательский интерфейс контроллера сброса

- •15. Таймер реального времени (rtt)

- •15.3 Функциональное описание

- •15.4 Пользовательский интерфейс таймера реально времени

- •16. Интервальный таймер (pit)

- •16.3 Функциональное описание

- •16.4 Пользовательский интерфейс интервального таймера

- •17. Сторожевой таймер (wdt)

- •17.3 Функциональное описание

- •17.4 Пользовательский интерфейс сторожевого таймера

- •18. Контроллер режимов стабилизатора напряжения (vreg)

- •19. Контроллер памяти (mc)

- •19.3 Функциональное описание

- •19.4 Пользовательский интерфейс контроллера памяти

- •20. Контроллер встроенной флэш-памяти (efc)

- •20.3 Пользовательский интерфейс контроллера встроенной флэш-памяти

- •21. Интерфейс программирования флэш-памяти (ffpi)

- •21.3. Последовательный интерфейс программирования флэш-памяти

- •22. Стартовый загрузчик at91sam7 (бут загрузчик)

- •23. Контроллер пдп (dma) периферийных модулей

- •23.3 Функционирование контроллера dma

- •23.4 Контроллер пдп (pdc). Интерфейс работы

- •24. Расширенный Контроллер Прерываний (aic)

- •24.6 Особенности контроллеров at91 серии

- •24.7 Функциональное описание

- •24.8 Контроллер прерываний aic. Интерфейс пользователя

- •25. Тактовый генератор

- •26. Контроллер управления потребляемой мощности (pmc)

- •26.5 Контроллер тактовых сигналов периферийных модулей (Peripheral Clock Controller)

- •26.6 Контроллер программно управляемых внешних тактовых сигнала

- •6.7 Последовательность программирования

- •26.8 Переключение тактовых сигналов

- •26.9 Регистры контроллера управления потребляемой мощности

- •27. Модуль внутрисхемной отладки (dbgu)

- •27.4. Работа уапп (uart)

- •27.5 Пользовательский интерфейс модуля внутрисхемной отладки

- •28. Контроллер параллельного ввода-вывода

- •8.5 Функциональное описание

- •28.7. Пользовательский интерфейс контроллера параллельного ввода - вывода

- •9. Последовательный периферийный интерфейс (spi)

- •29.6 Функциональное описание

- •29.7 Пользовательский интерфейс последовательно - параллельного интерфейса (spi)

- •30. Двухпроводной интерфейс

- •30.5 Функциональное описание

- •30.6. Пользовательский интерфейс двухпроводного интерфейса

- •33. Таймер-счетчик (тс)

- •33.5 Функциональное описание

- •33.6 Пользовательский интерфейс таймера-счетчика (тс)

- •34. Контроллер широтно-импульсной модуляции (шим)

- •34.5 Функциональное описание

- •34.6 Пользовательский интерфейс шим-контроллера (pwm)

- •35. Порт usb-устройства (udp)

- •35.5. Функциональное описание

- •35.5.2.8 Транзакция "Статус"

- •35.6. Пользовательский интерфейс usb порта (udp)

- •36. Аналогово-цифровой преобразователь (ацп)

- •36.5 Функциональное описание

- •36.6 Пользовательский интерфейс ацп

34. Контроллер широтно-импульсной модуляции (шим)

34.1 Обзор

Модуль ШИМ независимо управляет несколькими каналами. Каждый из каналов генерирует прямоугольные импульсы на одном своем выходе. Параметры прямоугольных импульсов, такие как период, заполнение импульсов и полярность конфигурируются через пользовательский интерфейс. Каждый канал использует один из сигналов синхронизации, генерируемых тактовым генератором (какой именно сигнал выбирается пользователем). Сигналы синхронизации, формируемые тактовым генератором, получаются в результате деления сигнала главной синхронизации модуля ШИМ.

Доступ к модулю ШИМ выполнен через регистры, связанные с шиной APB.

В целях генерации неперекрывающихся прямоугольных импульсов предусмотрена возможность синхронизации работы каналов. Все каналы интегрируют систему двойной буферизации, которая позволяет избежать генерацию нежелательных импульсов при изменении периода или заполнения импульсов ШИМ-сигнала.

34.2 Структурная схема

Рисунок

34.1. Структурная схема контроллера

широтно-импульсной модуляции

Рисунок

34.1. Структурная схема контроллера

широтно-импульсной модуляции

34.3 Порты ввода-вывода, мультиплексированные с ШИМ контроллером

Каждый канал генерирует импульсы на одной внешней линии ввода-вывода.

Таблица 34.1. Описание линий ввода-вывода

|

Наименование |

Описание |

Тип |

|

PWMx |

Выход ШИМ канала х |

Выход |

34.4 Различия в реализации ШИМ контроллера в семействе AT91SAM7S

34.4.1 Линии ввода-вывода

Выводы, используемые для подключения ШИМ, могут быть мультиплексированы с портами ввода-вывода. Первоначально программист должен запрограммировать контроллер порта ввода-вывода, чтобы назначить желаемых ШИМ-выводам их периферийную функцию. Если линии ввода-вывода ШИМ не используются в приложении, то они могут использоваться в других целях контроллером ПВВ.

Пользователь может сам решать, какое количество выходов активизировать, а какое нет. Если в приложении требуется только четыре канала, то только четыре линии ввода-вывода могут использоваться в качестве ШИМ-выходов.

34.4.2 Управление потребляемой мощностью

Синхронизация ШИМ реализована не на постоянной основе. Перед использованием модуля ШИМ программист должен вначале разрешить синхронизацию ШИМ в контроллере управления потребляемой мощностью (PMC). Однако, если в приложении не требуется работа модуля ШИМ, то его синхронизация может быть остановлена, когда в ней нет необходимости и может быть перезапущена позже. В этом случае, модуль восстановит работу из того же состояния, в котором он был оставлен отключенным.

Для конфигурирования модуля ШИМ не требуется включение его синхронизации.

34.4.3 Источники прерываний

Линия прерывания модуля ШИМ подключена к одному из внутренних источников расширенного контроллера прерываний. Для использования прерывания ШИМ необходимо вначале запрограммировать контроллер прерываний AIC. Обратите внимание, что не рекомендуется использовать линию прерываний ШИМ в режиме, чувствительном к фронтам.

34.5 Функциональное описание

Модуль ШИМ состоит из тактового генератора и 4 каналов.

Тактовый генератор синхронизируется системным сигналом MCK и формирует 13 сигналов синхронизации.

Каждый канал может использовать один из выходов тактового генератора (выбирается пользователем).

Каждый канал генерирует выходной сигнал, параметры которого задаются раздельно для каждого канала через регистры интерфейса пользователя.

34.5.1 Тактовый генератор модуля ШИМ

Рисунок

34.2. Структурная схема тактового генератора

Рисунок

34.2. Структурная схема тактового генератора

Замечание: перед использованием модуля ШИМ программист должен вначале разрешить работу его синхронизации в контроллере управления потребляемой мощностью (PMC).

Внутренние сигналы синхронизации, используемые всеми каналами, формируются путем деления частоты сигнала главной синхронизации модуля ШИМ - MCK. Предусмотрена возможность раздельного выбора одного из выходов тактового генератора для каждого канала.

Тактовый генератор состоит из трех блоков:

счетчик по модулю n, который формирует 11 сигналов синхронизации: FMCK, FMCK/2, FMCK/4, FMCK/8, FMCK/16, FMCK/32, FMCK/64, FMCK/128, FMCK/256, FMCK/512, FMCK/1024

два линейных делителя (1, 1/2, 1/3, ... 1/255), которые формируют два отдельных сигнала синхронизации: clkA и clkB

Каждый линейный делитель может раздельно подключаться к одному из выходов счетчика по модулю n. Выбор сигнала, который будет подвергаться делению, осуществляется с помощью параметра PREA (PREB) в регистре режима ШИМ (PWM_MR). Коэффициент деления и результирующая частота сигналов синхронизации clkA (clkB) зависит от параметра DIVA (DIVB) в регистре режима ШИМ (PWM_MR).

После сброса контроллера ШИМ значения DIVA (DIVB) и PREA (PREB) в регистре режима ШИМ обнуляются. Это означает, что сразу после сброса синхронизация clkA (clkB) находится в отключенном состоянии.

Во время сброса все сигналы синхронизации, формируемые счетчиком по модулю n, отключаются, кроме "clk". Данная ситуация также повторяется при отключении главной синхронизации модуля ШИМ через контроллер управления потребляемой мощностью.

34.5.2 Канал ШИМ

34.5.2.1 Структурная схема

Рисунок

34.3. Структурная схема канала ШИМ

Рисунок

34.3. Структурная схема канала ШИМ

Каждый из четырех каналов состоит из трех блоков:

Селектор синхронизации, который выбирает один из сигналов синхронизации, формируемых тактовым генератором (см. 34.5.1 "Тактовый генератор модуля ШИМ ").

Внутренний счетчик, который тактируется с выхода селектора синхронизации. Данный внутренний счетчик инкрементируется или декрементируется в соответствии с конфигурацией канала и командами компараторов. Внутренний счетчик является 16-разрядным.

Компаратор, используемый для генерации команд в зависимости от значения внутреннего счетчика. От настройки компаратора также зависит форма сигнала на выходе PWMx.

34.5.2.2 Настройка формы выходного сигнала

К свойствам выходного сигнала относятся:

выбор внутренней синхронизации. Внутренний канал счетчика синхронизируется одним из сигналов тактового генератора, описанного в предыдущем разделе. Данный параметр канала задается в поле CPRE регистра PWM_CMRx. После сброса данное поле равно 0.

период следования импульсов. Данный параметр канала задается в поле CPRD регистра PWM_CPRDx.

- если выбрана генерация импульсов с левым выравниванием, то период следования импульсов зависит от источника синхронизации счетчика и вычисляется по формуле:

(X * CPRD)/MCK, если используется сигнал главной синхронизации MCK, поделенный предделителем на величину X (1, 2, 4, 8, 16, 32, 64, 128, 256, 512 или 1024).

(CPRD * DIVA)/MCK или (CPRD * DIVB)/MCK, если главная синхронизация поделена одним из делителей DIVA или DIVB.

- если выбрана генерация импульсов с выравниванием по центру, то период следования импульсов зависит источника синхронизации счетчика и вычисляется следующим образом:

(2* X * CPRD)/MCK, если используется сигнал главной синхронизации MCK, поделенный предделителем на величину X (1, 2, 4, 8, 16, 32, 64, 128, 256, 512 или 1024).

(2 * CPRD * DIVA)/MCK или (2 * CPRD * DIVB)/MCK , если главная синхронизация поделена одним из делителей DIVA или DIVB.

коэффициент заполнения импульсов. Данный параметр канала задается в поле CDTY регистра PWM_CDTYx. Если выбрана генерация импульсов с левым выравниванием, то:

Кзап.имп.=(ПЕРИОД-1/Fсинхр.канала_х * CDTY) / ПЕРИОД

Кзап.имп.=( ½ ПЕРИОД-1/Fсинхр.канала_х * CDTY) / ½ПЕРИОД

полярность импульсов. В начале периода генерируемый сигнал может иметь высокий или низкий уровень. Данное свойство задается в поле CPOL регистра PWM_CMRx. По умолчанию импульсы генерируются с низкого уровня.

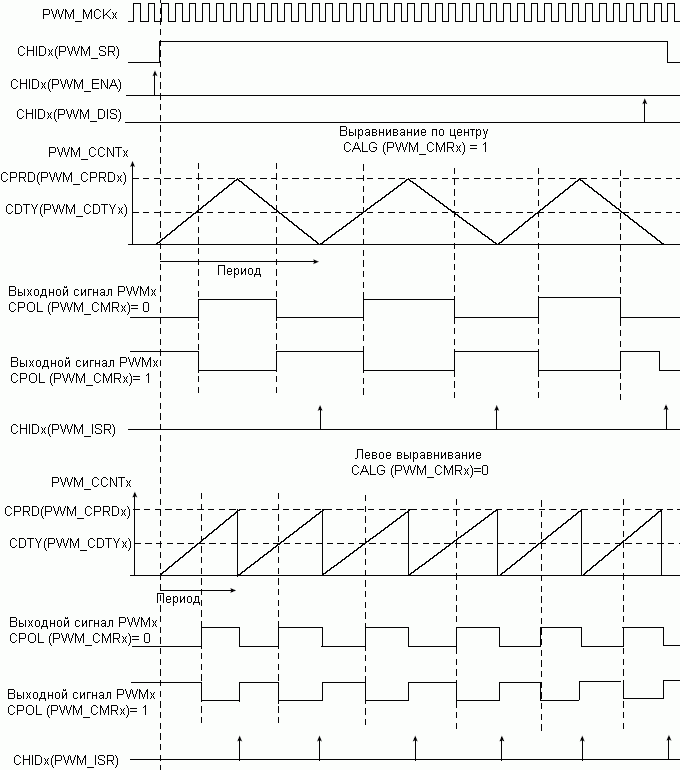

выравнивание импульсов. Прямоугольные импульсы могут генерироваться с левым выравниванием или выравниванием по центру. Выравнивание по центру позволяет генерировать неперекрывающиеся импульсы. Данное свойство задается в поле CALG регистра PWM_CMRx. По умолчанию принимается левое выравнивание.

Рисунок

34.4. Генерация неперекрывающихся импульсов

с выравниванием по центру1

Рисунок

34.4. Генерация неперекрывающихся импульсов

с выравниванием по центру1

Прим.: см. рисунок 34.5, где представлено более детальное описание импульсов с выравниванием по центру.

При выборе выравнивания по центру внутренний канал счетчика инкрементируется до CPRD, а затем декрементируется до 0. На этом период заканчивается. При выборе левого выравнивания внутренний канал счетчика увеличивается до CPRD и сбрасывается. Этим заканчивается период. Таким образом, одно и тоже значение CPRD, которое задает период для канала с выравниванием по центру, будет соответствовать двум периодам в канале с левым выравниванием.

Выходной сигнал имеет непрерывный низкий уровень, если:

CDTY = CPRD и CPOL = 0

CDTY = 0 и CPOL = 1

Выходной сигнал имеет непрерывно высокий уровень (после разрешения работы канала), если:

CDTY = 0 и CPOL = 0

CDTY = CPRD и CPOL = 1

Полярность импульсов необходимо установить до разрешения работы канала. Это приводит к незамедлительному изменению выходного уровня канала. Изменения полярности канала игнорируется после разрешения его работы.

Рисунок

34.5. Свойства генерируемых импульсов

Рисунок

34.5. Свойства генерируемых импульсов

34.5.3 Работа ШИМ-контроллера

34.5.3.1 Инициализация

Перед разрешением работы выходного канала необходимо выполнить его программную настройку:

конфигурация тактового генератора, если необходимо использование DIVA и DIVB

выбор синхронизации для каждого канала (поле CPRE в регистре PWM_CMRx)

конфигурация выравнивания импульсов в каждом канале (поле CALG в регистре PWM_CMRx)

конфигурация периода для каждого канала (CPRD в регистре PWM_CPRDx). Запись в регистр PWM_CPRDx возможна, только если канал отключен. После настройки канала пользователь может использовать регистр PWM_CUPDx для обновления PWM_CPRDx в соответствии с описанием приведенным ниже.

конфигурация заполнения импульсов для каждого канала (CDTY в регистре PWM_CDTYx). Запись в регистр PWM_CDTYx возможна только при отключенном канале. После настройки канала пользователь может использовать регистр PWM_CUPDx для обновления PWM_CDTYx в соответствии с описанием, приведенным ниже.

конфигурация полярности импульсов для каждого канала (CPOL в регистре PWM_CMRx)

разрешение прерываний (запись CHIDx в регистре PWM_IER)

разрешение работы канала ШИМ (запись CHIDx в регистре PWM_ENA). Синхронизировать работу каналов можно путем одновременной записи нескольких бит CHIDx в регистре PWM_ENA.

в такой ситуации все каналы могут иметь одинаковые настройки селектора синхронизации и период следования импульсов.

34.5.3.2 Критерий выбор источника синхронизации

Широкий выбор источников синхронизации может усложнить их выбор. Соотношение между значением в регистре периода (PWM_CPRDx) и регистром заполнения импульсов (PWM_CDTYx) может облегчить выбор. Число, записанное в регистр периода, определяет точность ШИМ. Разрешающая способность заполнения импульсов не может быть меньше 1/PWM_CPRDx. Более высокие значения PWM_CPRDx увеличивают точность ШИМ. Например, если пользователь запишет число 15 (десятичное) в PWM_CPRDx, то в дальнейшем в регистр PWM_CDTYx возможна только запись значений между 1 и 14. В результате, разрешающая способность заполнения импульсов не может быть меньше 1/15 от периода ШИМ.

34.5.3.3 Изменение заполнения импульсов или периода

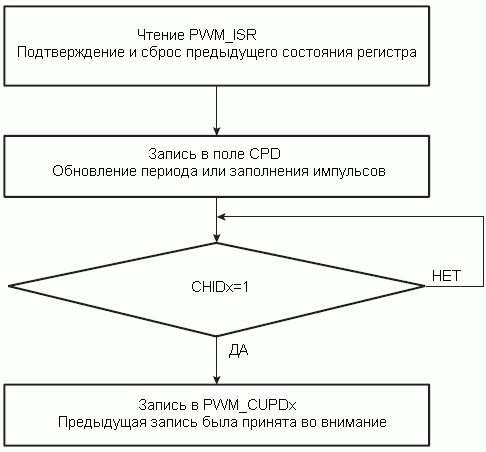

Регулировать форму выходного сигнала можно путем изменения заполнения импульсов или периода. У регистров PWM_CPRDx и PWM_CDTYx предусмотрен механизм двойной буферизации, который позволяет избежать сбоев в генерации импульсов, когда разрешена работа каналов и выполнено изменение параметров генерируемых импульсов. Пользователь может записать новое значение периода или заполнения импульсов в регистр обновления (PWM_CUPDx). Данный регистр запоминает новое значение до завершения текущего цикла и обновляет значение для следующего цикла. В зависимости от значения в поле CPD регистра PWM_CMRx значение, хранящееся в PWM_CUPDx, обновляет PWM_CPRDx или PWM_CDTYx.

Рисунок

34.6. Синхронизированное обновление

периода/заполнения импульсов

Рисунок

34.6. Синхронизированное обновление

периода/заполнения импульсов

В целях предотвращения перезаписи PWM_CUPDx программой пользователь может использовать флаги статуса. Возможно два метода. При использовании каждого из них необходимо разрешить соответствующее прерывание в PWM_IER на уровне ШИМ-контроллера.

Первый метод (метод опроса) заключается в считывании бит статуса в регистре PWM_ISR, соответствующих активным каналам (см. рисунок 34.7).

Второй метод основан на использовании процедуры обработки прерывания, связанного с ШИМ-каналом.

Прим.: при считывании регистра PWM_ISR флаги CHIDx автоматически сбрасываются.

Рисунок

34.7. Метод опроса

Рисунок

34.7. Метод опроса

Прим.: полярность и выравнивание может изменяться только при отключенном канале.

34.5.3.4 Прерывания

В зависимости от маски прерывания в регистре PWM_IMR прерывание генерируется в конце периода соответствующего канала. Прерывание остается активным до считывания регистра PWM_ISR. Прерывание канала активизируется путем установки соответствующего бита в регистре PWM_IER. Для отключения прерывания канала необходимо установить соответствующий бит в регистре PWM_IDR.