- •Отличительные особенности микроконтроллеров at91 на базе ядра arm® Thumb®

- •. Описание

- •2. Краткий обзор конфигурации семейства at91sam7s

- •3. Структурная схема

- •4. Назначение выводов

- •5. Назначение внешних выводов для различных корпусов

- •6. Питание

- •7. Порты ввода-вывода

- •8. Архитектура ядра процессора

- •9. Память

- •10. Системный контроллер

- •10.1 Организация памяти системного контроллера

- •10.2 Контроллер сброса

- •10.3 Тактовый генератор

- •10.4 Контроллер управления потребляемой мощностью

- •Расширенный контроллер прерываний и модуль внутрисхемной отладки

- •Таймеры, контроллер портов ввода-вывода и контроллер режимов стабилизатора напряжения питания

- •11. Периферийные модули

- •11.1 Организация памяти периферийных модулей

- •11.2 Дополнительные функции портов ввода-вывода

- •11.3 Функции портов pa0…pa31

- •11.4 Идентификаторы периферийных модулей

- •11.5 Последовательный периферийный интерфейс

- •Двухпроводной интерфейс, usart, spi

- •11.9 Таймер-счетчик (tc)

- •Шим контроллер, usb, ацп

- •12. Обзор процессора arm7tdmi

- •13. Отличительные способности средств отладки и тестирования Описание и структурная схема

- •13.3 Примеры применения

- •13.4 Описание выводов для отладки и тестирования

- •13.5 Функциональное описание

- •14. Контроллер сброса (rstc) Обзор и структурная схема

- •14.3 Функциональное описание

- •14.4 Пользовательский интерфейс контроллера сброса

- •15. Таймер реального времени (rtt)

- •15.3 Функциональное описание

- •15.4 Пользовательский интерфейс таймера реально времени

- •16. Интервальный таймер (pit)

- •16.3 Функциональное описание

- •16.4 Пользовательский интерфейс интервального таймера

- •17. Сторожевой таймер (wdt)

- •17.3 Функциональное описание

- •17.4 Пользовательский интерфейс сторожевого таймера

- •18. Контроллер режимов стабилизатора напряжения (vreg)

- •19. Контроллер памяти (mc)

- •19.3 Функциональное описание

- •19.4 Пользовательский интерфейс контроллера памяти

- •20. Контроллер встроенной флэш-памяти (efc)

- •20.3 Пользовательский интерфейс контроллера встроенной флэш-памяти

- •21. Интерфейс программирования флэш-памяти (ffpi)

- •21.3. Последовательный интерфейс программирования флэш-памяти

- •22. Стартовый загрузчик at91sam7 (бут загрузчик)

- •23. Контроллер пдп (dma) периферийных модулей

- •23.3 Функционирование контроллера dma

- •23.4 Контроллер пдп (pdc). Интерфейс работы

- •24. Расширенный Контроллер Прерываний (aic)

- •24.6 Особенности контроллеров at91 серии

- •24.7 Функциональное описание

- •24.8 Контроллер прерываний aic. Интерфейс пользователя

- •25. Тактовый генератор

- •26. Контроллер управления потребляемой мощности (pmc)

- •26.5 Контроллер тактовых сигналов периферийных модулей (Peripheral Clock Controller)

- •26.6 Контроллер программно управляемых внешних тактовых сигнала

- •6.7 Последовательность программирования

- •26.8 Переключение тактовых сигналов

- •26.9 Регистры контроллера управления потребляемой мощности

- •27. Модуль внутрисхемной отладки (dbgu)

- •27.4. Работа уапп (uart)

- •27.5 Пользовательский интерфейс модуля внутрисхемной отладки

- •28. Контроллер параллельного ввода-вывода

- •8.5 Функциональное описание

- •28.7. Пользовательский интерфейс контроллера параллельного ввода - вывода

- •9. Последовательный периферийный интерфейс (spi)

- •29.6 Функциональное описание

- •29.7 Пользовательский интерфейс последовательно - параллельного интерфейса (spi)

- •30. Двухпроводной интерфейс

- •30.5 Функциональное описание

- •30.6. Пользовательский интерфейс двухпроводного интерфейса

- •33. Таймер-счетчик (тс)

- •33.5 Функциональное описание

- •33.6 Пользовательский интерфейс таймера-счетчика (тс)

- •34. Контроллер широтно-импульсной модуляции (шим)

- •34.5 Функциональное описание

- •34.6 Пользовательский интерфейс шим-контроллера (pwm)

- •35. Порт usb-устройства (udp)

- •35.5. Функциональное описание

- •35.5.2.8 Транзакция "Статус"

- •35.6. Пользовательский интерфейс usb порта (udp)

- •36. Аналогово-цифровой преобразователь (ацп)

- •36.5 Функциональное описание

- •36.6 Пользовательский интерфейс ацп

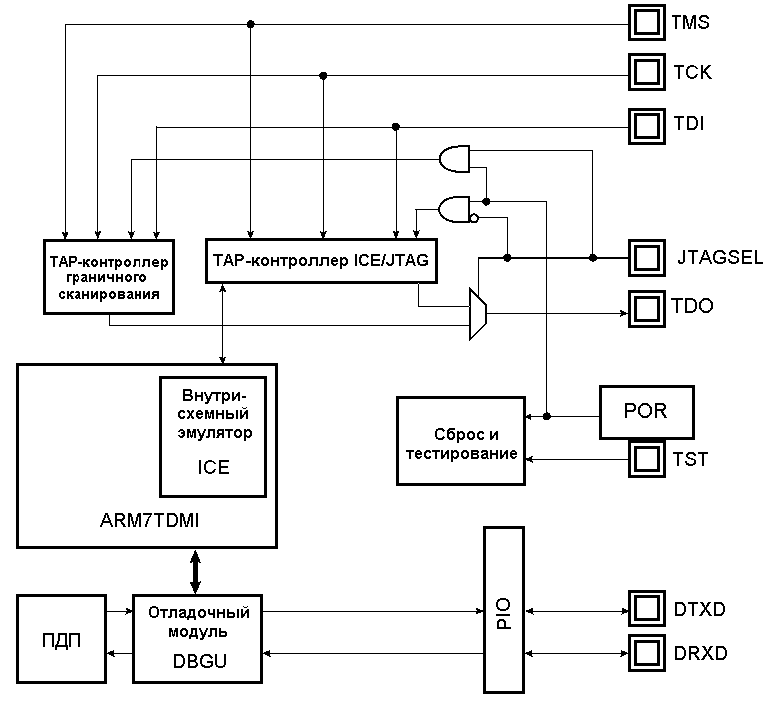

13. Отличительные способности средств отладки и тестирования Описание и структурная схема

13.1 Описание

Отличительной особенностью микроконтроллеров семейства AT91SAM7S является наличие в каждом из них встроенных средств отладки и тестирования. Порт JTAG/ICE (EmbeddedICE) используется для выполнения стандартных функций отладки: загрузка кода и пошаговое выполнение программы. Модуль внутрисхемной отладки (DBGU) предоставляет двухвыводный универсальный асинхронный приемо-передатчик (UART), который может использоваться для загрузки готовой прошивки во внутреннюю статическую память СОЗУ (SRAM). Кроме того, модуль DBGU выполняет обработку прерываний от внутренних сигналов COMMTX и COMMRX, формируемых через отладочный коммуникационный канал (DCC).

Для доступа к внутренним модулям отладки и тестирования предназначены несколько внешних выводов, непосредственно подключаемых к соответствующему оборудованию для связи с компьютером.

13.2 Структурная схема

Рисунок

13-1. Структурная схема модулей отладки

и тестирования

Рисунок

13-1. Структурная схема модулей отладки

и тестирования

13.3 Примеры применения

13.3.1 Среда отладки

На рис. 13-2 изображен пример для реализации полноценной среды отладки. Интерфейс ICE/JTAG используется для выполнения таких стандартных функций отладки, как загрузка кода в память микроконтроллера и пошаговое его выполнение.

Рисунок

13-2. Пример полноценной среды отладки

Рисунок

13-2. Пример полноценной среды отладки

13.3.2 Среда тестирования

На рис. 13-3 изображен пример для реализации полноценной среды тестирования. В этом примере некое тестирующее устройство (тестер) формирует и принимает тестовые сигналы через интерфейс JTAG, позволяющий подключать другие тестируемые кристаллы последовательно в эту же цепь (scan chain).

Рисунок

13-3. Пример полноценной среды тестирования

Рисунок

13-3. Пример полноценной среды тестирования

13.4 Описание выводов для отладки и тестирования

Таблица 13-1. Список выводов для отладки и тестирования

|

Название вывода |

Функциональное назначение |

Тип вывода |

Активный уровень |

|

Сброс/Тестирование | |||

|

NRST |

Сброс микроконтроллера |

Вход / Выход |

Низкий |

|

TST |

Выбор режима тестирования |

Вход |

Высокий |

|

Внутрисхемный эмулятор (ICE) и JTAG | |||

|

TCK |

Тактовый сигнал |

Вход |

|

|

TDI |

Вход последовательных данных |

Вход |

|

|

TDO |

Выход последовательных данных |

Выход |

|

|

TMS |

Выбор режима |

Вход |

|

|

JTAGSEL |

Разрешение работы JTAG |

Вход |

|

|

Модуль внутрисхемной отладки | |||

|

DRXD |

Прием данных для отладки |

Вход |

|

|

DTXD |

Передача данных для отладки |

Выход |

|

13.5 Функциональное описание

13.5.1 Вывод тестирования

Выбор рабочего режима микроконтроллера производится с помощью одного вывода TST, специально предназначенного только для этой цели. Необходимо быть уверенным в том, что на этом выводе всегда присутствует низкий логический уровень (или этот вывод подключен к GND). При высоком уровне напряжения на выводе TST микроконтроллер переходит режим тестирования, используемый на этапе производства его кристалла, поэтому этот режим использоваться не должен.

13.5.2 EmbeddedICE (встроенный внутрисхемный эмулятор)

Работа с внутрисхемным эмулятором EmbeddedICE ядра ARM7TDMI производится через JTAG порт. Через этот же порт производится контроль над ядром ARM7TDMI и его внутренними состояниями.

Процессор ARM7TDMI содержит следующие дополнительные аппаратные возможности и расширенные функции для отладки:

В режиме останова (halt mode) в буфер выполняемых команд возможна вставка команд загрузки/хранения (STM). Это позволяет "на лету" вычитывать содержимое регистров ядра процессора без риска их искажения или порчи, т.е. прозрачно для отлаживаемой программы.

В режиме мониторинга (monitor mode) интерфейс JTAG может использоваться для передачи данных между отладчиком и простой программой-монитором, запускаемой на процессоре ARM7TDMI.

Внутри процессора ARM7TDMI для внутрисхемного эмулятора реализованы три цепочки сканирования (scan chain), управляемых через порт ICE/JTAG и поддерживающих тестирование, отладку и программирование.

Режим внутрисхемной эмуляции активизируется при подаче на вывод JTAGSEL низкого логического уровня. Не существует способа прямого переключения между JTAG и встроенным внутрисхемным эмулятором (Embedded ICE). После переключения состояния вывода JTAGSEL обязательно должен быть выполнен сброс микроконтроллера.

Для получения более подробной информации по встроенному внутрисхемному эмулятору см. документ ARM7TDMI (Rev4) Technical Reference Manual (DDI0210B).

13.5.3 Модуль внутрисхемной отладки

Для подключения к модулю внутрисхемной отладки (DBGU) через встроенный синхронно-асинхронный приемо-передатчик (USART) предназначены два внешних вывода DTXD и DRXD, через которые производится передача и прием отладочной информации. Такое построение позволяет создавать устройства с возможностью отладки кода непосредственно в уже законченном изделии. Кроме того, наличие связи отладочного порта с двумя каналами ПДП позволяет сократить участие процессора в обмене по этому каналу до минимума.

Также модуль DBGU выполняет обработку прерываний от внутренних сигналов COMMTX и COMMRX, формируемых внутрисхемным эмулятором или отладочным коммуникационным каналом (DCC). Более того, модуль внутрисхемной отладки блокирует любой вид доступа к системе через интерфейс внутрисхемного эмулятора ICE.

Для получения информации о версии контроллера и его внутренней конфигурации предназначен специальный регистр модуля отладки - регистр идентификации чипа (Debug Unit Chip ID Register).

Таблица 13-2. Идентификационные номера микроконтроллеров семейства AT91SAM7Sxx

|

Название микроконтроллера |

Идентификационный номер кристалла |

|

AT91SAM7S32 |

0x27080340 |

|

AT91SAM7S321 |

0x27080342 |

|

AT91SAM7S64 |

0x27090540 |

|

AT91SAM7S128 |

0x270A0740 |

|

AT91SAM7S256 |

0x270B0940 |

Для получения более подробной информации о модуле отладки см. главу 27

13.5.4 JTAG граничное сканирование по стандарту IEEE 1149.1

JTAG граничное сканирование по стандарту IEEE 1149.1 позволяет получать доступ независимо от типа размещения выводов отладки и типа корпуса отлаживаемого кристалла.

Режим JTAG граничного сканирования активируется при подаче на внешний вывод JTAGSEL высокого логического уровня. Реализованы функции SAMPLE, EXTEST и BYPASS. В режиме отладки через внутрисхемный эмулятор ICE процессор ARM возвращает внешнему устройству для работы с ICE такой идентификационный номер кристалла, который имеют чипы без встроенного интерфейса JTAG. Это не соответствует стандарту JTAG IEEE 1149.1.

Не существует способа прямого переключения между интерфейсом JTAG и встроенным внутрисхемным эмулятором (Embedded ICE). После переключения состояния вывода JTAGSEL обязательно должен быть выполнен сброс микроконтроллера.

Для тестирования кристалла предназначен специализированный язык описания для работы через граничное сканирование (BSDL).

13.5.4.1 Регистр JTAG граничного сканирования

Регистр граничного сканирования BSR (Boundary-scan Register) содержит 96 бит, которые отвечают за текущее состояние внешних выводов, ассоциированных с сигналами управления.

Каждому выводу входа/выхода AT91SAM7Sxx соответствует 3-битный регистр внутри регистра BSR. Бит OUTPUT (выход) содержит данные, которые записываются непосредственно во внутреннюю защелку порта соответствующего вывода. Бит INPUT (вход) облегчает наблюдение за логическим уровнем непосредственно на выводе. Бит CONTROL (управление) отвечает за направление передачи вывода: на вход или на выход.

Таблица 13-3. Регистр граничного сканирования JTAG для AT91SAM7Sxx

|

Номер бита |

Название вывода |

Тип вывода |

Соотв. ячейки регистра BSR |

|

96 |

PA17/PGMD5/AD0 |

ВХОД/ВЫХОД |

INPUT |

|

95 |

OUTPUT | ||

|

94 |

CONTROL | ||

|

93 |

PA18/PGMD6/AD1 |

ВХОД/ВЫХОД |

INPUT |

|

92 |

OUTPUT | ||

|

91 |

CONTROL | ||

|

90 |

PA21/PGMD9* |

ВХОД/ВЫХОД* |

INPUT(1) |

|

89 |

OUTPUT(1) | ||

|

88 |

CONTROL(1) | ||

|

87 |

PA19/PGMD7/AD2 |

ВХОД/ВЫХОД |

INPUT |

|

86 |

OUTPUT | ||

|

85 |

CONTROL | ||

|

84 |

PA20/PGMD8/AD3 |

ВХОД/ВЫХОД |

INPUT |

|

83 |

OUTPUT | ||

|

82 |

CONTROL | ||

|

81 |

PA16/PGMD4 |

ВХОД/ВЫХОД |

INPUT |

|

80 |

OUTPUT | ||

|

79 |

CONTROL | ||

|

78 |

PA15/PGMD4 |

ВХОД/ВЫХОД |

INPUT |

|

77 |

OUTPUT | ||

|

76 |

CONTROL | ||

|

75 |

PA14/PGMD2 |

ВХОД/ВЫХОД |

INPUT |

|

74 |

OUTPUT | ||

|

73 |

CONTROL | ||

|

72 |

PA13/PGMD1 |

ВХОД/ВЫХОД |

INPUT |

|

71 |

OUTPUT | ||

|

70 |

CONTROL | ||

|

69 |

PA22/PGMD10* |

ВХОД/ВЫХОД* |

INPUT(1) |

|

68 |

OUTPUT(1) | ||

|

67 |

CONTROL(1) | ||

|

66 |

PA23/PGMD11* |

ВХОД/ВЫХОД* |

INPUT(1) |

|

65 |

OUTPUT(1) | ||

|

64 |

CONTROL(1) | ||

|

63 |

PA24/PGMD12* |

ВХОД/ВЫХОД* |

INPUT(1) |

|

62 |

OUTPUT(1) | ||

|

61 |

CONTROL(1) | ||

|

60 |

PA12/PGMD0 |

ВХОД/ВЫХОД |

INPUT |

|

59 |

OUTPUT | ||

|

58 |

CONTROL | ||

|

57 |

PA11/PGMM3 |

ВХОД/ВЫХОД |

INPUT |

|

56 |

OUTPUT | ||

|

55 |

CONTROL | ||

|

54 |

PA10/PGMM2 |

ВХОД/ВЫХОД |

INPUT |

|

53 |

OUTPUT | ||

|

52 |

CONTROL | ||

|

51 |

PA9/PGMM1 |

ВХОД/ВЫХОД |

INPUT |

|

50 |

OUTPUT | ||

|

49 |

CONTROL | ||

|

48 |

PA8/PGMM0 |

ВХОД/ВЫХОД |

INPUT |

|

47 |

OUTPUT | ||

|

46 |

CONTROL | ||

|

45 |

PA7/PGMNVALID |

ВХОД/ВЫХОД |

INPUT |

|

44 |

OUTPUT | ||

|

43 |

CONTROL | ||

|

42 |

PA6/PGMNOE |

ВХОД/ВЫХОД |

INPUT |

|

41 |

OUTPUT | ||

|

40 |

CONTROL | ||

|

39 |

PA5/PGMRDY |

ВХОД/ВЫХОД |

INPUT |

|

38 |

OUTPUT | ||

|

37 |

CONTROL | ||

|

36 |

PA4/PGMNCMD |

ВХОД/ВЫХОД |

INPUT |

|

35 |

OUTPUT | ||

|

34 |

CONTROL | ||

|

33 |

PA25/PGMD13 |

ВХОД/ВЫХОД |

INPUT(1) |

|

32 |

OUTPUT(1) | ||

|

31 |

CONTROL(1) | ||

|

30 |

PA26/PGMD14 |

ВХОД/ВЫХОД |

INPUT(1) |

|

29 |

OUTPUT(1) | ||

|

28 |

CONTROL(1) | ||

|

27 |

PA27/PGMD15 |

ВХОД/ВЫХОД |

INPUT(1) |

|

26 |

OUTPUT(1) | ||

|

25 |

CONTROL(1) | ||

|

24 |

PA28 |

ВХОД/ВЫХОД |

INPUT(1) |

|

23 |

OUTPUT(1) | ||

|

22 |

CONTROL(1) | ||

|

21 |

PA3 |

ВХОД/ВЫХОД |

INPUT |

|

20 |

OUTPUT | ||

|

19 |

CONTROL | ||

|

18 |

PA2 |

ВХОД/ВЫХОД |

INPUT |

|

17 |

OUTPUT | ||

|

16 |

CONTROL | ||

|

15 |

PA1/PGMEN1 |

ВХОД/ВЫХОД |

INPUT |

|

14 |

OUTPUT | ||

|

13 |

CONTROL | ||

|

12 |

PA0/PGMEN0 |

ВХОД/ВЫХОД |

INPUT |

|

11 |

OUTPUT | ||

|

10 |

CONTROL | ||

|

9 |

PA29 |

ВХОД/ВЫХОД |

INPUT(1) |

|

8 |

OUTPUT(1) | ||

|

7 |

CONTROL(1) | ||

|

6 |

PA30 |

ВХОД/ВЫХОД |

INPUT(1) |

|

5 |

OUTPUT(1) | ||

|

4 |

CONTROL(1) | ||

|

3 |

PA31 |

ВХОД/ВЫХОД |

INPUT(1) |

|

2 |

OUTPUT(1) | ||

|

1 |

CONTROL(1) | ||

|

0 |

ERASE |

ВХОД |

INPUT |

Примечание: 1. В AT91SAM7S32 ни с чем не связан.

13.5.5 Идентификационный регистр кода кристалла

Вид доступа: только для чтения

|

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

|

VERSION |

PART NUMBER | ||||||

|

| |||||||

|

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

|

PART NUMBER | |||||||

|

| |||||||

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

PART NUMBER |

MANUFACTURER IDENTITY | ||||||

|

| |||||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

MANUFACTURER IDENTITY |

0 | ||||||

VERSION[31:28]: Номер версии изделия

Установлен в 0x0

PART NUMBER[27:12]: Кодовый номер изделия

|

Тип микроконтроллера |

Кодовый номер |

|

AT91SAM7S32 |

0x5B07 |

|

AT91SAM7S321 |

0x5B12 |

|

AT91SAM7S64 |

0x5B06 |

|

AT91SAM7S128 |

0x5B0A |

|

AT91SAM7S256 |

0x5B09 |

MANUFACTURER IDENTITY[11:1]: Идентификатор производителя

Установлен в 0x01F

BIT[0]: Необходимое требование согласно стандарту IEEE 1149.1

Установлен в 0x1

|

Тип микроконтроллера |

Идентификатор по JTAG |

|

AT91SAM7S32 |

05B0_703F |

|

AT91SAM7S321 |

05B1_203F |

|

AT91SAM7S64 |

05B0_603F |

|

AT91SAM7S128 |

05B0_A03F |

|

AT91SAM7S256 |

05B0_903F |