- •Отличительные особенности микроконтроллеров at91 на базе ядра arm® Thumb®

- •. Описание

- •2. Краткий обзор конфигурации семейства at91sam7s

- •3. Структурная схема

- •4. Назначение выводов

- •5. Назначение внешних выводов для различных корпусов

- •6. Питание

- •7. Порты ввода-вывода

- •8. Архитектура ядра процессора

- •9. Память

- •10. Системный контроллер

- •10.1 Организация памяти системного контроллера

- •10.2 Контроллер сброса

- •10.3 Тактовый генератор

- •10.4 Контроллер управления потребляемой мощностью

- •Расширенный контроллер прерываний и модуль внутрисхемной отладки

- •Таймеры, контроллер портов ввода-вывода и контроллер режимов стабилизатора напряжения питания

- •11. Периферийные модули

- •11.1 Организация памяти периферийных модулей

- •11.2 Дополнительные функции портов ввода-вывода

- •11.3 Функции портов pa0…pa31

- •11.4 Идентификаторы периферийных модулей

- •11.5 Последовательный периферийный интерфейс

- •Двухпроводной интерфейс, usart, spi

- •11.9 Таймер-счетчик (tc)

- •Шим контроллер, usb, ацп

- •12. Обзор процессора arm7tdmi

- •13. Отличительные способности средств отладки и тестирования Описание и структурная схема

- •13.3 Примеры применения

- •13.4 Описание выводов для отладки и тестирования

- •13.5 Функциональное описание

- •14. Контроллер сброса (rstc) Обзор и структурная схема

- •14.3 Функциональное описание

- •14.4 Пользовательский интерфейс контроллера сброса

- •15. Таймер реального времени (rtt)

- •15.3 Функциональное описание

- •15.4 Пользовательский интерфейс таймера реально времени

- •16. Интервальный таймер (pit)

- •16.3 Функциональное описание

- •16.4 Пользовательский интерфейс интервального таймера

- •17. Сторожевой таймер (wdt)

- •17.3 Функциональное описание

- •17.4 Пользовательский интерфейс сторожевого таймера

- •18. Контроллер режимов стабилизатора напряжения (vreg)

- •19. Контроллер памяти (mc)

- •19.3 Функциональное описание

- •19.4 Пользовательский интерфейс контроллера памяти

- •20. Контроллер встроенной флэш-памяти (efc)

- •20.3 Пользовательский интерфейс контроллера встроенной флэш-памяти

- •21. Интерфейс программирования флэш-памяти (ffpi)

- •21.3. Последовательный интерфейс программирования флэш-памяти

- •22. Стартовый загрузчик at91sam7 (бут загрузчик)

- •23. Контроллер пдп (dma) периферийных модулей

- •23.3 Функционирование контроллера dma

- •23.4 Контроллер пдп (pdc). Интерфейс работы

- •24. Расширенный Контроллер Прерываний (aic)

- •24.6 Особенности контроллеров at91 серии

- •24.7 Функциональное описание

- •24.8 Контроллер прерываний aic. Интерфейс пользователя

- •25. Тактовый генератор

- •26. Контроллер управления потребляемой мощности (pmc)

- •26.5 Контроллер тактовых сигналов периферийных модулей (Peripheral Clock Controller)

- •26.6 Контроллер программно управляемых внешних тактовых сигнала

- •6.7 Последовательность программирования

- •26.8 Переключение тактовых сигналов

- •26.9 Регистры контроллера управления потребляемой мощности

- •27. Модуль внутрисхемной отладки (dbgu)

- •27.4. Работа уапп (uart)

- •27.5 Пользовательский интерфейс модуля внутрисхемной отладки

- •28. Контроллер параллельного ввода-вывода

- •8.5 Функциональное описание

- •28.7. Пользовательский интерфейс контроллера параллельного ввода - вывода

- •9. Последовательный периферийный интерфейс (spi)

- •29.6 Функциональное описание

- •29.7 Пользовательский интерфейс последовательно - параллельного интерфейса (spi)

- •30. Двухпроводной интерфейс

- •30.5 Функциональное описание

- •30.6. Пользовательский интерфейс двухпроводного интерфейса

- •33. Таймер-счетчик (тс)

- •33.5 Функциональное описание

- •33.6 Пользовательский интерфейс таймера-счетчика (тс)

- •34. Контроллер широтно-импульсной модуляции (шим)

- •34.5 Функциональное описание

- •34.6 Пользовательский интерфейс шим-контроллера (pwm)

- •35. Порт usb-устройства (udp)

- •35.5. Функциональное описание

- •35.5.2.8 Транзакция "Статус"

- •35.6. Пользовательский интерфейс usb порта (udp)

- •36. Аналогово-цифровой преобразователь (ацп)

- •36.5 Функциональное описание

- •36.6 Пользовательский интерфейс ацп

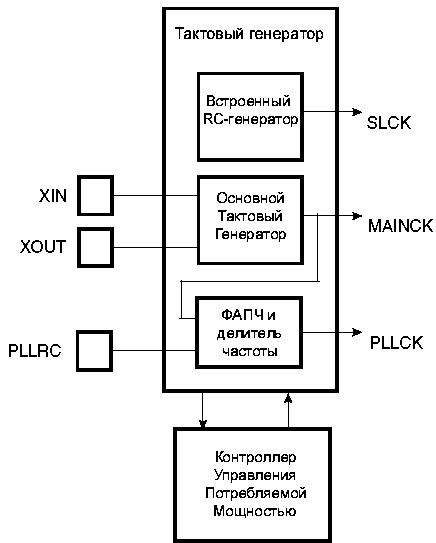

10.3 Тактовый генератор

Тактовый генератор имеет в своем составе низкочастотный RC-генератор, главный осциллятор и модуль ФАПЧ (PLL). Ниже приведены основные характеристики тактового генератора.

Частота RC-генератора: 22 кГц … 42 кГц

Частота основного тактового генератора: 3МГц … 20 МГц

Выход основного тактового генератора может быть программно отключен

Выходная частота модуля ФАПЧ: 80МГц … 220 МГц

Выходные сигналы тактового генератора: SLCK, MAINCK и PLLCK

Рисунок

10-4. Структурная схема тактового генератора

Рисунок

10-4. Структурная схема тактового генератора

10.4 Контроллер управления потребляемой мощностью

Контроллер управления потребляемой мощностью использует выходы тактового генератора для формирования следующих синхронизирующих сигналов:

синхронизирующий сигнал процессора (PCK);

главный синхронизирующий сигнал (MCK);

синхронизирующий сигнал USB порта (UDPCK), кроме AT91SAM7S32;

независимые синхронизирующие сигналы периферийных модулей;

три программно управляемых внешних тактовых выхода.

Синхронизирующий сигнал процессора (PCK) программно настраивается на частоту от нескольких сот кГц до максимальной рабочей частоты микроконтроллера.

Главный синхронизирующий сигнал (MCK) отключается тогда, когда процессор переходит холостой режим работы, таким образом, уменьшая общую потребляемую мощность.

Рисунок

10-5. Структурная схема контроллера

управления потребляемой мощностью

Рисунок

10-5. Структурная схема контроллера

управления потребляемой мощностью

Расширенный контроллер прерываний и модуль внутрисхемной отладки

10.5 Расширенный Контроллер Прерываний

Управление внутренними линиями прерывания процессора ARM (nIRQ и nFIQ)

Индивидуально маскируемые источники прерывания, каждый с собственным вектором

Источник 0 зарезервирован для Быстрого Прерывания (FIQ)

Источник 1 зарезервирован для системной периферии: RTT, PIT, EFC, PMC, DBGU и др.

Остальные источники предназначены для прерываний от периферийных модулей и внешних прерываний

Программируемые внутренние и внешние источники прерываний как по фронту/срезу, так и по низкому/высокому уровню

8-уровневый контроллер приоритета прерываний

Обслуживание прерываний ядра процессора

Управление приоритетами прерываний

Поддержка вложенных прерываний

Векторы прерываний

Оптимизация процесса передачи управления обработчикам прерываний и их выполнения

Один 32-битный регистр для всех 32-х векторов прерываний

Регистр векторов прерываний, хранящий вектор текущего возникшего прерывания

Защитный режим

Упрощение процесса отладки, благодаря запрету некоторых прерываний

Симуляция быстрого прерывания

Возможность переключения любого источника прерываний в качестве быстрого прерывания FIQ

Маскирование прерываний

Выполнение синхронизации событий процессора без необходимости формирования прерываний

10.6 Модуль внутрисхемной отладки

Модуль внутрисхемной отладки состоит из следующих узлов:

Один полнодуплексный двухвыводный UART

Один интерфейс для поддержки отладочного канала связи (DDC)

Один набор регистров с уникальными идентификационными номерами микроконтроллера

Один интерфейс, предоставляющий доступ через внутрисхемный эмулятор (ICE)

Двухвыводный полнодуплексный UART

Полностью совместим с USART

Программируемый генератор битовых интервалов

Контроль за ошибками четности/нечетности и ошибкой кадра

Режимы автоматического эха, каналы внутренней и внешней петли обратной связи.

Поддержка отладочного канала связи

Аппаратная доступ к сигналам COMMRX и COMMTX из ARM ядра процессора

Идентификационные Регистры Чипа (ID)

Определение номера ревизии микроконтроллера, размера встроенной флэш-памяти и встроенной статической памяти и набора встроенных периферийных модулей

Идентификационный номер AT91SAM7S256 (версия 0): ID = 0x270B0940

Идентификационный номер AT91SAM7S128 (версия 0): ID = 0x270A0740

Идентификационный номер AT91SAM7S64 (версия 0): ID = 0x27090540

Идентификационный номер AT91SAM7S321 (версия 0): ID = 0x27080342

Идентификационный номер AT91SAM7S32 (версия 0): ID = 0x27083040