- •Архітектура пеом

- •1. Інтервальний таймер і8253/і8254 на платі івм рс: принцип будови та функціонування

- •2.Програмування інтервального таймера на рівні портів

- •3.!Читання конcтант перерахунку каналів інтервального таймера і8253/і8254

- •4.! Читання байту стану каналів 0-2 інтервального таймера: спосіб 1, 2.

- •5.! Системний час в івм рс: таймер bios (таймер ос).

- •6.Засоби bios та ос для роботи з таймером bios.

- •7.Реальний час в івм рс: годинник реального часу (rtc)

- •8.Функціональна схема годинника реального часу та порти доступу (rtc) на платі ibm pc.

- •9. Керуючі та регістри стану годинника реального часу (rtc).

- •10.Сигнальне переривання від годинника реального часу (rtc).

- •11. Періодичне переривання від годинника реального часу (rtc).

- •12.Програмування годинника реального часу (rtc).

- •13.Апаратна реалізація порту послідовної передачі даних на платі ibm pc, принцип побудови уапп.

- •14. Порти асинхронного адаптера та їх призначення

- •16. Контролер прямого доступу до пам’яті (dma). Призначення і основні функції

- •17.! Регістри каналів контролера прямого доступу до пам’яті (dma).

- •18.!Алгоритм ініціалізації контролера прямого доступу до пам’яті (dma).

- •19.! Реалізація прямого доступу до пам’яті (пдп) в івм рс ат

- •20.! Контролер переривань на платі івм рс (і8259): принцип будови та функціонування

- •21.Загальна схема переривань в івм рс ат

- •22.Види переривань: апаратні та програмні переривання

- •23.Особливості обробки апаратних переривань, пріоритети обслуговування запитів на переривання та їх зміна.

- •24. Суть і призначення векторів переривань. Таблиця векторів переривань та зміна її елементів.

- •25.! Порти доступу до контролера переривань на платі івм рс

- •27.Керування пам`яттю. Сегментація пам`яті.

- •28.Дескрипторні таблиці. Селектори сегментів.

- •29.Сторінкова організація пам`яті, сторінкове перетворення адреси.

- •30.Алгоритм сегмента сторінкової адресації.

12.Програмування годинника реального часу (rtc).

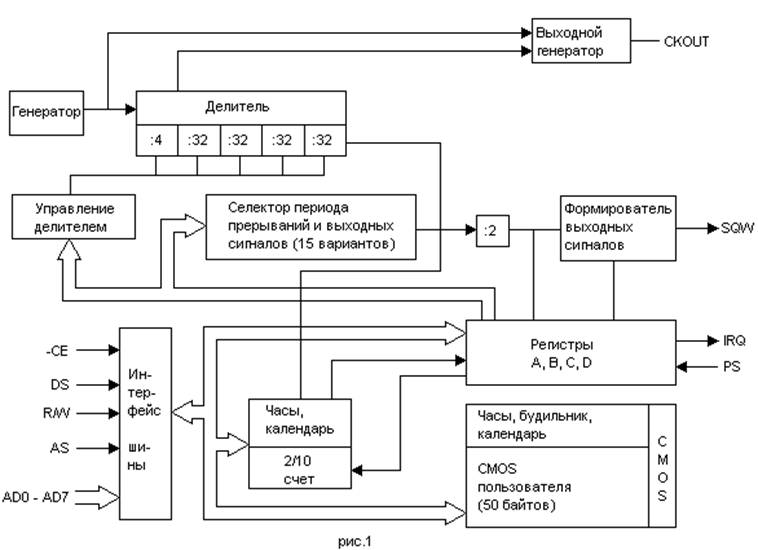

До складу IBM PC AT входять годинник реального часу Real Time Clock (RTC) і 64 байта НЕРУЙНІВНИЙ оперативної КМОП пам'яті (CMOS), що живляться від автономного джерела живлення. При включенні ПЕОМ вміст CMOS аналізується POST, який витягує з неї конфігурацію системи та поточні дату і час. Годинник реального часу RTC і CMOS пам'ять виконані на базі мікросхеми МС146818 фірми Motorola, спрощена структурна схема якої представлена на рис. 1.

Призначення сигналів наступне:-CE - дозвіл кристала (вихід дешифратора адреси); DS - строб даних; AS - адресний стрибає; R / W - читання / запис; SQW - вихідні прямокутні імпульси - меандр (у IBM PC AT не використовуються); IRQ - запит на переривання від RTC; PS - сигнал стану харчування (використовується для контролю достовірності даних); CKOUT - синхросигнал, який може використовуватися як вхідний синхросигнал мікропроцесора.

Основна частина RTC - задає генератор (внутрішній або зовнішній) з частотою 4.194304 МГц, 1.048576 МГц і дільник частоти, у якого вихід останнього каскаду (1 Гц) управляє годинами.

Для доступу до даних CMOS використовуються порти 70h і 71h, причому адреса регістра подається в 70h порт, а дані читаються / пишуться через 71h порт.

Адреси CMOS з 10h за 20h захищені контрольною сумою, що зберігається за адресами 2Eh-2Fh. Тому зміни вмісту цих адрес необхідно супроводжувати перерахунком і зміною контрольної суми. Порт 70h застосовується не тільки для завдання адреси CMOS, але і для дозволу або заборони NMI (немаскованого переривання). Якщо біт 7 дорівнює 0, то NMI дозволяється, якщо 1 - забороняється.

Всі дані RTC зберігаються в двійковій - десятковому форматі (BCD). Байти будильника 1h, 3h, 5h служать для створення часу вироблення сигналу переривання від RTС. Кожен байт може містити конкретне значення часу (секунди і хвилини в межах 0-59, а годинник в межах 0-23) і "байдуже" значення - код в межах C0h-FFh, тобто два старших розряду містять 1. При конкретному завданні часу переривання виробляється раз на добу (2 рази при 12-ти годинному часом). Якщо байт годин містить "байдужий" код, переривання кожну годину; якщо байт годин і хвилин "байдужі", переривання кожну хвилину; і при всіх "байдужих" байтах - кожну секунду.

0Ah - Регістр A стану RTC:

0Bh - Регістр B стану RTC:

0Ch - Регістр З стану RTC: біти стану переривань, тільки для читання. При читанні з регістра всі розряди скидаються.

0Dh - Регістр D стану RTC. Біт 7 = 1, якщо CMOS отримує харчування; 0 = немає харчування від автономного джерела.

0Eh - Байт результатів початкового тестування:

0Fh - Байт стану перезавантаження. Цей байт зчитується після скидання ЦП, щоб визначити чи не був скидання викликаний для виведення 80286 із захищеного режиму.

13.Апаратна реалізація порту послідовної передачі даних на платі ibm pc, принцип побудови уапп.

Комп'ютер може бути оснащений одним або двома портами послідовної передачі даних. Ці порти розташовані або на материнській платі, або на окремій платі, що вставляється в слоти розширення материнської плати.

Бувають також плати, містять 4 або 8 портів послідовної передачі даних. Їх часто використовують для підключення декількох комп'ютерів або терміналів до одного, центрального, комп'ютеру.

В основі послідовного порту передачі даних лежить мікросхема Intel 8250. Це універсальний асинхронний приймач-передавач (UART - Universal Asynchronous Receiver Transmitter). Мікросхема містить декілька внутрішніх регістрів, доступних через команди введення / виведення.

Мікросхема 8250 містить регістри передавача і приймача даних. При передачі байта він записується в буферний регістр передавача, звідки потім переписується в зсувний регістр передавача. Байт "висувається" з зсувного регістру по бітам.

Аналогічно є зсувний і буферний регістри приймача.

Програма має доступ тільки до буферних регістрів, копіювання інформації в зсувні регістри і процес зсуву виконується мікросхемою 8250 автоматично.

Зовнішні пристрої підключаються до порту введення / виводу через роз'єм DB25P (що має 25 висновків) або DB9P (що має 9 висновків). Наведемо розводку роз'єму послідовної передачі даних DB25P:

Номер контакта |

Назначение контакта |

Вход или выход |

1 |

Защитное заземление |

- |

2 |

Передаваемые данные (Transmitted Data) |

Выход |

3 |

Принимаемые данные (Received Data) |

Вход |

4 |

Запрос для передачи (Request to send, RTS) |

Выход |

5 |

Сброс для передачи (Clear to Send, CTS) |

Вход |

6 |

Готовность данных (Data Set Ready, DSR) |

Вход |

7 |

Сигнальное заземление |

- |

8 |

Детектор принимаемого с линии сигнала (Data Carrier Detect, DCD) |

Вход |

9-19 |

Не используются |

|

20 |

Готовность выходных данных (Data Terminal Ready, DTR) |

Выход |

21 |

Не используется |

|

22 |

Индикатор вызова (Ring Indicator, RI) |

Вход |

23-25 |

Не используется |

|

Рівні напруги на лініях роз'єму становлять для логічного нуля -15 вольт, для логічної одиниці - +15 вольт.

Доступ до окремих лініях можливий через порти введення / виведення асинхронного адаптера, які ми розглянемо в наступному розділі. Там же буде описано призначення окремих ліній роз'єму.

Протокол UART (Universal asynchronous receiver/transmitter) или, по-русски, УАПП (универсальный асинхронный приемопередатчик) — старейший и самый распространенный на сегодняшний день физический протокол передачи данных. Наиболее известен из семейства UART протокол RS-232 (в народе – COM-порт, тот самый который стоит у тебя в компе). Это, наверное, самый древний компьютерный интерфейс. Он дожил до наших дней и не потерял своей актуальности.

Надо сказать, что изначально интерфейс УАПП появился в США как средство для передачи телеграфных сообщений, и рабочих бит там было пять (как в азбуке Морзе). Для передачи использовались механические устройства. Потом появились компьютеры, и коды ASCII, которые потребовали семь бит. В начале 60-х на смену пришла всем известная 8-битная таблица ASCII, и тогда формат передачи стал занимать полноценный байт, плюс управляющие три бита.

В 1971 году, когда уже начался бум микросхем, Гордон Белл для компьютеров PDP фирмы Western Digital сделал микросхему UART WD1402A. Примерно в начале 80-х фирмой National Semiconductor был создан чип 8520. В 90-е был придуман буфер к интерфейсу, что позволило передавать данные на более высоких скоростях. Этот интерфейс, не претерпев практически никаких изменений, дошел и до наших дней