- •Архітектура пеом

- •1. Інтервальний таймер і8253/і8254 на платі івм рс: принцип будови та функціонування

- •2.Програмування інтервального таймера на рівні портів

- •3.!Читання конcтант перерахунку каналів інтервального таймера і8253/і8254

- •4.! Читання байту стану каналів 0-2 інтервального таймера: спосіб 1, 2.

- •5.! Системний час в івм рс: таймер bios (таймер ос).

- •6.Засоби bios та ос для роботи з таймером bios.

- •7.Реальний час в івм рс: годинник реального часу (rtc)

- •8.Функціональна схема годинника реального часу та порти доступу (rtc) на платі ibm pc.

- •9. Керуючі та регістри стану годинника реального часу (rtc).

- •10.Сигнальне переривання від годинника реального часу (rtc).

- •11. Періодичне переривання від годинника реального часу (rtc).

- •12.Програмування годинника реального часу (rtc).

- •13.Апаратна реалізація порту послідовної передачі даних на платі ibm pc, принцип побудови уапп.

- •14. Порти асинхронного адаптера та їх призначення

- •16. Контролер прямого доступу до пам’яті (dma). Призначення і основні функції

- •17.! Регістри каналів контролера прямого доступу до пам’яті (dma).

- •18.!Алгоритм ініціалізації контролера прямого доступу до пам’яті (dma).

- •19.! Реалізація прямого доступу до пам’яті (пдп) в івм рс ат

- •20.! Контролер переривань на платі івм рс (і8259): принцип будови та функціонування

- •21.Загальна схема переривань в івм рс ат

- •22.Види переривань: апаратні та програмні переривання

- •23.Особливості обробки апаратних переривань, пріоритети обслуговування запитів на переривання та їх зміна.

- •24. Суть і призначення векторів переривань. Таблиця векторів переривань та зміна її елементів.

- •25.! Порти доступу до контролера переривань на платі івм рс

- •27.Керування пам`яттю. Сегментація пам`яті.

- •28.Дескрипторні таблиці. Селектори сегментів.

- •29.Сторінкова організація пам`яті, сторінкове перетворення адреси.

- •30.Алгоритм сегмента сторінкової адресації.

19.! Реалізація прямого доступу до пам’яті (пдп) в івм рс ат

20.! Контролер переривань на платі івм рс (і8259): принцип будови та функціонування

Контролеры

Всі пристрої на системної шині мікропроцесор розглядає або як адресуемую пам'ять, або як порти виводу-введення-висновку. Власне кажучи, під портом розуміють якусь схему поєднання, що зазвичай включає у собі чи кілька регістрів виводу-введення-висновку (особливих осередків пам'яті). Про скоєнні якогось події мікропроцесор може дізнатися лише за сигналом, званому перериванням. У цьому виконання поточної послідовності команд припиняється (переривається), а натомість починає виконуватися інша послідовність, відповідна даному перериванню. Зазвичай переривання поділяються на апаратні, логічні й програмні. Апаратні переривання (IRQ) передаються спеціальними лініях системної шини і пов'язані з запитами від зовнішніх пристроїв (наприклад, натискання клавіші на клавіатурі). Логічні переривання виникають під час роботи самого мікропроцесора (наприклад, розподіл на нуль), а програмні ініціюються виконуваної програмою і звичайно йдуть на виклику спеціальних подпрограмм.

У перших комп'ютерах IBM PC використовувалася мікросхема контролера переривань i8259 (Interrupt Controller), має вісім входів для сигналів переривань (IRQ0-IRQ7). Як відомо, за одну і те час мікропроцесор може обслуговувати лише одна подія у виборі даного події їй сприяє контролер переривань, яким установлено для кожного зі своїх входів певний рівень важливості - пріоритет. Найвищий пріоритет має лінія запиту переривання IRQ0, а найменший - IRQ7, тобто пріоритет убуває гаразд зростання номери лінії. У IBM PC/AT восьми ліній переривання стало замало і кількість було збільшено до 15. У перших моделях при цьому використовувалося каскадне включення двох мікросхем i8259. Воно здійснювалося шляхом під'єднання виходу другого контролера до входу IRQ2 першого. Важливо розуміння тут таке. Лінії переривання IRQ8 - IRQ15 (то є входи другого контролера) мають пріоритет нижче ніж IRQ1, але вище IRQ3. У режимі прямого доступу (DMA, Direct Memory Access) периферійне пристрій пов'язані з оперативної пам'яттю безпосередньо, а чи не через внутрішні регістри мікропроцесора. Найефективнішою така передача даних буває ситуаціях, коли визначена висока швидкість обміну для великої кількості інформації. Для ініціалізації процесу прямого доступу на системної шині використовуються відповідні сигнали. У комп'ютерах, сумісних з IBM РС і PC/XT, в організацію прямого доступу на згадку про використовується одна 4-канальная мікросхема DMA i8237, канал 0 якої призначений для регенерації динамічної пам'яті. Канали 2 і трьох служать керувати високошвидкісної передачею даних між дисководами гнучких дисків, вінчестером і оперативної пам'яттю відповідно. IBM PC/AT-совместимые комп'ютери мають 7 каналів прямого доступу до пам'яті. У перших комп'ютерах до цього йшли каскадним включенням двох мікросхем i8237, як у разі контролерів прерываний.

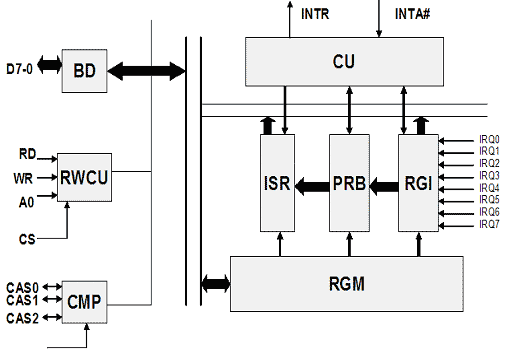

Обробка переривань на основі контролера 8259A Контролер переривань 8259A являє собою пристрій, що реалізує до восьми рівнів запитів на переривання, З можливістю програмного маскування і зміни порядку обслуговування переривань. Контролер переривань (рис. 1) Складається з наступних блоків:

RGI - реєстр заборон переривань; Зберігає всі рівні, на які надходять запити IRQx.

PRB - схема прийняття рішень за пріоритетами; схема ідентифікує пріоритет запитів і вибирає запит з найвищим пріоритетом.

ISR - регістр обслуговуються переривань; Зберігає рівні запитів переривань, Що знаходяться на обслуговуванні контролера переривань.

RGM - регістр маскування переривань; Забезпечує заборону однієї або кількох ліній запитів переривання.

BD - буфер даних; призначений для сполучення з системною шиною даних.

RWCU - блок керування записом / читанням; приймає керуючі сигнали від мікропроцесора і задає режим функціонування контролера переривань.

CMP - схема каскадного буфера-компаратора; використовується для включення в систему декількох контролерів.

CU - схема управління; виробляє сигнали переривання і формує трехбайтовую команду CALL для видачі на шину даних.

Рис. 1.Структура контролера переривань 8259А Один контролер 8259A здатний обслуговувати переривання від 8 джерел. Для обслуговування більшої кількості пристроїв використовується каскадне включення контролерів . У системах IBM PC AT каскадне включення дозволяє до 15 пристроїв сигналізувати про переривання