- •Логические функции (1,2,3 выводные). Законы де Моргана.

- •Минимизация функций алгебры логики (фал). Разложение фал в различных базисах.

- •Язык конфигурирования программируемых логических схем Verilog.

- •Основные конструкции языка (описать, пример использования)

- •Реализация комбинационной логики на Verilog

- •Формальное определение

- •Способы задания

- •Автомат Мили

- •Автомат Мура

- •Реализация секвенциальной логики на Verilog

- •Автомат Мили

- •Автомат Мура

- •Реализация дешифраторов/шифраторов (2 варианта)

- •Реализация мультиплексоров

- •Реализация счетчиков (модули счета, пропуск состояний)

- •Реализация регистров (обычных, сдвиговых)

- •Реализация цифровых автоматов (Мура)

- •Реализация цифровых автоматов (Милли)

- •Реализация генератора последовательностей.

- •Реализация мультивибратора.

- •Реализация одновибратора.

- •Процессор виды, способы реализации. Микропроцессор. Микропроцессорная система. Трехшинная архитектура микропроцессорных систем.

- •Виды процессоров:

- •Назначение шин следующее:

- •Необходимость создания программного цифрового автомата. Гарвардская архитектура (достоинства недостатки).

- •Способы реализации стековой памяти.

- •Машинный такт, цикл. Блок- схема машинного цикла.

- •Проблема выбора структуры и формата команд.

- •Недостатки cisc архитектуры

- •Характерные особенности risc-процессоров

- •Группы команд. Реализаций групп команд в различных архитектурах.

- •Структура микроконтроллера c8051f411

Реализация цифровых автоматов (Мура)

module statem

(

input clk, in, reset,

output reg [1:0] out

);

// Declare state register

reg [2:0]state;

// Declare states

parameter S0 = 0, S1 = 1, S2 = 2, S3 = 3, S4 = 4, S5 = 5, S6 = 6, S7 = 7;

// Output depends only on the state

always @ (state) begin

case (state)

S0:

out = 2'b01;

S1:

out = 2'b01;

S2:

out = 2'b01;

S3:

out = 2'b01;

S4:

out = 2'b00;

S5:

out = 2'b00;

S6:

out = 2'b10;

S7:

out = 2'b10;

endcase

end

// Determine the next state

always @ (posedge clk or posedge reset) begin

if (reset)

state <= S7;

else

case (state)

S0:

if (in)

state <= S5;

else

state <= S6;

S1:

if (in)

state <= S2;

else

state <= S0;

S2:

if (in)

state <= S7;

else

state <= S4;

S3:

state <= S7;

S4:

if (in)

state <= S6;

else

state <= S1;

S5:

state <= S5;

S6:

if (in)

state <= S6;

else

state <= S4;

S7:

if (in)

state <= S3;

else

state <= S0;

endcase

end

endmodule

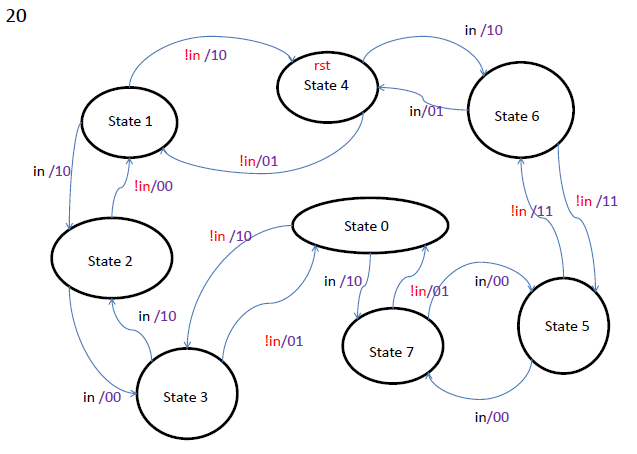

Реализация цифровых автоматов (Милли)

module mealy

(

input clk, in, reset,

output reg [1:0] out

//output state

);

reg [2:0]state;

parameter S0 = 0, S1 = 1, S2 = 2, S3 = 3,S4 = 4, S5 = 5, S6 = 6, S7 = 7;

always @ (posedge clk or posedge reset) begin

if (reset)

state <= S4;

else

case (state)

S0:

if (in)

begin

state <= S7;

end

else

begin

state <= S3;

end

S1:

if (in)

begin

state <= S2;

end

else

begin

state <= S4;

end

S2:

if (in)

begin

state <= S3;

end

else

begin

state <= S1;

end

S3:

if (in)

begin

state <= S2;

end

else

begin

state <= S0;

end

S4:

if (in)

begin

state <= S6;

end

else

begin

state <= S1;

end

S5:

if (in)

begin

state <= S7;

end

else

begin

state <= S6;

end

S6:

if (in)

begin

state <= S4;

end

else

begin

state <= S5;

end

S7:

if (in)

begin

state <= S5;

end

else

begin

state <= S0;

end

endcase

end

always @ (state or in)

begin

case (state)

S0:

begin

out = 2'b10;

end

S1:

begin

out = 2'b10;

end

S2:

begin

out = 2'b00;

end

S3:

if (in)

begin

out = 2'b10;

end

else

begin

out = 2'b01;

end

S4:

if (in)

begin

out = 2'b10;

end

else

begin

out = 2'b01;

end

S5:

if (in)

begin

out = 2'b00;

end

else

begin

out = 2'b11;

end

S6:

if (in)

begin

out = 2'b01;

end

else

begin

out = 2'b11;

end

S7:

if (in)

begin

out = 2'b00;

end

else

begin

out = 2'b01;

end

endcase

end

endmodule