- •Логические функции (1,2,3 выводные). Законы де Моргана.

- •Минимизация функций алгебры логики (фал). Разложение фал в различных базисах.

- •Язык конфигурирования программируемых логических схем Verilog.

- •Основные конструкции языка (описать, пример использования)

- •Реализация комбинационной логики на Verilog

- •Формальное определение

- •Способы задания

- •Автомат Мили

- •Автомат Мура

- •Реализация секвенциальной логики на Verilog

- •Автомат Мили

- •Автомат Мура

- •Реализация дешифраторов/шифраторов (2 варианта)

- •Реализация мультиплексоров

- •Реализация счетчиков (модули счета, пропуск состояний)

- •Реализация регистров (обычных, сдвиговых)

- •Реализация цифровых автоматов (Мура)

- •Реализация цифровых автоматов (Милли)

- •Реализация генератора последовательностей.

- •Реализация мультивибратора.

- •Реализация одновибратора.

- •Процессор виды, способы реализации. Микропроцессор. Микропроцессорная система. Трехшинная архитектура микропроцессорных систем.

- •Виды процессоров:

- •Назначение шин следующее:

- •Необходимость создания программного цифрового автомата. Гарвардская архитектура (достоинства недостатки).

- •Способы реализации стековой памяти.

- •Машинный такт, цикл. Блок- схема машинного цикла.

- •Проблема выбора структуры и формата команд.

- •Недостатки cisc архитектуры

- •Характерные особенности risc-процессоров

- •Группы команд. Реализаций групп команд в различных архитектурах.

- •Структура микроконтроллера c8051f411

Реализация мультиплексоров

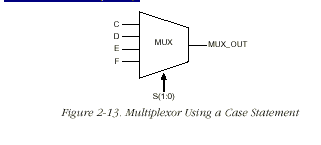

Другим часто используемым устройством является мультиплексор (Multiplexors).

Как правило, для построения мультиплексора удобно использовать оператор Case. Оператор case обеспечивает параллельную обработку. Оператор выбора case (case statement) используется для выбора одного варианта из нескольких в зависимости от условий.

Средства синтеза с Verilog поддерживают приоритет в выполнении оператора case и в ряде случаев необходимо ввести специфические инструкции в код и для того, чтобы оператор выбора не имел приоритета

Рис.6.13 Мультиплексор 4 в 1

Пример описания на Verilog

//4:1 Multiplexor

module MUX (C, D, E, F, S, MUX_OUT);

input C, D, E, F;

input [1:0] S;

output MUX_OUT;

reg MUX_OUT;

always @(C or D or E or F or S)

begin

case (S)

2'b00 : MUX_OUT = C;

2'b01 : MUX_OUT = D;

2'b10 : MUX_OUT = E;

default : MUX_OUT = F;

endcase

end

endmodule

Реализация счетчиков (модули счета, пропуск состояний)

Счетчики являются достаточно широко распространенными устройствами, их классификация и принципы построения изложены в литературе. Следует помнить, что большинство программ синтеза не позволяют получить приемлимых результатов по быстродействию при разрядности счетчика более 8 бит, в этом случае часто применяются специфические приемы синтеза, зависящие от технологии, по которой выполнена ПЛИС.

Рассмотрим пример построения 8 разрядного счетчика, считающего в прямом направлении и имеющего цепи разрешения счета и асинхронного сброса.

Пример на Verilog

module count_en (en, clock, reset, out);

parameter Width = 8;

input clock,reset, en;

output [Width-1:0] out;

reg [Width-1:0] out;

always @(posedge clock or negedge reset)

if(!reset)

out = 8'b0;

else if(en)

out =out +1;

endmodule

Рассмотрим счетчик с модулем счета М=6..

module mod_counter( input wire reset, input wire clock, input wire [3:0]in, input wire load, output reg [3:0]cnt ); parameter MODULE = 6; always @(posedge clock or posedge reset) begin if(reset) cnt <= 4'b0000; else begin if(load) cnt <= in; else if(cnt+1==MODULE) cnt <= 4'b0000; else cnt <= cnt + 1'b1; end end endmodule

Реализация регистров (обычных, сдвиговых)

Реализация различных видов регистров:

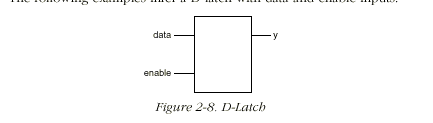

Далее рассмотрим защелки на основе D-триггеров (D-Latches)

Защелка с разрешением выхода (D-Latch with Data and Enable)

Описание на Verilog

module d_latch (enable, data, y);

input enable, data;

output y;

reg y;

always @(enable or data)

if (enable)

y = data;

endmodule

Реализация сдвигового регистра.

module simple_shift ( operandA, operandB, out_shl, out_shr, out_sar);

// два входных 8-ми битных операнда input [7:0] operandA, operandB;

// Выходы для операций сдвига output [15:0] out_shl; output [7:0] out_shr; output [7:0] out_sar;

//логический сдвиг влево assign out_shl = operandA << operandB; // пример: на сколько сдвигать определяется 3-мя битами второго операнда assign out_shr = operandA >> operandB[2:0];

//арифметический сдвиг вправо (сохранение знака числа) assign out_sar = operandA >>> operandB[2:0]; endmodule