- •Логические функции (1,2,3 выводные). Законы де Моргана.

- •Минимизация функций алгебры логики (фал). Разложение фал в различных базисах.

- •Язык конфигурирования программируемых логических схем Verilog.

- •Основные конструкции языка (описать, пример использования)

- •Реализация комбинационной логики на Verilog

- •Формальное определение

- •Способы задания

- •Автомат Мили

- •Автомат Мура

- •Реализация секвенциальной логики на Verilog

- •Автомат Мили

- •Автомат Мура

- •Реализация дешифраторов/шифраторов (2 варианта)

- •Реализация мультиплексоров

- •Реализация счетчиков (модули счета, пропуск состояний)

- •Реализация регистров (обычных, сдвиговых)

- •Реализация цифровых автоматов (Мура)

- •Реализация цифровых автоматов (Милли)

- •Реализация генератора последовательностей.

- •Реализация мультивибратора.

- •Реализация одновибратора.

- •Процессор виды, способы реализации. Микропроцессор. Микропроцессорная система. Трехшинная архитектура микропроцессорных систем.

- •Виды процессоров:

- •Назначение шин следующее:

- •Необходимость создания программного цифрового автомата. Гарвардская архитектура (достоинства недостатки).

- •Способы реализации стековой памяти.

- •Машинный такт, цикл. Блок- схема машинного цикла.

- •Проблема выбора структуры и формата команд.

- •Недостатки cisc архитектуры

- •Характерные особенности risc-процессоров

- •Группы команд. Реализаций групп команд в различных архитектурах.

- •Структура микроконтроллера c8051f411

Необходимость создания программного цифрового автомата. Гарвардская архитектура (достоинства недостатки).

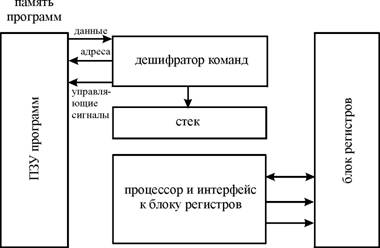

Гарвардская архитектура — архитектура ЭВМ, отличительными признаками которой являются: 1. Хранилище инструкций и хранилище данных представляют собой разные физические устройства. 2. Канал инструкций и канал данных также физически разделены.

Классическая гарвардская архитектура:

Типичные операции (сложение и умножение) требуют от любого вычислительного устройства нескольких действий:

выборку двух операндов,

выбор инструкции и её выполнение,

и, наконец, сохранение результата.

В гарвардской архитектуре характеристики устройств памяти для инструкций и памяти для данных не обязательно должны быть одинаковыми. В частности, ширина слова, тактирование, технология реализации и структура адресов памяти могут различаться. В некоторых системах инструкции могут храниться в памяти только для чтения, в то время как для сохранения данных обычно требуется память с возможностью чтения и записи. В некоторых системах требуется значительно больше памяти для инструкций, чем памяти для данных, поскольку данные обычно могут подгружаться с внешней или более медленной памяти. Такая потребность увеличивает битность (ширину) шины адреса памяти инструкций по сравнению с шиной адреса памяти данных.

Модифицированная гарвардская архитектура.

Соответствующая схема реализации доступа к памяти имеет один очевидный недостаток — высокую стоимость. При разделении каналов передачи команд и данных на кристалле процессора последний должен иметь почти вдвое большевыводов, так как шина адреса и шина данных составляют основную часть выводов микропроцессора. Способом решения этой проблемы стала идея использовать общие шину данных и шину адреса для всех внешних данных, а внутри процессора использовать шину данных, шину команд и две шины адреса. Такую концепцию стали называть модифицированной гарвардской архитектурой.

Такой подход применяется в современных сигнальных процессорах. Ещё дальше по пути уменьшения стоимости пошли при создании однокристалльных ЭВМ — микроконтроллеров. В них одна шина команд и данных применяется и внутри кристалла.

Разделение шин в модифицированной гарвардской структуре осуществляется при помощи раздельных управляющих сигналов: чтения, записи или выбора области памяти

Способы реализации стековой памяти.

Стековой называют память, доступ к которой организован по принципу: «последним записан — первым считан» (Last Input First Output — LIFO). Использование принципа доступа к памяти на основе механизма LIFO началось с больших ЭВМ. Применение стековой памяти оказалось очень эффективным при построении компилирующих и интерпретирующих программ, при вычислении арифметических выражений с использованием польской инверсной записи. В малых ЭВМ она стала широко использоваться в связи с удобствами реализации процедур вызова подпрограмм и при обработке прерываний.

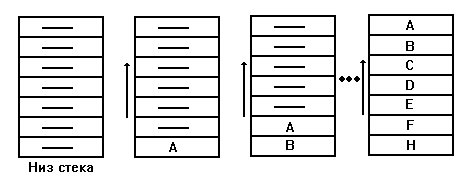

Принцип работы стековой памяти состоит в следующем (см. рис. 4.15). Когда слово А помещается в стек, оно располагается в первой свободной ячейке памяти. Следующее записываемое слово перемещает предыдущее на одну ячейку вверх и занимает его место и т.д. Запись 8-го кода, после H, приводит к переполнению стека и потере кода A. Считывание слов из стека осуществляется в обратном порядке, начиная с кода H, который был записан последним. Заметим, что выборка, например, кода E невозможна до выборки кода F, что определяется механизмом обращения при записи и чтении типа LIFO. Для фиксации переполнения стека желательно формировать признак переполнения.

Перемещение данных при записи и считывании информации в стековой памяти подобно тому, как это имеет место в сдвигающих регистрах. С точки зрения реализации механизма доступа к стековой памяти выделяют аппаратный и аппаратно-программный (внешний) стеки.

Аппаратный стек представляет собой совокупность регистров, связи между которыми организованы таким образом, что при записи и считывании данных содержимое стека автоматически сдвигается. Обычно емкость аппаратного стека ограничена диапазоном от нескольких регистров до нескольких десятков регистров, поэтому в большинстве МП такой стек используется для хранения содержимого программного счетчика и его называют стеком команд. Основное достоинство аппаратного стека — высокое быстродействие, а недостаток — ограниченная емкость.

Наиболее распространенным в настоящее время и, возможно, лучшим вариантом организации стека в ЭВМ является использование области памяти. Для адресации стека используется указатель стека, который предварительно загружается в регистр и определяет адрес последней занятой ячейки. Помимо команд CALL и RET, по которым записывается в стек и восстанавливается содержимое программного счетчика, имеются команды PUSH и POP, которые используются для временного запоминания в стеке содержимого регистров и их восстановления, соответственно. В некоторых МП содержимое основных регистров запоминается в стеке автоматически при прерывании программ. Содержимое регистра указателя стека при записи уменьшается, а при считывании увеличивается на 1 при выполнении команд PUSH и POP, соответственно.

Пример реализации простого стека на Verilog.

module stack(output [7:0] out_stack, input [7:0] in_stack, input wr); reg [7:0] st0, st1, st2, st3, st4, st5, st6, st7; always @(posedge wr) begin st7 <= st6; st6 <= st5; st5 <= st4; st4 <= st3; st3 <= st2; st2 <= st1; st1 <= st0; st0 <= in_stack; end assign out_stack = st7; endmodule