- •1. Основные архитектуры эвм и их сравнительная оценка 9неймановская, Гарвардская, risc, cisc и пр.)

- •Принципы фон Неймана

- •Классическая гарвардская архитектура

- •Отличие от архитектуры фон Неймана

- •Гибридные модификации с архитектурой фон Неймана

- •Использование

- •Философия risc

- •Характерные особенности risc-процессоров

- •Недостатки cisc архитектуры

- •2. Базовая структура фон-Неймановской архитектуры эвм. Порядок выполнения команды Принцип программного управления и машина фон Неймана

- •3. Структура и форматы команд эвм

- •Форматы команд эвм

- •4. Основные способы адресации

- •Классификация способов адресации по наличию адресной информации в команде

- •Классификация способов адресации по кратности обращения в память

- •Классификация по способу формирования исполнительных адресов ячеек памяти

- •Относительная адресация

- •Стековая адресация

- •9. Иерархия памяти эвм

- •17. Контроллер прямого доступа к памяти

- •13. Ввод-вывод в программном режиме. Порт ввода-вывода.

- •16. Ввод-вывод в режиме прямого доступа к памяти

- •18. Процессоры гарвардской архитектуры: общие принципы и архитектура микроконтроллера 8051

- •Структурная организация микроконтроллера i8051.

- •2.1.1.Общие характеристики. Микроконтроллер семейства 8051 имеют следующие аппаратные особенности:

- •23. Предсказатель переходов

- •Статическое предсказание

- •Динамическое предсказание

- •24. Основные архитектуры многопроцессорных систем (окод, окмд, мкод, мкмд)

- •26. Системы массового параллелизма и многоядерные процессоры

- •25. Состояние задачи в многопрограммной (в том числе многопроцессорной) системе.

- •26. Система массового параллелизма и многоядерные процессоры: структура, организация взаимодействия.

- •21. Процессоры класса Pentium – общая архитектура, блок подготовки микрокоманд, потоки микрокоманд (на примере Pentium III)

- •12. Ввод-вывод в программном режиме: шинная архитектура, машинный цикл, командный цикл: варианты реализации механизма запрос-ответ.

- •11. Менеджер памяти. Порядок определения физического адреса.

- •8. Cisc-процессоры семейства 80х86. Блок сегментации. Формирование адреса в линейном, действительном и защищенном режимах.

- •7. Cisc-процессоры семейства 80х86. Регистровая структура операционного блока. Способы адресации(используемые в х86!!).

- •6. Cisc-процессоры семейства 80х86. Блок выборки и декорирования команд (бвдк), очередь команд. Взаимодействие бвдк, iu,fpu.

11. Менеджер памяти. Порядок определения физического адреса.

Менеджер памяти — часть компьютерной программы (как прикладной, так и операционной системы), обрабатывающая запросы на выделение и освобождение оперативной памяти или (для некоторых архитектур ЭВМ) запросы на включение заданной области памяти в адресное пространство процессора.

Основное назначение менеджера памяти в первом смысле — реализация динамической памяти. Например, в языке C динамическое выделение памяти производится через функцию malloc.

Иерархия менеджеров памяти

Распределение памяти в монопрограммировании.

Менеджеры памяти часто образуют иерархию: нижестоящие менеджеры задействуют какие-либо закономерности выделения-освобождения памяти и этим снижают нагрузку на вышестоящие. Например:

Системный. Сверху находится менеджер памяти, встроенный в ОС. Он вносит ту или иную страницу в адресное пространство процесса — а значит, работает с дискретностью в 4 килобайта и очень медленный.

Принадлежащий процессу. Менеджер памяти, встроенный в стандартную библиотеку языка программирования, берёт у ОС блоки памяти «оптом» и раздаёт их сообразно с нуждами программиста. При этом он знает, что память отдаётся только одному процессу — а значит, синхронизация потоков производится не мютексами, а фьютексами. И переключение в режим ядра происходит в двух случаях: либо когда «оперативного запаса» памяти не хватает и нужно обратиться к ОС, либо когда один из потоков «натыкается» на занятый фьютекс.

Специализированные. Некоторые динамические структуры данных, например, std::vector, также берут память у стандартной библиотеки с запасом (например, блоками по 16 элементов). Таким образом, элементы добавляются по одному, но обращение к вышестоящему менеджеру происходит один раз за 16 элементов. Объектный пул выделяет память под объекты конкретного типа и удобен, если они выделяются-освобождаются в больших количествах, и т. д.

Подобная иерархия приводит к тому, что на каждом из уровней «залёживается» свободная память. Но это оправдано: снижается фрагментация памяти и повышается скорость.

Определение физического адреса.

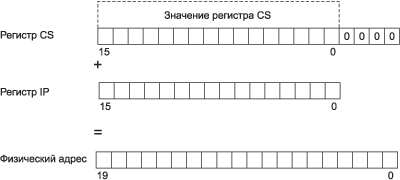

Конкретизируем задачу и ограничимся рассмотрением определения адреса команды. Для адресации операндов используется аналогичный механизм, только участвуют в этом случае другие сегментные регистры. Напомним, что для определения физического адреса команды содержимое сегментного регистра CS (code segment) умножается на 16 за счет добавления справа (к младшим битам) четырех нулей, после чего к полученному значению прибавляется содержимое указателя команд (регистр IP, instruction pointer). Получается двадцатибитовое значение, которое и позволяет указать любой байт из 220.

В защищенном режиме работы определение физического адреса осуществляется совершенно иначе. Прежде всего используется сегментный механизм для организации виртуальной памяти. При этом адреса задаются 32-битовыми значениями. Кроме этого, возможна страничная трансляция адресов, также с 32-битовыми значениями. Наконец, при работе в защищенном режиме, который по умолчанию предполагает 32-битовый код, возможно исполнение двоичных программ, созданных для работы микропроцессора в 16-битовом режиме. Для этого введен режим виртуальной 16-битовой машины и 20-битовые адреса реального режима транслируются с помощью страничного механизма в 32-битовые значения защищенного режима. Наконец, есть еще один режим -- 16-битовый защищенный, позволяющий 32-битовым микропроцессорам выполнять защищенный 16-битовый код, который был характерен для микропроцессора 80286. Правда, следует отметить, что это последний режим практически не используется, поскольку программ, созданных для него, не так уж и много.

Для изучения этих возможностей рассмотрим сначала новые архитектурные возможности микропроцессоров i80x86.