- •2. За допомогою ключів (керуються клавішами [w] і [q]) подати на вхід схеми комбінації значень r і s. Значення виходів занести в таблицю 1.3. 10

- •Лабораторна робота № 1. Дослідження rs тригера. Тригери асинхронні і з синхронізуючим входом.

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 2. Дослідження послідовного та паралельного регістрів.

- •Основні теоретичні відомості

- •2.1 Паралельний регістр

- •2.2 Послідовний регістр

- •Порядок виконання роботи

- •2.1. Дослідження паралельного регістра.

- •2.2. Дослідження послідовного регістра

- •Питання і завдання для повторення:

- •Лабораторна робота № 3. Дослідження лічильників на jk та d тригерах.

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 4. Дослідження дешифраторів, шифраторів.

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 5. Дослідження мультиплексорів.

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 6. Дослідження Арифметико-Логічного Пристрою (алп).

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 7. Дослідження Оперативного Запам'ятовуючого Пристрою (озп).

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 8. Дослідження Постійного Запам'ятовуючого Пристрою (пзп).

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 9 Аналогo-цифрові та цифро-аналогові перетворювачі.Ацп прямогоперетворення.

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 10 Аналогo-цифрові та цифро-аналогові перетворювачіЦап сходовоготипу.

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 11 Система команд микроконтроллера pic16fxх

- •Порядок виконання роботи

- •Лабораторна робота № 12 Програмування портів вводу-виводу мікроконтролера pic.

- •Основні теоретичні відомості

- •Текст файла Project3.Asm

- •Індивідуальні завдання

- •Питання і завдання для повторення:

- •Завдання для самостійної роботи студентів Додаток а.Дослідження лічильників на jk та d тригерах .

- •6.Дослідження синхронного реверсивного лічильника

- •Додаток б.Дослідження комбінаційних схем. Базові логічні елементи.

- •Додаток в.Дослідження тригерів

- •Додаток г.Дослідження регістрів

- •Список рекомендованої літератури

Лабораторна робота № 12 Програмування портів вводу-виводу мікроконтролера pic.

Мета роботи: Оволодіння технологією програмування мікроконтролерів PIC, придбання навичок роботи в інтегрованому середовищі розробки MPLAB IDE, придбання навичок написання програм для мікроконтролерів.

Програмне забезпечення: програмне забезпечення комп'ютерного моделювання електронних схем (програма Proteus (ISIS), MPLAB IDE).

Основні теоретичні відомості

Основні характеристики мікроконтролерів PIC

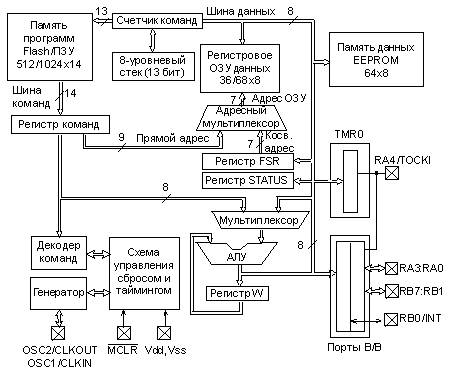

Мікроконтролери підгрупи PIC16F8X відносяться до сімейства 8-розрядних КМОН мікроконтролерів групи PIC16CXXX, для яких характерні низька вартість, цілком статична КМОН-технологія і висока продуктивність.

До складу підгрупи входять МК PIC16F83, PIC16CR83, PIC16F84 і PIC16CR84. Основні характеристики МК підгрупи PIC16F8X наведені в табл. 12.1.

Усі мікроконтролери підгрупи PIC16F8X використовують гарвардську архітектуру з RISC-процесором, що володіє наступними основними особливостями:

використовуються тільки 35 простих команд;

усі команди виконуються за один цикл (400 нс при частоті 10 Мгц), крім команд переходу, які вимагають 2 цикли;

робоча частота 0 Гц ... 10 Мгц;

роздільні шини даних (8 біт) і команд (14 біт);

512 х 14 або 1024 х 14 пам'ять програм, виконана на ПЗП або електрично перепрограмованій Flash- пам'яті;

15 восьмирозрядних регістрів спеціальних функцій (SFR);

восьмирівневий апаратний стек;

пряма, непряма і відносна адресація даних і команд;

36 або 68 восьмирозрядних регістрів загального призначення (GPR) або ОЗП;

чотири джерела переривання:

зовнішній вхід RB0/INT;

переповнення таймера TMR0;

зміна сигналів на лініях порту B;

завершення запису даних у пам'ять EEPROM;

64 x 8 електрично перепрограмована EEPROM пам'ять даних з можливістю виконання 1000000 циклів стирання/запису;

збереження даних у EEPROM протягом як мінімум 40 років.

Табл. 12.1. Основні характеристики МК підгрупи PIC16F8X. |

||||

Параметр |

PIC16F83 |

PIC16CR83 |

PIC16F84 |

PIC16CR84 |

Максимальна частота, МГц |

10 |

10 |

10 |

10 |

Flash-пам'ять програм, слів |

512 |

- |

1К |

- |

ПЗП програм, слів |

- |

512 |

- |

1К |

Пам'ять даних, байт |

36 |

36 |

68 |

68 |

Пам'ять даних у РПЗП (EEPROM), байт |

64 |

64 |

64 |

64 |

Таймери |

TMR0 |

TMR0 |

TMR0 |

TMR0 |

Кількість джерел переривань |

4 |

4 |

4 |

4 |

Кількість ліній вводу/виводу |

13 |

13 |

13 |

13 |

Діапазон напруг живлення, В |

2,0 – 6,0 |

2,0 – 6,0 |

2,0 – 6,0 |

2,0 – 6,0 |

Кількість виводів і тип корпуса |

18 DIP, SOIC |

18 DIP, SOIC |

18 DIP, SOIC |

18 DIP, SOIC |

Мікроконтролери підгрупи PIC16F8X мають розвинуті можливості вводу/виводу:

13 ліній вводу-виводу з індивідуальним встановленням напрямку обміну;

високий що втікаючий/витікаючий струми, достатні для керування світлодіодами:

максимальний струм, що втікає - 25 мА;

максимальний струм, що витікає - 20 мА;

8-бітний таймер/лічильник TMR0 з 8-бітним програмованим попереднім дільником.

Спеціалізовані мікроконтролерні функції включають наступні можливості:

автоматичне скидання при увімкненні (Power-on-Reset);

таймер увімкнення при ініціалізації (Power-up Timer);

таймер запуску генератора (Oscillator Start-up Timer);

сторожовий (Watchdog) таймер WDT із власним вмонтованим генератором, що забезпечує підвищену надійність;

EEPROM біт таємності для захисту коду;

економічний режим SLEEP;

обирані користувачем біти для встановлення режиму збудження вмонтованого генератора;

послідовний пристрій програмування Flash/EEPROM пам'яті програм і даних з використанням тільки двох виводів.

КМОН технологія забезпечує МК підгрупи PIC16F8X додаткові переваги:

статичний принцип роботи;

широкий діапазон напруг живлення: 2,0...6,0 В;

низьке енергоспоживання:

менше 2 мА при 5В та 4Мгц;

порядку 15 мкА при 2В и 32Кгц;

менше 1 мкА для SLEEP-режиму при 2В.

Мікроконтролери підгрупи PIC16F8X відрізняються між собою тільки об'ємом ОЗП даних, а також об'ємом і типом пам'яті програм. Наявність у складі підгрупи МК із Flash-пам'яттю програм полегшує створення і налагодження прототипів промислових зразків виробів.

Особливості архітектури

Спрощена структурна схема МК підгрупи PIC16F8X наведена на мал. 12.1.

Мал.

12.1.

Структурна схема МК підгрупи PIC16F8X.

Мал.

12.1.

Структурна схема МК підгрупи PIC16F8X.

Архітектура базується на концепції роздільних шин і областей пам'яті для даних і для команд (гарвардська архітектура). Шина даних і пам'ять даних (ОЗП) - мають ширину 8 біт, а програмна шина і програмна пам'ять (ПЗП) мають ширину 14 біт. Така концепція забезпечує просту, але потужну систему команд, розроблену так, що бітові, байтові і реєстрові операції працюють з високою швидкістю і з перекриттям за часом вибірок команд і циклів виконання. 14-бітова ширина програмної пам'яті забезпечує вибірку 14-бітової команди в один цикл. Двоступінчастий конвеєр забезпечує одночасну вибірку і виконання команди. Усі команди виконуються за один цикл, крім команд переходів.

Мікроконтролери PIC16F83 і PIC16CR83 адресують 512х14 пам'яті програм, а PIC16F84 і PIC16CR84 - 1Кх14 пам'яті програм. Уся пам'ять програм є внутрішньою.

Мікроконтролер може прямо або побічно звертатися до регістрів або пам'яті даних. Усі регістри спеціальних функцій, включаючи лічильник команд, відображаються на пам'ять даних. Ортогональна (симетрична) система команд дозволяє виконувати будь-яку команду над будь-яким регістром з використанням довільного методу адресації. Ортогональна архітектура і відсутність спеціальних винятків робить програмування МК групи PIC16F8X простим і ефективним.

Призначення виводів МК підгрупи PIC16F8X наведене в табл. 15.2.

-

Табл. 15.2. Призначення виводів МК підгрупи PIC16F8X.

Позначення

Тип

Буфер

Опис

OSC1/CLKIN

I

ТШ/КМОН3)

Вхід кристала генератора, RC-ланки або вхід зовнішнього тактового сигналу

OSC2/CLKOUT

O

–

Вихід кристала генератора. У RC-режимі - вихід 1/4 частоти OSC1

/MCLR

I/P

ТШ

Сигнал ініціалізації/вхід програмуючої напруги. Ініціалізація низьким рівнем.

RA0 RA1 RA2 RA3 RA4 /T0CKI

I/O I/O I/O I/O I/O

ТТЛ ТТЛ ТТЛ ТТЛ ТШ

PORTA - двонапрямлений порт вводу/виводу RA4/T0CKI може бути обраний як тактовий вхід таймера/лічильника TMR0. Вихід з відкритим стоком.

RB0/INT RB1 RB2 RB3 RB4 RB5 RB6 RB7

I/O I/O I/O I/O I/O I/O I/O I/O

ТТЛ/ТШ1) ТТЛ ТТЛ ТТЛ ТТЛ ТТЛ ТТЛ/ТШ 2) ТТЛ/ТШ 2)

PORTB - двонапрямлений порт вводу/виводу. Може бути запрограмований у режимі внутрішніх активних навантажень на лінію живлення по усіх виводах. Вивід RB0/INT може бути обраний як зовнішній вхід переривання. Виводи RB4...RB7 можуть бути програмно надбудовані як входи переривання за зміною стану на кожнім із входів. При програмуванні МК RB6 використовується як тактовий, а RB7 як вхід/вихід даних.

Vdd

P

–

Позитивна напруга живлення

Vss

P

-

Загальний провід (земля)

У таблиці використані наступні позначення: I - вхід; O - вихід; I/O - вхід/вихід; P - живлення; - - не використовується; ТТЛ - ТТЛ вхід; ТШ - вхід тригера Шмідта.

Примітки: 1) Цей буфер має вхід тригера Шмідта, коли конфігурується як вхід зовнішнього переривання. 2) Цей буфер має вхід трігера Шмідта, коли використовується в режимі послідовного програмування. 3) Цей буфер має вхід тригера Шмідта, коли конфігурується в режимі RC-генератора і КМОН-вхід в інших випадках.

Мікроконтролер містить 8-розрядний АЛП і робочий регістр W. АЛП є арифметичним модулем загального призначення і виконує арифметичні і логічні функції над умістом робочого регістра і кожного з регістрів контролера. АЛП може виконувати операції додавання, віднімання, зсуву і логічні операції. Якщо не зазначене інше, то арифметичні операції виконуються в додатковому двійковому коді.

У залежності від результату операції, АЛП може змінювати значення бітів регістра STATUS: C (Carry), DC (Digit carry) і Z (Zero).

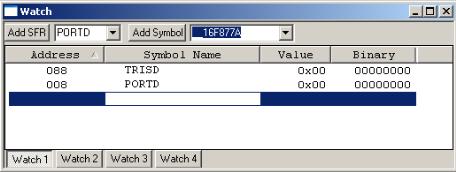

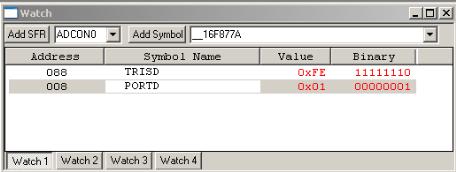

Порт вводу-виводу мікроконтролера складається з двох регістрів: керуючого регістра TRIS, і регістра PORT. Керуючий регістр TRIS визначає напрям надходження інформації. Інформація може надходити в контролер, або виводитися з контролера. Якщо регістр TRIS налаштований на вихід, то запис інформації в регістр порту призводить до появи цієї інформації на ніжках мікросхеми. Більшість портів мікроконтролера восьмирозрядних. Розрядність порту вводу-виводу визначається кількістю доступних біт в регістрах PORT і TRIS. Один біт регістра TRIS управляє напрямком роботи одного біта регістра PORT. Так, наприклад, для настройки всіх розрядів порту PORTD на вихід, до реєстру TRISD повинно бути занесено значення «всі вісім біт - нулі». Якщо планується використовувати на вихід тільки один розряд (біт) порту, то достатньо встановити тільки один нуль в регістрі TRIS. Наприклад, якщо скинути третій біт регістра TRISD (TRISD, 3 = 0), то третій біт порту PORTD (PORTD, 3) буде працювати на виведення інформації і передавати нуль або одиницю з третього біта PORTD на ніжку корпусу мікросхеми.

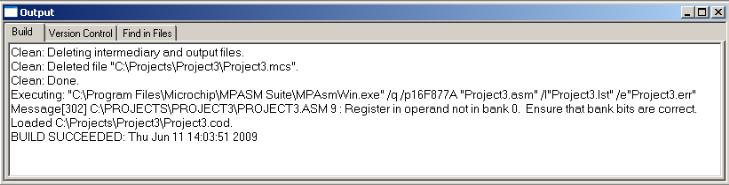

Пам'ять даних мікроконтролера розбита на банки. Банки - це набори елементів пам'яті в єдиному адресному просторі. Розмір цього простору визначається полем адреси команд мікроконтролера. У нашому випадку поле адреси команди містить 7 біт, значить можна адресувати 128 (27) осередків. Адресний простір одного банку кратно числу 07Fh (числу 127 в десятковій системі числення). Ещ ѐ є два біта <RP1:RP0> в регістрі STATUS. Це дозволяє звертатися до чотирьох ѐ м банкам пам'яті по 128 осередків у кожному банку, тобто в кожному банку є 128 осередків пам'яті по 8 біт (8 біт = один байт). Функція бітів RP0 і RP1, які розташовані в регістрі STATUS, полягає в підключенні того чи іншого банку до мікроконтролера. Мікроконтролер може адресувати одночасно тільки один з банків пам'яті даних. Банк пам'яті даних, який в даний момент може адресувати ядро мікроконтролера, називають активним. Регістри TRIS і PORT знаходяться в різних банках пам'яті даних. Після включення мікроконтролера активним стає нульовою банк пам'яті даних або, іншими словами, нульовий банк пам'яті даних підключається до ядра мікроконтролера. Регістр PORTD знаходиться в нульовому банку пам'яті даних, а регістр TRISD в першому. Тому необхідно встановити біт RP0 в регістрі STATUS для роботи з TRISD. Потім потрібно скинути RP0 для переходу в нульовий банк, щоб працювати з регістром PORTD.

Порядок виконання роботи

Створіть проект, відкомпілюйте програму Project3. Запустіть програму в симуляторі MPLAB IDE.

Покажіть вікно з результатом роботи програми в симуляторі. Продемонструйте результат роботи програми.

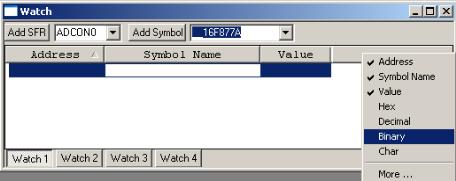

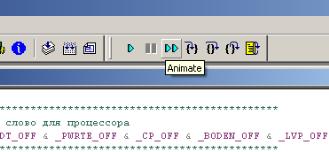

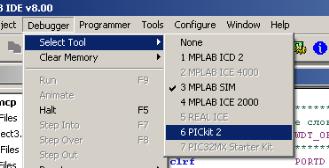

На диску С: \ в папці Projects створіть папку Project3. В цю папку скопіюйте файл Project3 і створіть проект з назвою Project3. Відкомпілюйте програму. Зверніть увагу на повідомлення компілятора (мал. 12.1) про перехід з одного банку пам'яті в інший. Відкрийте вікно Watch. Налаштуйте вікно для відображення значення вмісту регістрів в двійковій формі, для чого наведіть курсор миші на рядок з написами «Address», «Symbol name», «Value», щ ѐ лкніте правою кнопкою миші і оберіть "Binary» (мал. 12.2). Виведіть для спостереження у вікні Watch регістри TRISD і PORTD (мал. 12.3). Виберіть симулятор MPLAB SIM (мал.12. 4). Запустіть програму в режимі Animate (мал. 12.5). Зверніть увагу на зміну вмісту регістрів (мал. 12.6).

Мал. 12.1. Повідомлення компілятора про зміну банків пам'яті даних.

Мал. 12.2. Налаштування вікна Watch для відображення даних в двійковому вигляді.

Мал. 12.3. Вид налаштованого вікна Watch.

Мал. 12.4. Вибір симулятора MPLAB SIM.

Мал. 12.5. Кнопка Animate.

Мал. 12.6. Зміна вмісту регістрів.

Мал. 12.7. Вибір відладчика в середовищі розробки.

Запустіть програму в режимі Animate (рис. 12.9).

Мал. 12.8. Кнопка для програмування лабораторного макета.

Мал. 12. 9. Кнопка для запуску програми на макеті в режимі Animate.

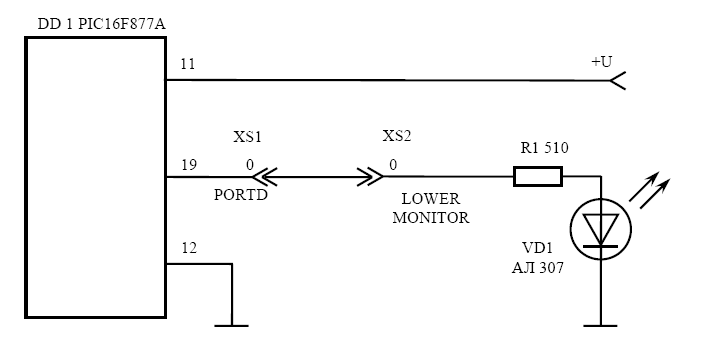

Ця робота виконується як на комп'ютері, в середовищі розробки MPLAB IDE. Принципова електрична схема зображена на мал. 12.10. Схема працює в такий спосіб: на мікроконтроллер подається напруга від блоку живлення. В процесі виконання програми нульовий біт PORTD налаштовується на вихід. Як тільки в регістр PORTD, 0 записується одиниця, на 19 ніжці мікросхеми встановлюється потенціал + U. Через роз'єми і провід потенціал передається на баластний резистор R1, який потрібен для обмеження струму через світлодіод. Послідовно з резистором включений анод світлодіода. Катод світлодіода з'єднаний з нульовим потенціалом. Якщо PORTD, 0 = 1, тоді струм теч ѐ т по ланцюгу + U, 11 ніжка контролера, внутрішній комутатор порту PORTD, 0 ніжка 19, роз'єм PORTD, 0, провід, роз'єм LOWER MONITOR, 0, баластний резистор R1, світлодіод VD1, нульовий потенціал .

Мал. 12.10. Схема електрична принципова.

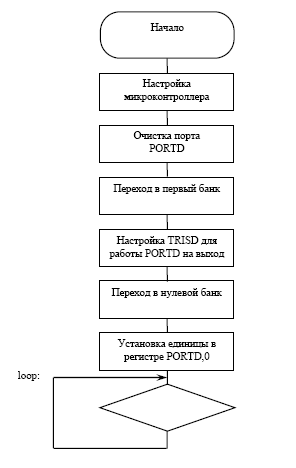

Алгоритм програми зображено на мал. 12.12.

Мал. 12.12. Алгоритм програми Project3.