- •«Устройство для преобразования кода»

- •Введение

- •Задание

- •Структурная схема устройства для помехоустойчивого декодирования

- •Составление тестируемой кодовой комбинации crc – кода (7, 4)

- •Построение декодирующего устройства циклического кода для обнаружения однократных ошибок

- •Проектирование устройства формирования пускового импульса

- •Проектирование устройства деления частоты

- •Проектирование устройства управления

- •Проектирование сдвигового регистра

- •Проектирование дешифратора для управления 7-сегментным индикатором

- •Размещение проекта на кристалле

- •Назначение контактов микросхемы epf10k70rc240-4 для портов проекта

- •Описание процедуры ввода проекта в микросхему epf10k70rc240-4 на учебной плате up2 Educational Kit

- •Определение временных задержек и быстродействия устройства

- •Заключение

- •Список литературы

Определение временных задержек и быстродействия устройства

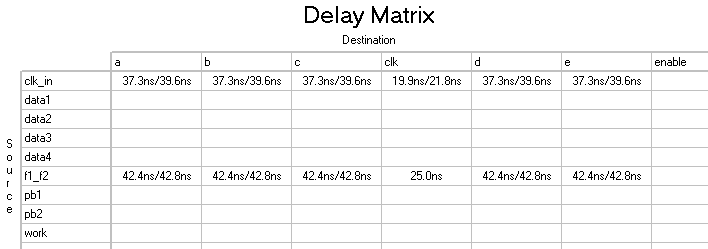

Для определения временных задержек нужно запустить систему временного анализа с помощью команды Timing Analyzer меню MAX+PLUSII. Если при этом через меню Analysis подана команда Delay Matrix, то на экран будет выведено диалоговое окно с матрицей временных задержек сигналов (рис.28), которая заполняется после нажатия кнопки Start.

Рис.28 Матрица задержек сигналов

По матрице временных задержек (Рис.28) можно видеть, что максимальная задержка распространения сигнала составляет 42.4 нс между сигналами выбора режима (f1_f2) и выходами дешифратора a[1..7]. Такая задержка легко объяснима, так как обусловлена временем распространения сигнала на плате.

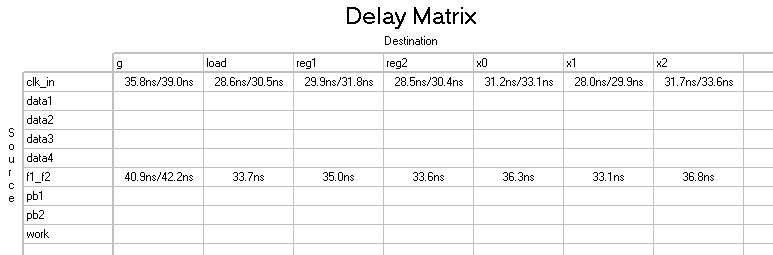

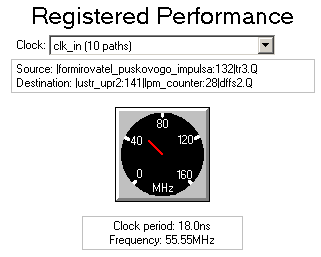

Для определения максимальной тактовой частоты работы проекта с помощью команды Timing Analyzer меню MAX+PLUS II следует выполнить команду Registered Performance меню Analysis. Появиться диалоговое окно Registered Performance, в котором следует нажать кнопку Start. По окончании временного анализа в этом окне будет отображена максимально допустимая частота работы проекта (рис.29).

Рис.29 Определение максимальной тактовой частоты проекта

Для представленного на рис.29 случая максимальная частота равна 52.08МГц. Эта частота может быть повышена, если выбрать более эффективный стиль синтеза – FAST.

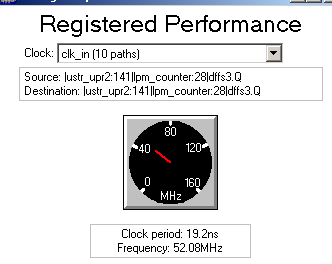

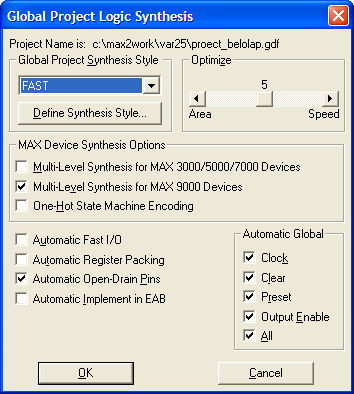

Для этого нужно выполнить команду Global Project Logic Synthesis меню Assign и в строке Global Project Synthesis Style диалогового окна Global Project Logic Synthesis (рис.30) – указать стиль синтеза FAST, подтвердив ввод кнопкой ОК.

Рис.30 Диалоговое окно Global Project Logic Synthesis

После компиляции проекта следует повторить процедуру определения максимальной частоты проекта. В рассматриваем случае использование стиля синтеза FAST позволяет увеличить максимальную тактовую частоту проекта до 55.55 МГц.

Рис.31 Определение максимальной тактовой частоты проекта

Заключение

В результате выполнения курсового проектирования был разработан CRC – декодер с образующим полиномом 1011, преобразующий комбинацию избыточного кода (7,4) в шестиразрядную кодовую комбинацию, предусматривающий обнаружение ошибок в принятой комбинации.

Получены навыки в проектировании устройств на основе библиотечных модулей, простейших модулей логических элементов и триггеров из библиотеки MAX+PLUS II, в виде текстового описания на языке AHDL.

Очень интересным моментом разработки является практическое применение, проверка устройства на работоспособность. Т. е. после введения проекта в микросхему, расположенную на учебной плате UP-2, и ввода тестируемой комбинации, на семисегментных индикаторах должен появляться остаток от деления на образующий полином, который говорит о наличии или отсутствии искажений в принятой комбинации.

Список литературы

А. Н. Гаврилов Проектирование цифровых устройств на ПЛИС: Задания и методические указания к курсовому проекту. Рязань: РГРТУ; 2008.

А. Н. Гаврилов Проектирование цифровых устройств на ПЛИС в графическом редакторе САПР MAX+PLUS II: Методические указания к лабораторным работам. Рязань: РГРТУ; 2005.

В. Б. Стешенко ПЛИС фирмы ALTERA: проектирование устройств обработки сигналов. М.: ДОДЕКА, 2000.

А. Н. Гаврилов Исследование CRC-кода: Методические указания к лабораторной работе. Рязань: РГРТА; 2006.

А. П. Антонов Язык описания цифровых устройств AlteraAHDL: Практический курс Справочник. М.: Радиософт, 1997.