- •«Устройство для преобразования кода»

- •Введение

- •Задание

- •Структурная схема устройства для помехоустойчивого декодирования

- •Составление тестируемой кодовой комбинации crc – кода (7, 4)

- •Построение декодирующего устройства циклического кода для обнаружения однократных ошибок

- •Проектирование устройства формирования пускового импульса

- •Проектирование устройства деления частоты

- •Проектирование устройства управления

- •Проектирование сдвигового регистра

- •Проектирование дешифратора для управления 7-сегментным индикатором

- •Размещение проекта на кристалле

- •Назначение контактов микросхемы epf10k70rc240-4 для портов проекта

- •Описание процедуры ввода проекта в микросхему epf10k70rc240-4 на учебной плате up2 Educational Kit

- •Определение временных задержек и быстродействия устройства

- •Заключение

- •Список литературы

Проектирование устройства управления

Устройство управления должно выполнять следующее:

на интервале с 1 по 4 такт при сигнале Work=0 генерировать сигнал «Общее разрешение», разрешающий ввод и сдвиг части комбинации в сдвиговых регистрах;

на интервале с 1 по 7 такт при сигнале Work=1, то есть при вводе последних символов, генерировать сигнал «Разрешение», позволяющий контролировать процесс декодирования.

Помимо этого в каждом случае происходит формирование импульса разрешающего загрузку в первый регист.

В соответствии с заданием устройство реализовано на основе логических элементов и библиотечных модулей MAX+PLUS II в виде распределителя импульсов библиотечного модуля LPM_COUNTER работающего в режиме дешифратора, четырех RS и одном D – триггерах, формирующих сигнал «Разрешение» (рис. 14):

Рис. 14 Устройство управления

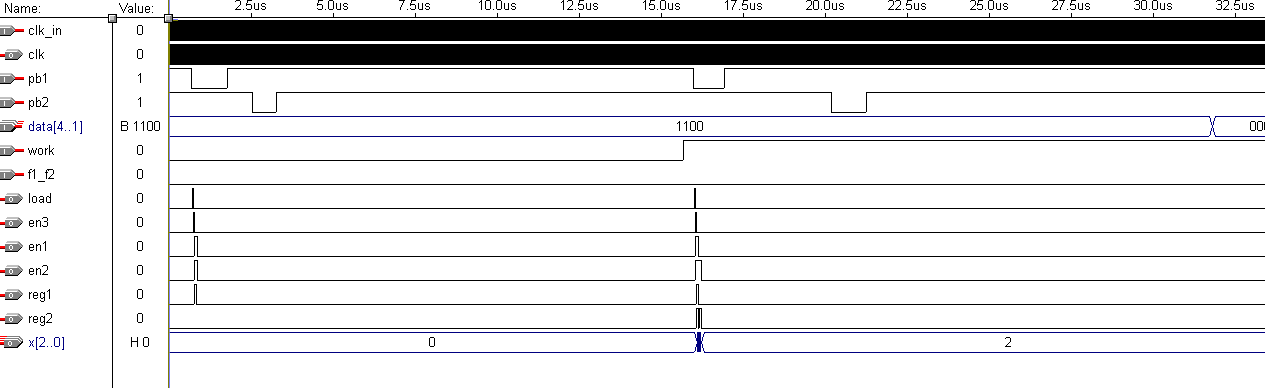

Временные диаграммы моделирования устройства управления представлены на рис. 15.

Рис. 15 Временная диаграмма работы устройства управления

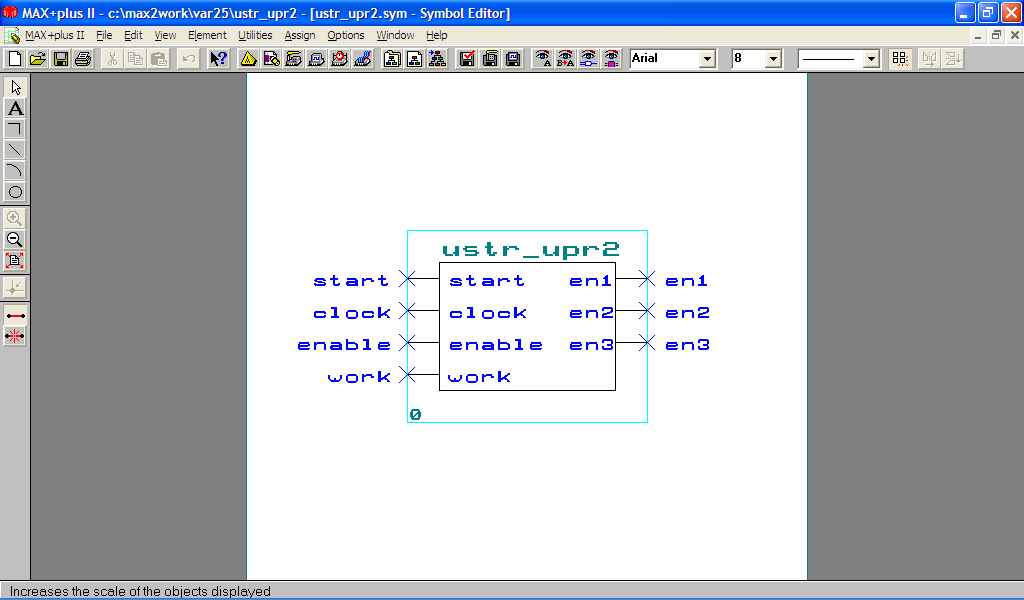

Графический символ устройства управления представлен на рис. 16.

Рис. 16 Графический символ устройства управления

Проектирование сдвигового регистра

Задача сдвигового регистра 1 (см. рис.1) заключается в преобразовании поступающего на него избыточного 7-ми разрядного (n,k) кода из параллельного вида в последовательный. Далее последовательный код поступает на регистр 2.

поступает на регистр 2.

Согласно заданию регистр разработан в виде текстового описания на языке AHDL:

PARAMETERS(WIDTH=4);

ASSERT(WIDTH>0)

REPORT "Value of WIDTH parameter must be grater then %" WIDTH

SEVERITY ERROR;

SUBDESIGN registr_sdvigovyi

(

data[WIDTH..1],load:INPUT=GND;

clock :INPUT;

enable :INPUT=VCC;

q :OUTPUT;

)

VARIABLE

FF[WIDTH..1]:DFFE;

BEGIN

FF[].clk=clock;

FF[].ena=enable;

IF load==0 THEN

FF[].d=(FF[WIDTH-1..1].q,GND);

ELSE

FF[].d=data[];

END IF;

q=FF[WIDTH].q;

END;

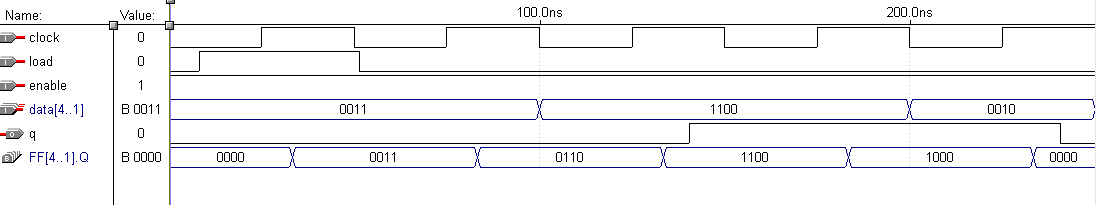

Работа сдвигового регистра 1 проиллюстрирована на рис. 17.

Рис. 17. Временные диаграммы сдвигового регистра 1

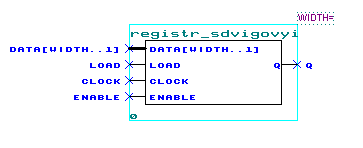

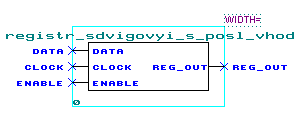

Для дальнейшей работы с проектом сохраним устройство в виде графического символа, представленного на рис. 18.

Рис. 18. Символ сдвигового регистра 1

Задача сдвигового регистра 2 заключается в последовательном приеме и передаче комбинации на декодер.

Согласно заданию регистр разработан в виде текстового описания на языке AHDL:

PARAMETERS(WIDTH=4);

ASSERT(WIDTH>0)

REPORT "Value of WIDTH parameter must be grater then %" WIDTH

SEVERITY ERROR;

SUBDESIGN registr_sdvigovyi_s_posl_vhod

(

data,clock,enable:INPUT;

reg_out :OUTPUT;

)

VARIABLE

FF[WIDTH..1]:DFFE;

BEGIN

FF[].d=(FF[WIDTH-1..1],data);

FF[].clk=clock;

FF[].ena=enable;

reg_out=FF[WIDTH].q;

END;

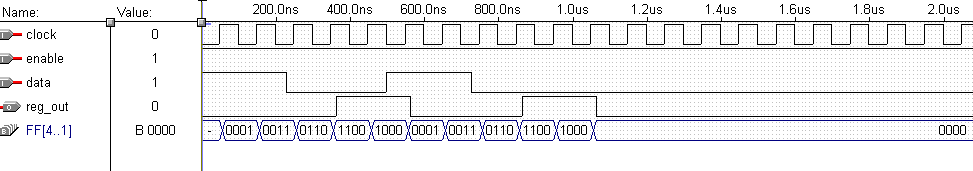

Работа сдвигового регистра 2 проиллюстрирована на рис. 19.

Рис. 19. Временные диаграммы сдвигового регистра 2

Для дальнейшей работы с проектом сохраним устройство в виде графического символа, представленного на рис. 20.

Рис. 20. Символ сдвигового регистра 2

Проектирование дешифратора для управления 7-сегментным индикатором

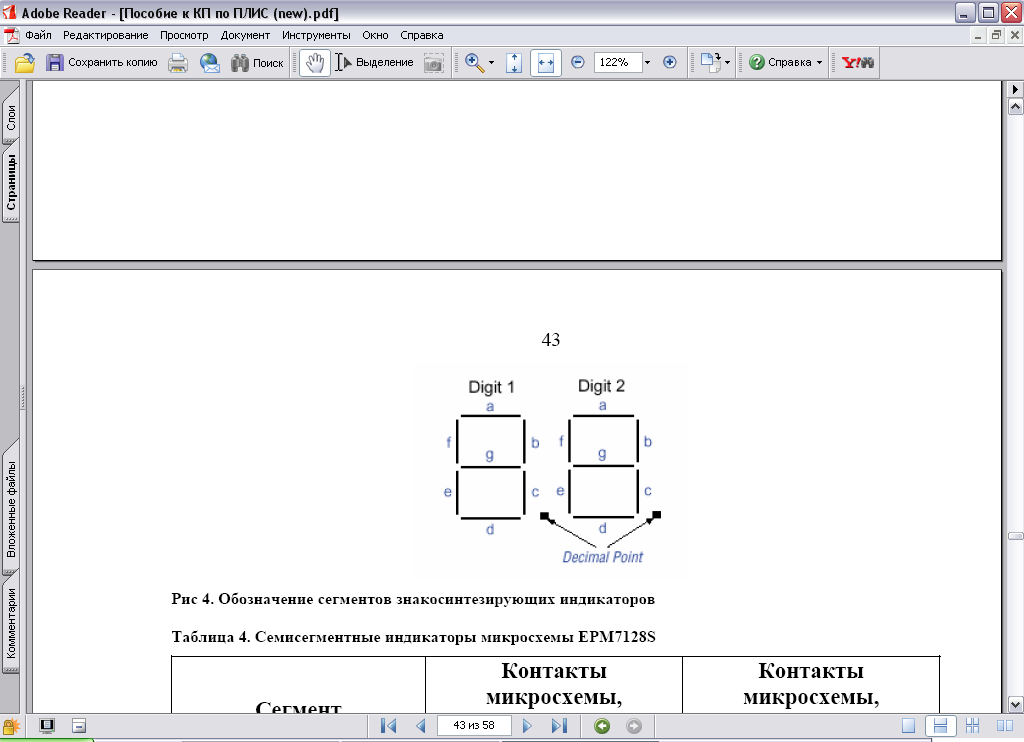

В проекте имеется два дешифратора для управления 7-сегментными индикаторами (рис. 21). Они абсолютно идентичны и предназначены для преобразования 4-битной комбинации для отображения на 7-сегментном индикаторе.

Рис. 21. 7-сегментные индикаторы

В соответствии с заданием дешифратор выполняется в виде текстового описания на языке AHDL:

SUBDESIGN deshifrator

(

i[3..0]: INPUT;

a,b,c,d,e,f,g: OUTPUT;

)

BEGIN

TABLE

i[3..0] => !a,!b,!c,!d,!e,!f,!g;

H"0" => 1,1,1,1,1,1,0;

H"1" => 0,1,1,0,0,0,0;

H"2" => 1,1,0,1,1,0,1;

H"3" => 1,1,1,1,0,0,1;

H"4" => 0,1,1,0,0,1,1;

H"5" => 1,0,1,1,0,1,1;

H"6" => 1,0,1,1,1,1,1;

H"7" => 1,1,1,0,0,0,0;

H"8" => 1,1,1,1,1,1,1;

H"9" => 1,1,1,1,0,1,1;

H"A" => 1,1,1,0,1,1,1;

H"B" => 0,0,1,1,1,1,1;

H"C" => 1,0,0,1,1,1,0;

H"D" => 0,1,1,1,1,0,1;

H"E" => 1,0,0,1,1,1,1;

H"F" => 1,0,0,0,1,1,1;

END TABLE;

END;

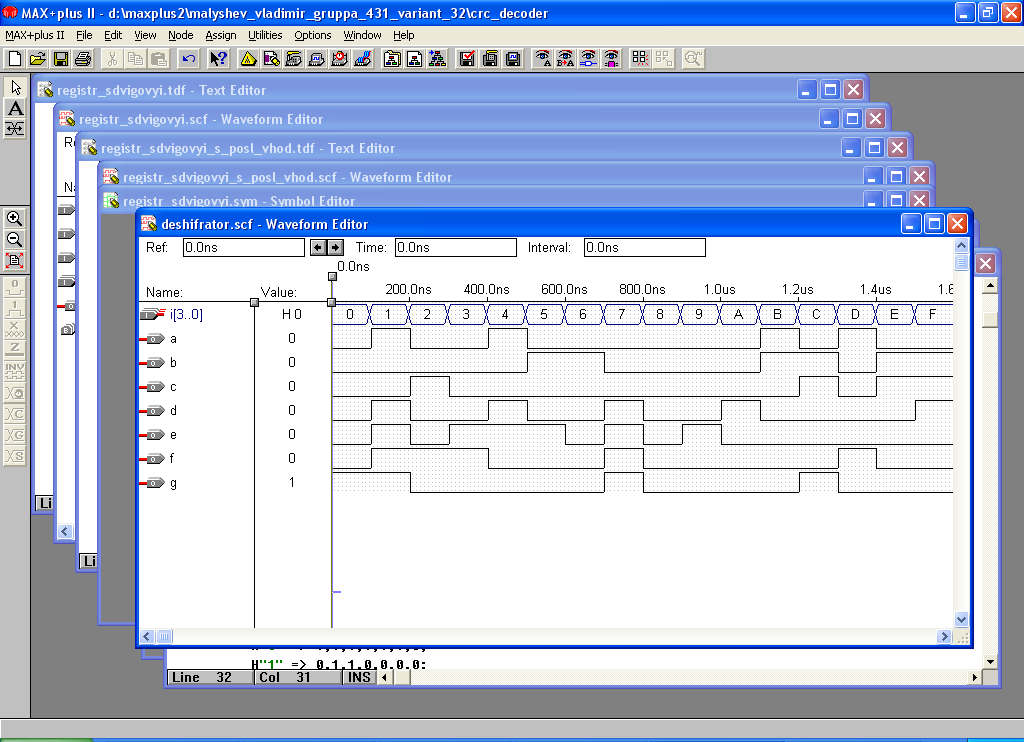

Временные диаграммы полученного устройства приведены на рис. 22.

Рис. 22. Временные диаграммы дешифратора для управления 7-сегментным индикатором

Графический символ дешифратора для управления 7-сегментным индикатором представлен на рис. 23.

Рис.23.

Символ дешифратора для управления

7-сегментным индикатором

Рис.23.

Символ дешифратора для управления

7-сегментным индикатором

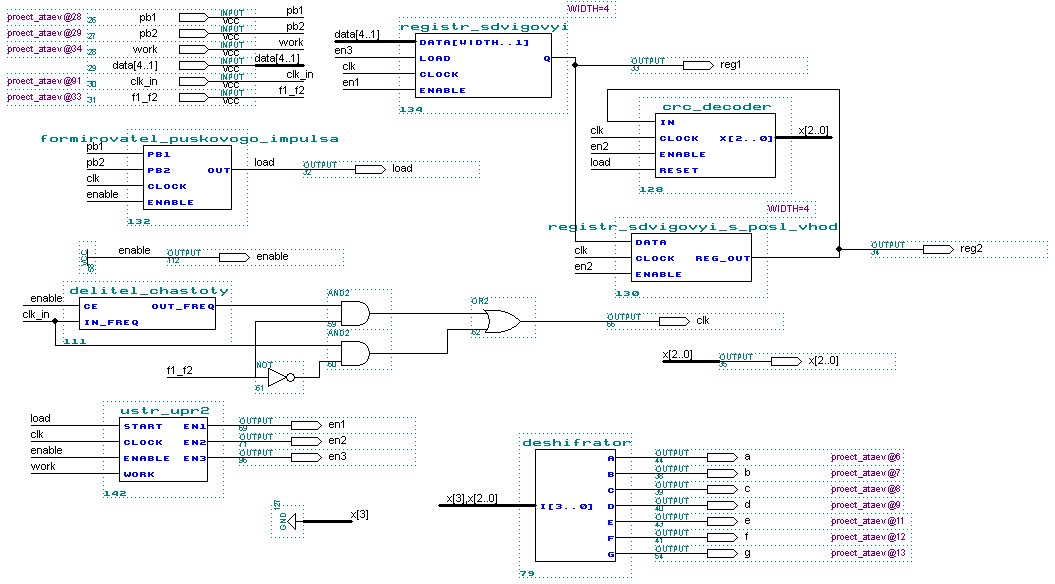

Схема и описание работы проекта

Схема проекта устройства преобразования кода (CRC-кодера) представлена на рис. 24.

Ввод безызбыточной комбинации из 7-ми символов в проект осуществляется в 2 этапа. На первом этапе (сигнал work=0) по нажатию кнопки «Пуск» (pb1) на учебной плате UP2 Educational Kit формируется пусковой импульс. С приходом пускового импульса разрешается первому регистру запись первых 4 символов без избыточной комбинации. После того, как первая часть безбыточной комбинации записана, необходимо нажать кнопку «Сброс» (pb2).

На втором этапе (сигнал work=1) по нажатию кнопки «Пуск» (pb1) на учебной плате UP2 Educational Kit формируется пусковой импульс. С приходом пускового импульса остальные символы загружаются в сдвиговый регистр 1, а затем выдается на CRC-декодер. Устройство управления запускает процесс декодирования, на 7-ом такте работы декодера при work=1 прекращает этот процесс.

Сформированный остаток от деления с выхода CRC-декодера подается на дешифратор для управления 7-сегментным индикатором - параллельно поступают по 4 сформированных в CRC-декодере символа. На 7-сегментном индикаторе учебной платы высвечивается результат, представленный в шестнадцатеричном коде.

Работа устройства протекает под управлением тактовых импульсов ТИ. Предусматривается два режима работы устройства:

с частотой следования тактовых импульсов ТИ, когда простейшие операции в устройстве происходят через интервалы, равные периоду следования ТИ;

с пониженной в 10 раз частотой, когда простейшие операции в схеме происходят в моменты действия каждого 10-ого ТИ.

Режим работы устанавливается логической схемой ЛС1 в устройстве делителя частоты по сигналам с выхода счетчика cout и управляющему сигналу выбора режима f1_f2, принимающему значение логического нуля или единицы. При работе с частотой следования ТИ на выходе логической схемы ЛС1 формируется сигнал «Разрешение» постоянного уровня, и подключаются тактовые импульсы с частотой ТИ. При работе с пониженной в 10 раз частотой ТИ на выходе логической схемы ЛС1 формируется сигнал, разрешающий работу устройства деления частоты.

Рис.22 Схема проекта CRC-декодера (7,4)

На рис.23-24 приведены результаты работы схемы проекта для двух входных комбинаций:

- ошибочной 1100110;

- разрешенной 1100010;

при режиме работы схемы с частотой следования тактовых импульсов.

При моделировании проекта с частотой следования тактовых импульсов (f1_f2=0) на вход подадим комбинацию 1100110 с ошибкой в пятом разряде. При ее делении на образующий полином получаем ненулевой остаток.

Исходя из временных диаграмм работы проекта (Рис. 23), на выходе декодера получаем не нулевую последовательность, что указывает на верность работы проекта при частоте, равной частоте следования тактовых импульсов.

Рассмотрим разрешенную входную комбинацию 1100110. При ее делении на образующий полином получаем нулевой остаток.

Исходя из временных диаграмм работы проекта (Рис. 23), на выходе декодера получаем не нулевую последовательность и нулевую, что указывает на верность работы проекта при частоте, равной частоте следования тактовых импульсов.

Рис.23 Результаты моделирования проекта при работе с частотой следования тактовых импульсов

При моделировании проекта с пониженной в 10 раз частотой (f1_f2=1) на вход подадим все те же комбинации: 1100110 - с ошибкой в пятом разряде и разрешенную - 1100110.

Исходя из временных диаграмм работы проекта, на выходе декодера получаем последовательность, идентичную теоретическим расчетам, что указывает на правильность работы проекта при пониженной в 10 раз частоте.

Рис.24 Результаты моделирования для работы с пониженной в 10 раз частотой

На диаграммах представлены следующие выходные сигналы:

clk_in – входная частота следования тактовых импульсов;

clk – частота следования тактовых импульсов после выбора режима работы;

pb1 – сигнал с переключателя «Старт»;

pb2 - сигнал с переключателя «Стоп»;

data[1..5] – пяти разрядная входная последовательность;

work – сигнал разрешения декодирования;

f1_f2 – сигнал выбора частоты следования тактовых импульсов;

load – сигнал с выхода устройства формирования пусковых импульсов;

en3 – сигнал загрузки первого регистра;

en1 – сигнал разрешения работы первого регистра;

en2 - сигнал разрешения сдвига и декодирования;

reg1 и reg2 – последовательныt выходы первого и второго сдвигового регистра;

x[3..0] – сигнал на выходе декодера (остаток от деления);