- •«Устройство для преобразования кода»

- •Введение

- •Задание

- •Структурная схема устройства для помехоустойчивого декодирования

- •Составление тестируемой кодовой комбинации crc – кода (7, 4)

- •Построение декодирующего устройства циклического кода для обнаружения однократных ошибок

- •Проектирование устройства формирования пускового импульса

- •Проектирование устройства деления частоты

- •Проектирование устройства управления

- •Проектирование сдвигового регистра

- •Проектирование дешифратора для управления 7-сегментным индикатором

- •Размещение проекта на кристалле

- •Назначение контактов микросхемы epf10k70rc240-4 для портов проекта

- •Описание процедуры ввода проекта в микросхему epf10k70rc240-4 на учебной плате up2 Educational Kit

- •Определение временных задержек и быстродействия устройства

- •Заключение

- •Список литературы

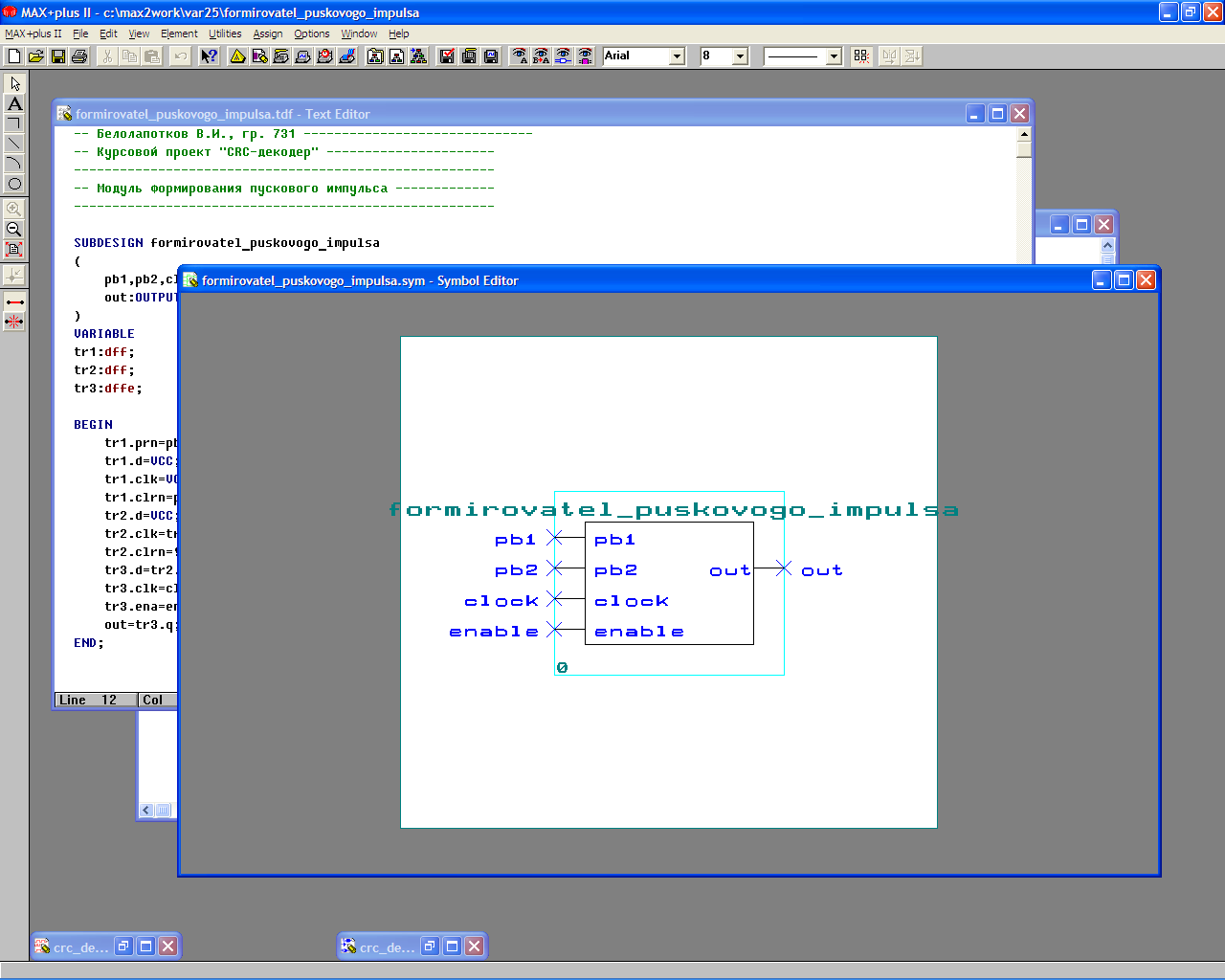

Проектирование устройства формирования пускового импульса

Устройство формирования пускового импульса обеспечивает формирование импульса на выходе «out» при поступлении на вход «pb1» пускового сигнала от кнопки «Пуск» на демонстрационной плате UP-2. Оно также обеспечивает «привязку» выходного импульса к переднему фронту тактовых импульсов, поступающих на вход «clock», а также выполняет защиту от «дребезга» (многократного изменения напряжения на входе «pb1», что не исключено при нажатии кнопки «Пуск»), т.е. реагирует только на первый перепад от единицы к нулю сигнала на входе «pb1». Для повторного формирования импульса на выходе «out» необходимо подать сигнал «Стоп» на вход «pb2», аналогичный сигналу «Пуск» на входе «pb1» (см. рис. 6).

Согласно заданию устройство формирования пускового импульса разработано в виде текстового описания на языке AHDL [2]:

SUBDESIGN formirovatel_puskovogo_impulsa

(

pb1,pb2,clock,enable:INPUT;

out:OUTPUT;

)

VARIABLE

tr1:dff;

tr2:dff;

tr3:dffe;

BEGIN

tr1.prn=pb1;

tr1.d=VCC;

tr1.clk=VCC;

tr1.clrn=pb2;

tr2.d=VCC;

tr2.clk=tr1.q;

tr2.clrn=!out;

tr3.d=tr2.q;

tr3.clk=clock;

tr3.ena=enable;

out=tr3.q;

END;

Рис.9. Временные диаграммы устройства формирования пускового импульса

Первый триггер переходит в единичное состояние, когда на его вход prn со входа «pb1» поступает логический «0». Второй триггер устанавливается в единичное состояние вслед за первым триггером по сигналу с выхода q первого триггера, т.к. на его информационный вход постоянно действует логическая «1» (сигнал VCC). Сигнал с выхода q второго триггера подготавливает третий триггер к записи в него единицы, которая записывается в него по переднему фронту тактового импульса, поступающего по входу clock. Сигнал выхода третьего триггера инвертируется и практически мгновенно устанавливает второй триггер в нулевое состояние, подготавливая запись логического нуля в третий триггер, что осуществляется передним фронтом очередного тактового импульса поступающего по входу clock.

Повторение сигнала на входе «pb1» не меняет состояние первого и второго триггеров, а, следовательно, не приводит к повторному формированию импульса на выходе устройства.

Однако, если первый триггер обнулить по асинхронному входу clrn, то при повторном поступлении сигнала на вход «pb1» работа устройства повторится и на выходе out появиться импульс.

Для дальнейшей работы с проектом сохраним устройство в виде графического символа, представленного на рис.10.

Рис. 10. Символ устройства формирования пускового импульса

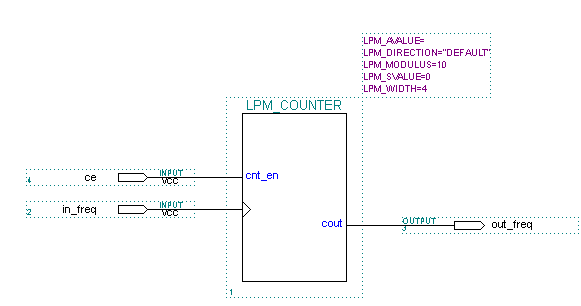

Проектирование устройства деления частоты

Устройство деления частоты построено на основе параметризированного модуля счетчика LPM_COUNTER, в котором предусмотрена возможность счета по модулю k (10 – по заданию). В этом режиме счетчик может считать только до k-1 (9), после чего цикл его работы повторяется. При этом на выходе переполнения cout (out_freq) формируется периодическая последовательность импульсов, длительность которых равна периоду следования входных импульсов clock (in_freq), а частота уменьшается в k (10) раз. Эта периодическая последовательность импульсов формируется на выходе только тогда, когда на вход разрешения работы устройства еe подан сигнал логической единицы.

Рис.11. Устройство деления частоты

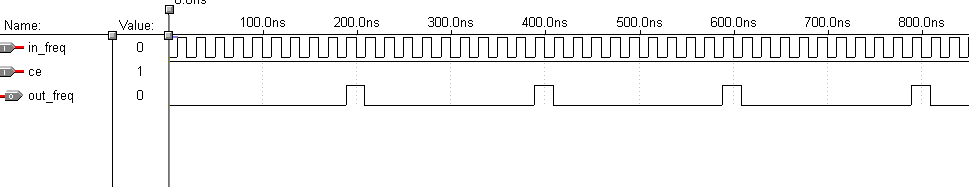

Рис. 12. Временные диаграммы устройства деления частоты

Как следует из временных диаграмм (рис. 12) на выходе устройства out_freq формируется синфазная с входной последовательностью in_freq периодическая последовательность импульсов, длительность которых равна периоду следования входных импульсов in_freq, а частота уменьшается в 10 раз.

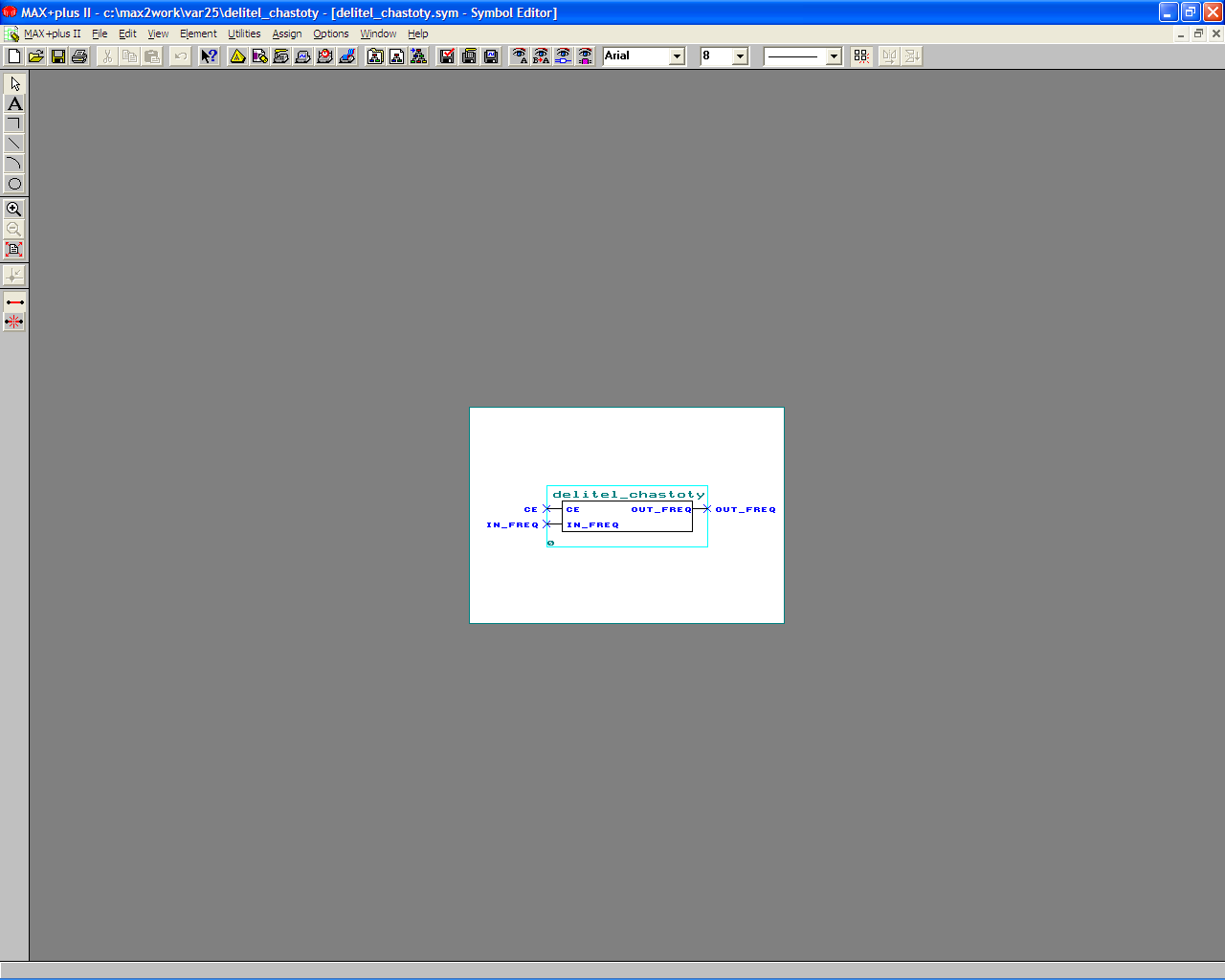

Для дальнейшей работы с проектом сохраним устройство в виде графического символа, представленного на рис. 13.

Рис. 13. Символ устройства деления частоты