- •Міністерство освіти і науки україни, молоді та сторту україни тернопільський національний технічний університет імені івана пулюя

- •Лабораторна робота № 1

- •Короткі теоретичні відомості

- •1 Загальні завваги

- •2 Опис програми

- •2.1 Опис меню програми

- •Опис кнопок панелей інструментів

- •Створення схеми

- •Порядок виконання

- •Де р0пот-потужність,яка споживається схемою в стані 0”, р1пот-потужність,яка споживається схемою в стані “1”.

- •Порядок виконання

- •Контрольні питання

- •Література

- •Додаток 1

- •Додаток 3

- •Лабораторна робота № 3

- •Короткі теоретичні відомості

- •Порядок виконання

- •Контрольні питання

- •Література

- •Параметри інтегральних мікросхем регістрів

- •Лабораторна робота № 4

- •Короткі теоретичні відомості

- •Хід роботи

- •Контрольні запитання

- •6.Список викоистаної літератури

- •Лабораторна робота № 9

- •Короткі теоретичні відомості

- •Порядок виконання

- •Контрольні питання

- •Література

Порядок виконання

1. Дослідження особливостей функціонування логічних елементів ДД1 - ДД4 і визначення їх функціонального призначення.

2. Задаючи різні комбінації вхідних логічних сигналів, визначити значення вихідного сигналу і за результатами вимірів заповнити таблиці істинності для кожного елемента ДД1 - ДД4 у лабораторному звіті.

3. За результатами вимірів визначити функціональне призначення елементів і проставити їхнє позначення на схемі в лабораторному звіті.

Зміст звіту

1. Назва і ціль роботи

2. Схема досліджуваного пристрою

3. Таблиці.

4. Висновки по роботі

Контрольні питання

1. Якими значеннями перемінних оперує алгебра логіки?

2. Основні форми завдання ФАЛ

3. Вид основних логічних функцій в алгебраїчній формі

4. Що таке “логічний елемент”?

5. Які логічні функції виконують елементи Пірса і Шеффера?

6. Чим визначається число можливих комбінацій вхідних перемінних для довільного логічного елемента?

Література

Електротехніка й основи електроніки. О.А.Антонова, О.П. Глудкин і ін., Під ред. проф. О.П. Глудкина. - М.: Вища школа, 1993.

Рябенький В.М., Жуйков В.Я., Гулий В.Д. Цифрова схемотехніка:Навчальний посібник Львів:Новий Світ-2000,2009

Под ред. В.П.Боровского Справочник по схемотехнике для радіолюбителя К.: Тэхника, 1989

Додаток 1

-

Функція

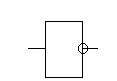

Графічне позначення

Європейське

Американське

АБО

І

НЕ

І-НЕ

АБО-НЕ

Додаток 2

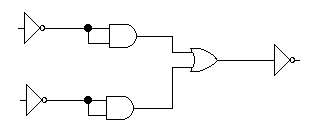

Схема № 1

Схема № 2

Схема № 3

Схема № 4

Додаток 3

Тип |

Аналог |

Функціональне призначення |

SN7400 |

К155ЛА3 |

Чотири логічних елементи “2І-НЕ” |

SN7401 |

К155ЛА8 |

Чотири елементи “2І-НЕ” |

SN7402 |

К155ЛЕ1 |

Чотири елементи “2АБО-НЕ” |

SN7404 |

К155ЛН1 |

Шість інверторів |

SN7408 |

К155ЛИ1 |

Чотири елементи “2І” |

SN7410 |

К155ЛА4 |

Три елементи “3І-НЕ” |

SN7432 |

К155ЛЛ1 |

Чотири елементи “2АБО” |

Лабораторна робота № 3

Тема:

Мета роботи: Навчитись створювати регістри зсуву на базі тригерів.

Короткі теоретичні відомості

Регістрами називають вузли, які призначені для зберігання двійкових чисел та їх зсуву на потрібну кількість розрядів. Вони складаються з однакових елементів пам’яті і комбінаційної керуючої схеми. В кожному елементі пам’яті може зберігатися лише один розряд двійкового коду. Тому цей елемент разом з відповідною частотою і комбінаційною схемою називається розрядом регістра.

Ввід в регістр багаторозрядного числа може бути одночасно паралельним заповненням всіх розрядів, так послідовного (по розрядах). Вивід інформації може бути паралельним і послідовним. Залежно від способів вводу і виводу розрізняють: паралельні, послідовні і комбіновані регістри. В паралельних регістрах ввід і вивід числа здійснюється паралельно. Такі регістри називають регістрами пам’яті і використовують на базі Т- або RS-тригерів.

Регістри зсуву. Тригерним регістром зсуву називають сукупність тригерів з визначеними зв'язками між ними, при яких вони діють як єдиний пристрій. У регістрах зсуву організація цих зв'язків така, що при подачі тактового імпульсу, загального для всіх тригерів, вихідний стан кожного тригера зрушується в сусідній. У залежності від організації зв'язків цей зсув може відбуватися вправо чи вліво :

Введення інформації в регістр може виконуватися різними способами, однак найбільш часто використовують рівнобіжне чи послідовне введення, при яких введення двійкового числа здійснюється одночасно в усі розряди регістра чи послідовно в часі по окремих розрядах. У лічильниках імпульсів знаходять застосування регістри зсуву з послідовним вводом і виводом і зі зрушенням вправо. На рисунку 1 а приведена схема чотирьохрозрядного регістра зсуву, виконаного на T тригерах. У цій схемі кожен вихід Q тригера з'єднаний із входом S наступного розряду, а кожен вихід Q — із входом R. Тактові входи всіх тригерів з'єднані разом, і надходження сигналу синхронізації здійснюється одним загальним імпульсом через логічний елемент І-НІ (DD1). Стан першого тригера визначається вхідними сигналами на входах XI і Х2 логічного елемента І-НІ (DD5). На вхід XI подається поточна інформація, а на вхід Х2 сигнал дозволу її передачі. Логічний елемент НІ (DD6) використовується для інвертування вхідного сигналу, що подається на вхід S.

На рисунку 1 б приведені тимчасові діаграми вихідних сигналів тригерів.

Інтегральні мікросхеми регістрів зсуву бувають реверсивними, тобто виконуючими зсув у будь-якому напрямку: вправо чи вліво. Напрямок зсуву визначається значенням керуючого сигналу. Регістри зсуву застосовують як запам'ятовуючі пристрої, як перетворювачі послідовного коду в рівнобіжний, як пристрої затримки і лічильників імпульсів.