- •Міністерство освіти і науки україни, молоді та сторту україни тернопільський національний технічний університет імені івана пулюя

- •Лабораторна робота № 1

- •Короткі теоретичні відомості

- •1 Загальні завваги

- •2 Опис програми

- •2.1 Опис меню програми

- •Опис кнопок панелей інструментів

- •Створення схеми

- •Порядок виконання

- •Де р0пот-потужність,яка споживається схемою в стані 0”, р1пот-потужність,яка споживається схемою в стані “1”.

- •Порядок виконання

- •Контрольні питання

- •Література

- •Додаток 1

- •Додаток 3

- •Лабораторна робота № 3

- •Короткі теоретичні відомості

- •Порядок виконання

- •Контрольні питання

- •Література

- •Параметри інтегральних мікросхем регістрів

- •Лабораторна робота № 4

- •Короткі теоретичні відомості

- •Хід роботи

- •Контрольні запитання

- •6.Список викоистаної літератури

- •Лабораторна робота № 9

- •Короткі теоретичні відомості

- •Порядок виконання

- •Контрольні питання

- •Література

Де р0пот-потужність,яка споживається схемою в стані 0”, р1пот-потужність,яка споживається схемою в стані “1”.

Потужність, яка використовується цими інтегральними мікросхемами в момент перехідних процесів , не перевищує потужності, спожитої в одному із логічних елементів.

Логічні елементи з наростаючим споживанням в динамічному режимі крім статичної потужності характеризуються потужністю, яка споживається на максимальній частоті переключення, коли на багато зростають струми в ланцюгах живлення. Прикладом таких схем являються КМОН ІС, які використовують мікроамперні струми живлення, якщо нема переключаючих сигналів. Допустима межа статичної завадостійкості логічного елемента обмежує рівень випадкової напруги, яка може бути присутня на його вході без небезпеки фальшивого спрацювання.

В статичному режимі розрізняють статичну завадостійкість по низькому рівні (U0пом) і по високому (U1пом ). Значення цих величин U0пом та U1пом визначають за допомогою передаточних характеристик (рис.2). Як видно з рисунку параметр U0пом визначається як різниця мінімальної напруги високого рівня ( U1 вх mіn ) і напруги в точці перегинання на верхній кривій (точка В). Параметр U0пом визначається як різниця напруг в точці перегинання нижньої кривої (точка А) і максимальної напруги низького рівня (U1 вх max).

Для більш повної оцінки завадостійкості схеми разом із статичною необхідно враховувати динамічну завадостійкість. Завадостійкість в динамічному режимі залежить від подовженості, амплітуди, і форми сигналу завади, а також від значення статистичної завадостійкості і швидкості переключення логічного елемента.

Коефіцієнт розгалуження по входу (навантажувальна здатність) Краз визначає число входів аналогічних елементів, яке може бути підключено без порушення роботи до виходу попереднього логічного елемента. Із збільшенням навантажувальної здатності розширюються можливості використання цифрових інтегральних мікросхем, зменшується кількість корпусів в розроблюваній цифровій установці. Проте при цьому погіршуються деякі параметри цифрових інтегральних мікросхем: понижується швидкодія, і завадостійкість і збільшується використання напруги.

Математична основа цифрової електроніки

Математичною основою цифрової електроніки й обчислювальної техніки є алгебра логіки або Булева алгебра (по імені англійського математика Джона Буля).

У булевій алгебрі незалежні змінні чи аргументи (X) приймають тільки два значення: 0 чи 1. Залежні змінні чи функції (Y) також можуть приймати тільки одне з двох значень: 0 чи 1. Функція алгебри логіки (ФАЛ) представляється у виді:

Y = F (X1; X2; X3 ... XN ).

Дана форма завдання ФАЛ називається алгебраїчною.

Основними логічними функціями є:

- логічне заперечення (інверсія)

Y

=

![]() ;

;

- логічне додавання (диз’юнкція)

Y = X1 + X2 чи Y = X1 V X2 ;

- логічне множення (кон’юнкція)

Y = X1 X2 чи Y = X1 X2 .

До більш складних функцій алгебри логіки відносяться:

- функція рівнозначності (еквівалентності)

Y

= X1

X2

+

![]() чи Y = X1

~

X2

;

чи Y = X1

~

X2

;

- функція нерівнозначності (додавання по модулі два)

Y

= X1

![]() +

+

![]()

X2

чи Y = X1

X2

чи Y = X1

![]() X2

;

X2

;

- функція Пірса (логічне додавання з запереченням)

Y

=

![]() ;

;

- функція Шеффера (логічне множення з запереченням)

Y

=

![]() ;

;

Для булевої алгебри справедливі наступні закони і правила:

- розподільний закон

X1 (X2 + X3) = X1 X2 + X1 X3 ,

X1 + X2 X3 = (X1 + X2) (X1 + X3) ;

- правило повторення

X X = X , X + X = X ;

- правило заперечення

X

![]() = 0 , X +

= 1 ;

= 0 , X +

= 1 ;

- теорема де Моргана

=

,

=

![]() ;

;

- тотожності

X 1 = X , X + 0 = X , X 0 = 0 , X + 1 = 1.

Схеми, що реалізують логічні функції, називаються логічними елементами. Основні логічні елементи мають, як правило, один вихід (Y) і декілька входів, число яких рівне числу аргументів (X1;X2;X3 ... XN ). На електричних схемах логічні елементи позначаються у виді прямокутників з висновками для вхідних (ліворуч) і вихідних (праворуч) перемінних. Усередині прямокутника зображується символ, що указує функціональне призначення елемента. Графічне позначення цих елементів приведене в додатку 1.

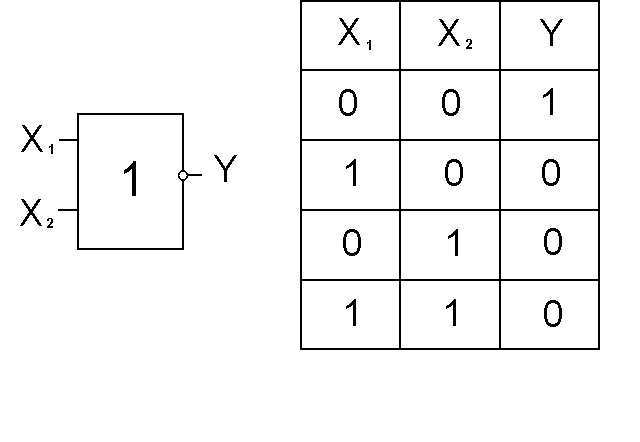

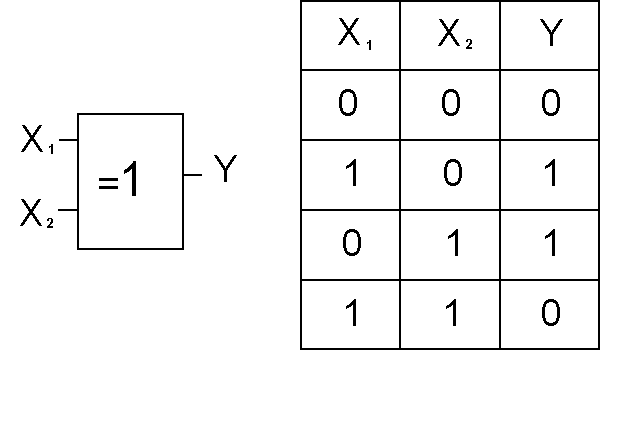

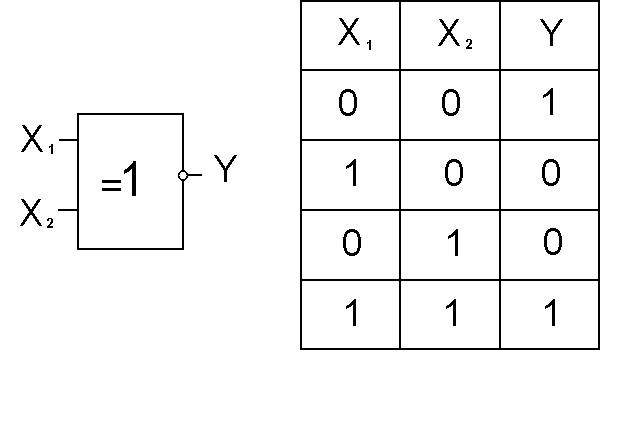

На рисунках представлені логічні елементи, що реалізують розглянуті функції. Там же представлені так називані таблиці станів або таблиці істинності, що описують відповідні логічні функції в двійковому коді у виді станів вхідних і вихідних змінних. Таблиця істинності є також табличним методом задання ФАЛ.

На рис.3 представлений елемент “НІ”, що реалізує функцію логічного заперечення Y = .

Рисунок 3

Елемент “АБО” (рис.4) і елемент “І” (рис.5) реалізують функції логічного додавання і логічного множення відповідно.

Рисунок 4 Рисунок 5

Функції Пірса і функції Шиффера реалізуються за допомогою елементів “АБО-НІ” і “І-НІ”, представлених на рис.6 і рис. 7 відповідно.

Рисунок 6 Рисунок 7

Елемент Пірса можна представити у виді послідовного з'єднання елемента “АБО” і елемента “НІ” (рис.8), а елемент Шиффера - у виді послідовного з'єднання елемента “І” і елемента “НІ” (рис.9).

![]()

Рисунок 8 Рисунок 9

На рис.10 і рис.11 представлені елементи “ Виключаючого АБО” і “ Виключаючого АБО - НІ”, що реалізують функції нерівнозначності і нерівнозначності з запереченням відповідно.

Рисунок 10 Рисунок 11

Логічні елементи, що реалізують операції кон’юнкції, диз’юнкції, функції Пірса і Шиффера, можуть бути, у загальному випадку, n - вхідні. Так, наприклад, логічний елемент із трьома входами, що реалізує функцію Пірса, має вид, представлений на рисунку.

Рисунок 12

У таблиці істинності є вісім значень вихідний змінних Y. Ця кількість визначається числом можливих комбінацій вхідних змінних N, що, у загальному випадку, рівно: N = 2 n , де n - число вхідних змінних.

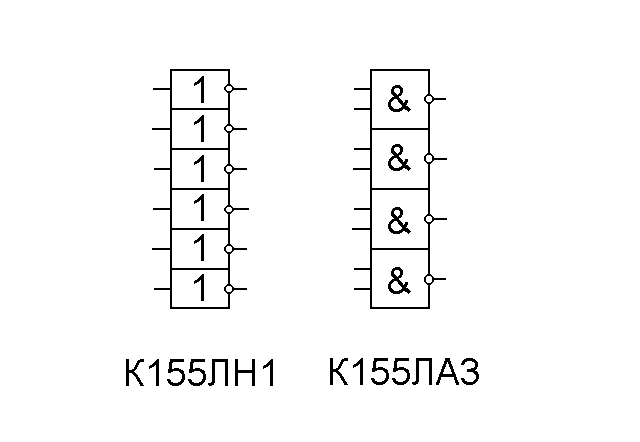

Логічні елементи використовуються для побудови інтегральних мікросхем, що виконують різні логічні й арифметичні операції маючи різне функціональне призначення. Мікросхеми типу К155ЛН1 і К155ЛА3, наприклад, мають у своєму складі шість інверторів і чотири елементи Шиффера відповідно (рис.13), а мікросхема К155ЛР1 містить елементи різного виду (рис.14).

Рисунок 13 Рисунок 14

ФАЛ будь-якої складності можна реалізувати за допомогою зазначених логічних елементів. Як приклад розглянемо ФАЛ, задану в алгебраїчній формі, у виді:

![]() .

.

Спростимо дану ФАЛ, використовуючи вищенаведені правила. Одержимо:

Проведена операція зветься мінімізації ФАЛ і служить для полегшення процедури побудови функціональної схеми відповідного цифрового пристрою.

Функціональна схема пристрою, що реалізує розглянуту ФАЛ, представлена на рис. 15.

Рисунок 15

Слід зазначити, що отримана після перетворень функція не є цілком мінімізованою. Повна мінімізація функції проводиться в процесі виконання лабораторної роботи.

Опис об’єкта і засобів дослідження

На рисунку 16. Преставлено підключення досліджувальних схем під час моделювання.

Рисунок 16

Досліджувана в лабораторній роботі структурна схема представлена у додатку 2.

Таблиця аналогів мікросхем ТТЛ логіки приставлена в додатку 3.

Для мікросхем даної серії логічній одиниці відповідає напруга U1 = (2,4 5,0) B, а логічному нулю - U0 = (0 0,8) В.

Логічні “0” і “1” на вході елементів задаються за допомогою кнопок.

Повне графічне зображення кнопок даного типу (так званих “кнопок з фіксацією”) показано тільки для кнопки SA1.

При натиснутій кнопці вхід елементів через резистор R1 підключається до джерела з напругою 5В. При цьому на вході елементів буде діяти напруга U1 , що відповідає подачі на мікросхеми логічної одиниці. При віджатій кнопці вхід елемента буде з'єднаний із шиною, що знаходиться під потенціалом землі, що відповідає подачі на висновок мікросхеми логічного нуля U0.