- •Міністерство освіти і науки, молоді та спорту україни

- •Методичний посібник

- •1 Пояснювальна записка

- •2 Вимоги до оформлення звіту

- •3 Інструкція з техніки безпеки

- •Дослідження диференційного підсилювача

- •4 Основні теоретичні положення

- •5 Послідовність виконання роботи

- •7 Контрольні питання

- •8 Література

- •Дослідження роботи диференціатора та інтегратора на операційному підсилювачі

- •4 Основні теоретичні положення

- •5 Послідовність виконання роботи

- •7 Контрольні питання

- •8 Література

- •Дослідження роботи мультивібратора на операційному підсилювачі

- •4 Основні теоретичні положення

- •5 Послідовність виконання роботи

- •7 Контрольні питання

- •Дослідження роботи транзисторно-транзисторної логіки (ттл)

- •3 Схема дослідження

- •4 Основні теоретичні положення

- •5 Послідовність виконання роботи

- •7 Контрольні питання

- •8 Література

- •Дослідження схем тригерів

- •4 Основні теоретичні положення

- •5 Послідовність виконання роботи

- •7 Контрольні питання

- •8 Література

- •Дослідження роботи лічильника

- •4 Основні теоретичні положення

- •5 Послідовність виконання роботи

- •7 Контрольні питання

- •8 Література

- •Список літератури

7 Контрольні питання

Назвіть основні типи логік.

Назвіть основні параметри інтегральних мікросхем.

Що таке багатоемітерний транзистор?

Назвіть переваги ТТЛ.

8 Література

8.1 Калабеков Б.А. Цифровые устройства и микропроцессорные системы.- М.: Горячая линия - Телеком, 2002. – с. 25-28.

8.2 Матвієнко М.П., Розен В.П., Комп'ютерна схемотехніка. Навчальний посібник. – К.: Видавництво Ліра-К, 2012.- 192 с.

8.3 Рябенький В.М. Жуйков В.Я. Цифрова схемотехніка. –Львів: Новий світ-2009.-736 с.Джонс М.Х. Электроника-Практический курс. М.: Техносфера, 2006. – 512 с.

Лабораторна робота № 5

Дослідження схем тригерів

1 Мета роботи: дослідити роботу асинхронного RS-тригера, синхронного RS-тригера та інформаційного D-тригера. Дослідити роботу JK-тригера з динамічним входом керування.

2 Апаратура та прилади: ПЕОМ, програма Electronics Workbench

3 Схема дослідження:

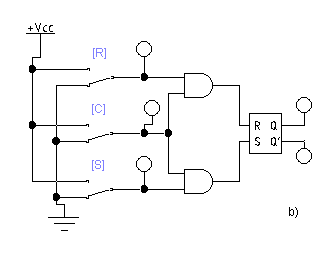

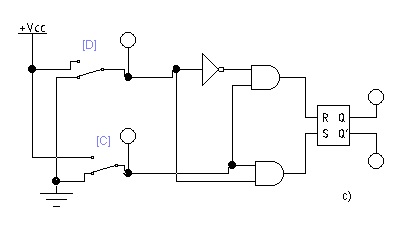

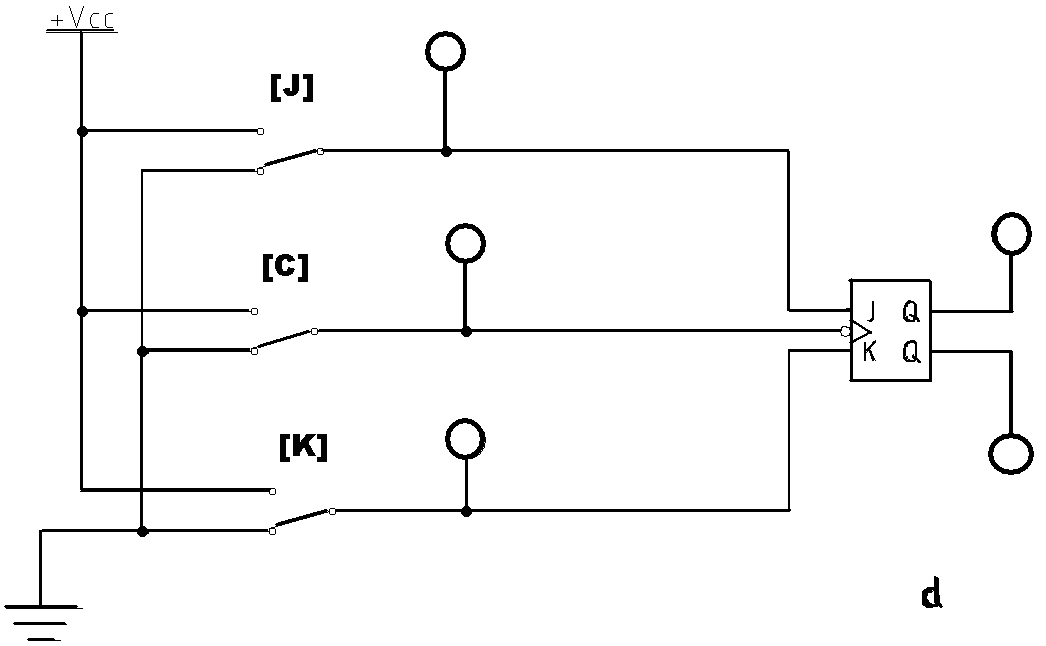

Рисунок

1 – Схеми дослідження асинхронного

RS-тригера (а), синхронного RS-тригера (б),

інформаційного D-тригера (с) та

універсального JK-тригера

(d)

Рисунок

1 – Схеми дослідження асинхронного

RS-тригера (а), синхронного RS-тригера (б),

інформаційного D-тригера (с) та

універсального JK-тригера

(d)

4 Основні теоретичні положення

Основою послідовнісних логічних пристроїв (пристроїв з пам’яттю) є тригери. Елементарний об’єм інформації, яка запам’ятовується, дорівнює 1 біту.

Тригер – це послідовнісний пристрій, призначений для запису і зберігання значення однорозрядної двійкової інформації.

За способом запису інформації тригери поділяють на асинхронні та синхронні.

Асинхронний тригер має лише інформаційні входи, сигнали на яких визначають стан тригера з моменту їх появи.

Синхронний тригер додатково має синхронізуючий (тактовий) вхід. Сигнали на інформаційних входах діють тільки під час синхронізуючого сигналу.

RS-тригер має два

інформаційних входи: S – роздільний

вхід установлення в стан логічної 1; R –

роздільний вхід установлення в стан

логічного 0; і два виходи: прямий

![]() і інверсний

і інверсний

![]() .

.

На входи R, S, D, С, за допомогою відповідних перемикачів подаються потенціальні рівні логічної одиниці (+5В) або логічного нуля (┴). Контроль подачі вхідних логічних змінних та появи рівня логічної одиниці на виході здійснюється за допомогою індикаторів .

Синхронний RSС-тригер (рис.1б) складається з асинхронного RS-тригера, на входах якого включені два логічні елементи І (&), завдяки яким тригер перемикається лише тоді, коли на входи І діють одночасно інформаційний сигнал з входу R або S і сигнал з синхронізуючого входу С, що мають високий рівень.

При С=0 інформаційні входи тригера блоковані і він зберігає попередній стан Qі.

D-тригер (рис.1с) є синхронним тригером і має один інформаційний і один синхронізуючий вхід. Його схема будується на основі RSС-тригера. Відмінність складається в тому, що на вхід R подається інвертований інформаційний сигнал.

Універсальний JK-тригер аналогічно RSC-тригеру має роздільні входи встановлення виходу в нуль або одиницю, але у нього відсутні заборонені комбінації по інформаційним входам J і K. Найчастіше JK-тригер працює з динамічним сигналом синхронізації, тобто спрацьовує за фронтом або зрізом. В схемі дослідження спрацювання JK-тригера здійснюється за зрізом сигнала керування.