- •Глава 1

- •1.1. Обобщенное описание задачи

- •1.2. Объекты управления

- •1.3. Принципы цифрового управления

- •1.4. Математические модели цифровых систем управления

- •1.5. Вычислительные методы решения задач

- •4. Ос рв с полным сервисом.

- •Глава 3

- •Глава 4

- •4.3. Нанокомпьютеры

- •5Л. Микропроцессорная система управления электродвигателем

- •5.2. Нечеткая адаптивная система

- •Получим выражение для уравнения движения атс. Для разложим в ряд Тейлора и используем линейные члены:

- •При малых отклонениях (в установившемся режиме)

- •Представим это выражение в безразмерном виде:

- •Поэтому передаточная функция атс при управлении скоростью с помощью механизма топливоподачи будет

- •5.3. Нечеткая система управления

- •Структурная схема системы управления атс будет выглядеть, как показано на рис. 5.43.

- •Окончание табл. 5.3

- •5.4. Управляющий вычислительный комплекс радиотелескопа

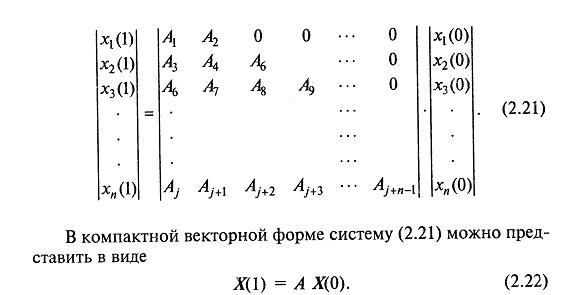

1.5. Вычислительные методы решения задач

оптимального управления

При синтезе систем управления, прежде всего возникает вопрос о нахождении наилучшего в том или ином смысле или оптимального управления объектом или процессом. Речь может идти, например, об оптимальности в смысле быстродействия, т. е. достижении цели за кратчайшее время или, например, о достижении цели с минимальной ошибкой и т. д.

Впервые математически сформулированные эти вопросы являлись задачами вариационного исчисления, которое и обязано им своим возникновением [12]. В классическом вариационном исчислении нет, однако, решения целого ряда вариационных задач, важных для современной техники. Поэтому стали появляться другие методы, например, объединенные одним общим математическим приемом, который называется принципом максимума [13]. В настоящее время, в связи с бурным развитием средств вычислительной техники, наиболее популярны различные вычислительные методы оптимизации, например, методы динамического программирования [14], математического программирования [8, 15] или так называемые генетические алгоритмы [16].

Наибольшее число методов оптимального управления рассматривает такие процессы управления, каждый из которых мажет быть описан системой обыкновенных дифференциальных уравнений:

dxi/dt

=

fi(x1

х2

,..хn,

![]() i =

1, 2, …

n,

(1.33)

i =

1, 2, …

n,

(1.33)

где

x1

х2

,..хn

— величины,

характеризующие процесс, т.е. фазовые

координаты объекта управления,

определяющие его состояние в каждый

момент времени

t,

а ,

![]() —

параметры управления (в том числе и

настраиваемые параметры регуляторов),

определяющие ход процесса.

—

параметры управления (в том числе и

настраиваемые параметры регуляторов),

определяющие ход процесса.

Для

того чтобы ход управляемого процесса

был определен на некотором отрезке

времени ![]() достаточно,

чтобы на этом отрезке времени были

заданы как функции времени параметры

управления:

достаточно,

чтобы на этом отрезке времени были

заданы как функции времени параметры

управления:

![]() (1.34)

(1.34)

Тогда при заданных начальных условиях

![]() (1.35)

(1.35)

решение системы (1.33) определяется однозначно. Подлежащая решению вариационная задача, связанная с управляемым процессом (1.33), заключается в следующем.

Рассматривается интегральный функционал:

где

![]() — заданная функция.

— заданная функция.

Для каждого управления (1.34), заданного на некотором отрезке времени t0 < t < tt однозначно определяется ход управляемого процесса, и интеграл (1.36) принимает определенное значение.

Допустим, что существует управление (1.34), переводящее объект управления из заданного начального фазового состояния (1.35) в предписанное конечное фазовое состояние:

xi(t1)= хi1 , i = 1, 2, ..., п. (1.37)

Требуется отыскать управление

uj(t), j = 1, 2, ..., т, (1.38)

которое осуществит перевод объекта управления из состояния (1.35) в состояние (1.37) таким образом, чтобы функционал (1.36) имел минимальное значение. При этом моменты времени t0, t1 не фиксируются, а требуется только, чтобы в начальный момент времени объект находился в состоянии (1.35), а в конечный — в состоянии (1.37) и чтобы функционал (1.36) достигал минимума (возможен случай, когда t0, не фиксированы).

В

технических задачах параметры управления

не могут принимать любые произвольные

значения. Поэтому для любой точки,

характеризующей текущее значение

управления, должно выполняться

условие (u1

..., um)![]() U.

Причем выбор множества

U

должен отражать

специфику объекта управления. Во многих

технических задачах это множество

замкнуто. Введение подобных ограничений

приводит к неклассическим задачам

вариационного исчисления, которые лучше

решать вычислительными методами.

U.

Причем выбор множества

U

должен отражать

специфику объекта управления. Во многих

технических задачах это множество

замкнуто. Введение подобных ограничений

приводит к неклассическим задачам

вариационного исчисления, которые лучше

решать вычислительными методами.

Часто встречаются задачи об оптимальном переходе объекта управления из некоторого начального многообразия Ма точек фазового пространства на некоторое конечное многообразие Mv причем размерности этих многообразий могут быть произвольными. В частности, когда оба многообразия равны нулю, то мы приходим к исходной задаче.

Совершенно

очевидно, что в технических системах

не только параметры управления, но

и фазовые координаты объекта управления

должны подчиняться некоторым физическим

ограничениям. Например, высота полета

самолета не может быть отрицательной.

Следовательно, в общем случае должно

выполняться условие (![]() )

)![]() X, где множество X отражает специфику

объекта управления и среды его

функционирования.

X, где множество X отражает специфику

объекта управления и среды его

функционирования.

Другой задачей оптимального управления может быть задача об оптимальном попадании в движущуюся точку фазового пространства.

Допустим, что в фазовом пространстве имеется движущая точка

![]() (1.39)

(1.39)

Тогда возникает задача об оптимальном приведении объекта (1.33) в совпадение с движущейся точкой (1.39). Эта задача легко сводится к первой, если ввести новые переменные, положив:

![]() i=

1, 2...

п. (1.40)

i=

1, 2...

п. (1.40)

В результате этого преобразования система (1.33) превращается в новую, правда уже не автономную, а целью управления становится приведение объекта у{ у2, ..., уп в неподвижную точку (0, 0, ..., 0) фазового пространства.

Совершенно новый и практически важный вопрос возникает, когда движение преследуемого объекта не известно заранее, а сведения о нем поступают только с течением времени. Для решения такой задачи нужно иметь некоторые данные о поведении преследуемого объекта.

Весьма важным представляется случай, когда преследуемый объект является управляемым и его движение описывается системой дифференциальных уравнений:

d![]() /dt =

/dt = ![]() (z1,

z2,..,

zn,u1

и2,

..., um )

(1.41)

(z1,

z2,..,

zn,u1

и2,

..., um )

(1.41)

Задача управления заключается в том, чтобы, зная технические возможности преследуемого объекта, т. е. систему уравнения (1.41) и его положение в каждый данный момент времени, определить управление преследующего объекта в тот же момент времени так, чтобы преследование осуществлялось оптимальным образом. В такой постановке задача рассматривается в теории дифференциальных игр [17, 18]. При этом предполагается, что в начальный момент времени положение преследуемого объекта известно, а дальнейшее его поведение описывается вероятностным образом и процесс его движения считается марковским. В этих предположениях ищется такое управление преследующим объектом (1.33), при котором встреча некоторой малой окрестности объекта (1.33) с преследуемым объектом (1.41) или его малой окрестностью являлась наиболее вероятной.

Указанная задача может быть обратной, т. е. ищется управление для преследуемого объекта (1.41), такое, чтобы встреча некоторой малой окрестности объекта (1.41) с преследующим объектом (1.33) или его малой окрестностью являлась наименее вероятной. Более того, может быть задача, когда преследующих объектов несколько. Все эти задачи относятся к теории дифференциальных игр, а оптимальное решение ищется в условиях неполной определенности.

Наконец, в сложных интеллектуальных системах, обладающих целесообразным поведением, управление может заключаться в выборе наилучшего решения из множества альтернативных при нечетком и не обязательно вероятностном или статистическом описании динамики объекта управления и окружающей среды, а также при нескалярном показателе качества системы управления. Такие задачи относятся к теории принятия решений [19].

Таким образом, при синтезе сложных систем управления обычно необходимо решать задачи принятия решения (ЗПР) об оптимальности системы. Для случаев, когда удается указать шкалу — целевую функцию, значение которой определяет решение, известны и хорошо развиты теория и методы математического программирования [19], позволяющие проводить качественный и численный анализ возникающих при этом четких задач оптимизации решения. Учет неопределенностей, которые могут возникать при решении задач принятия решения при управлении сложными объектами, функционирующими в плохо формализуемой среде, позволяет применять указанные методы математического программирования с большим или меньшим успехом и в этих случаях.

Рассмотрим наиболее популярные вычислительные методы принятия решений.

• Математическое программирование (МП).

В простейшей ситуации принятия решения лицо, принимающее решение (ЛПР), — разработчик — преследует единственную цель, и эта цель может быть формально задана в виде скалярной функции, т. е. критерия качества выбора. При этом значения критерия качества могут быть получены для любого допустимого набора значений аргументов. Предполагается также, что известна область определения параметров управления (выбора), т. е. компонент выбираемого вектора или, во всяком случае, для любой заданной точки может быть установлено, является ли она допустимым выбором, т. е. принадлежит ли она области определения критерия качества решения. В такой ситуации задача выбора решения может быть формализована и описана моделью математического программирования.

В

задаче МП требуется вычислить n-мерный

вектор X, оптимизирующий (обращающий

в максимум или минимум в зависимости

от содержательной постановки задачи)

критерий качества решения

![]() (x)

при соблюдении ограничений

(x)

при соблюдении ограничений

![]() (x)

(x)![]() где

f—

известные скалярные функционалы,

и — заданные числа,

G

— заранее заданное

множество

п- мерного пространства.

где

f—

известные скалярные функционалы,

и — заданные числа,

G

— заранее заданное

множество

п- мерного пространства.

Таким образом, задача МП имеет вид:

![]()

![]() (1.42)

(1.42)

В зависимости от свойств функции f = < /0, /,, •••, /„ > и множества G будет тот или иной класс задач оптимизации. Если все функции f— линейные, a G- многогранное множество, то это задачи линейного программирования (ЛМП). Если среди функций f встречаются нелинейные, то это задачи нелинейного программирования (НМГ1). Среди нелинейных экстремальных задач выделяют выпуклые задачи (ВЗНМП), в которых максимизации подлежат вогнутые функции fn(x) при вогнутых функционалах ограничений f(x) и выпуклой области G. Задачи, в которых G имеет конечное или счетное число точек, выделены в специальный раздел математического программирования — целочисленное или дискретное программирование (ДМП). Если функционал f0 квадратичный, а все остальные функции f линейные и G многогранное множество, то это задачи квадратичного программирования (КМП), которые можно привести к задачам (ЛМП) при использовании теоремы Куна-Таккера [8].

В процессе решения задач большинства оптимального управления, в том числе и управления системами логико-вероятностного типа, можно прийти к задачам МП при выборе оптимального решения, когда имеется возможность построения скалярного критерия качества, в том числе и из атрибутов логических переменных.

• Математическое программирование в порядковых шкалах (МППШ).

Традиционная схема МП, требующая задания целевой функции, т. е. критерия качества, и функционалов ограничений, может не использоваться в механизме принятия решения. Так как решения во многих случаях принимают люди, то для них часто понятие последовательного предпочтения одного из сравниваемых вариантов другому — более естественный путь выбора рациональной альтернативы, чем формулировка цели и приближение к ней. В этом случае допустимое множество альтернатив целесообразно задавать не неравенствами, а некоторыми условиями предпочтения выбираемых вариантов. Такие ситуации встречаются, в частности, при проектировании, когда выбор должен обеспечивать достижение ряда целей, а его допустимость определяют разные люди, ведающие различными ресурсами, ограничивающими выбор.

Для решения таких задач можно обобщить схему математического программирования, переходя от количественных шкал к порядковым, т. е. переходя от моделей, требующих задания функционалов, определяющих цели и ограничения задачи, к моделям, учитывающим предпочтения лиц, участвующих в выборе решения. Это расширяет диапазон приложений теории экстремальных задач и может оказаться полезным в целом ряде ситуаций выбора. В частности, к задачам МППШ можно прийти в процессе решения задач оптимального управления системами логико-лингвистического типа при выборе оптимального решения системы логических уравнений, когда часть атрибутов логических переменных является лингвистическими или нечеткими, но имеется принципиальная возможность упорядочивания предпочтений, формируемых на основании анализа атрибутов и мнения лиц, принимающих решения.

Рассмотрим простейший переход от условий экстремальной задачи в количественных шкалах к условиям задачи в порядковых шкалах.

Пусть

G— некоторое

фиксированное компактное множество в

![]() —

рефлексивные, транзитивные и полные

бинарные отношения в шаре, содержащем

G

предпочтения, g0—

предпочтение лица, принимающего решение.

При этом

—

рефлексивные, транзитивные и полные

бинарные отношения в шаре, содержащем

G

предпочтения, g0—

предпочтение лица, принимающего решение.

При этом ![]() —могут интерпретироваться

как предпочтения лиц, ограничивающих,

каждый по-своему, множество допустимых

планов. Некоторые из отношений

gj

могут определяться обычными функциональными

неравенствами, ограничивающими диапазоны

изменения различных компонент решения.

—могут интерпретироваться

как предпочтения лиц, ограничивающих,

каждый по-своему, множество допустимых

планов. Некоторые из отношений

gj

могут определяться обычными функциональными

неравенствами, ограничивающими диапазоны

изменения различных компонент решения.

Обозначим

через

иi

, j

= 1, 2, ..., r — заданные априори

точки

G

и будем считать, что план х ![]() G

допустим по j-му ограничению,

если xgj

иj.

т. е. если пара (х,

uj)

gjСоответственно

назовем точку

х

G

допустимым решением, если

х gj

иj,

j

= 1, 2,..., r.

G

допустим по j-му ограничению,

если xgj

иj.

т. е. если пара (х,

uj)

gjСоответственно

назовем точку

х

G

допустимым решением, если

х gj

иj,

j

= 1, 2,..., r.

Задача МППШ представляет собой задачу выбора "наилучшего" (в смысле бинарного отношения gQ) среди допустимых решений. В ней требуется найти одно из решений х* — такое, что:

![]()

методы МП. Однако точное вычисление P(CQQ) даже при небольшом числе логических переменных qj представляет собой весьма трудоемкого задачи, которую целесообразно решать приближенно [1]. Кроме того, иногда вместо вероятностных оценок решений уравнений типа: C0Q = 0 используют минимаксные оценки достоверности V( С0 Q), которые вычисляют, используя правила:

V(![]() )

= max{V(

)

= max{V(![]() ),

V(

),

V(![]() )}

и

)}

и

![]() =

min{V(

),

V(

)}.

=

min{V(

),

V(

)}.

Большинство

нелинейных задач МППШ не имеет процедуры

решения приемлемой трудоемкости. Однако

для задач выпуклого МППШ, т. е. для

задач, в которых множество

G

выпукло, а предпочтения

g,

j

= 0, 1, 2, ..., r

— вогнуты, разработан диалоговый метод

решения. Такая процедура позволяет по

последовательно предъявляемым

альтернативам и получаемой локальной

информации о предпочтениях g

на соответствующих парах вариантов

получить е приближенное решение задачи.

При расширении понятия "оптимизация

по бинарному отношению" и расширении

понятия "![]() оптимальное по

g0

решение", удается обобщить метод

решения выпуклой задачи МППШ на случай

произвольных (нерефлексивных, неполных

и нетранзитивных) бинарных отношений

[19]. Ожидается, что значительного

прогресса в решении задач МППШ удастся

достичь за счет применения нейронных

сетей.

оптимальное по

g0

решение", удается обобщить метод

решения выпуклой задачи МППШ на случай

произвольных (нерефлексивных, неполных

и нетранзитивных) бинарных отношений

[19]. Ожидается, что значительного

прогресса в решении задач МППШ удастся

достичь за счет применения нейронных

сетей.

* Обобщенное математическое программирование (ОМП).

Обобщенное математическое программирование — это методология, которая распространяет принципы и методы традиционного математического программирования на случай векторных критериев и векторных ограничений. В отличие от традиционной теории оптимизации схемы ОМП не оценивают допустимость и качество каждой альтернативы, а приближаются к решению в процессе сравнения пар альтернатив. Оптимизация и ограничения в ОМП трактуются в терминах отношений предпочтения.

Во многих случаях ОМП представляет собой естественный подход к численному решению многокритериальных задач, к принятию групповых решений и к анализу конфликтных ситуаций. Используемый в ОМП подход к выбору решений учитывает предпочтения лиц, принимающих решения. При этом предполагается, что каждый участник процесса принятия решения индуцирует на множестве альтернатив некоторые бинарные отношения и сохраняет их в процессе решения задачи.

Ф ормально

запись модели ОМП имеет вид:

ормально

запись модели ОМП имеет вид:

где f(x), j = 0, 1, 2, ..., r— вектор-функции в Rmj, и, — фиксированный вектор в Rm, g.,j =0, 1,2, ..., r— бинарные отношения на G с R".

Модель ОМП соответствует выбору объектов, основанному на сравнении его характеристик, тогда как МППШ соответствует выбору объектов, производимому при непосредственном сравнении пар объектов. Поэтому структура модели ОМП значительно сложнее.

К модели ОМП можно прийти в задачах оптимального управления системами логико-лингвистического типа, если при выборе оптимального решения системы логических уравнений требуется анализировать сложные лингвистические выражения, являющиеся атрибутами (w*, w) или формируемые из атрибутов (w*, w) логических переменных q и q*, характеризующих решения (х*, х). При этом, если указанные лингвистические выражения могут быть сведены к логическим выражениям вида f. = C.Y, где С — идентификационная строка из 0 и 1, Y— вектор, компонентами которого являются конъюнкции логических переменных, характеризующих решения (х*, х), то решение может быть автоматизировано программными средствами искусственного интеллекта [20]. Кроме того, к модели ОМП можно прийти и в процессе решения задач оптимизации управления эволюционно-генетического типа, если в процессе эволюции сохранять неизменными предпочтения ЛПР.

Однако

для получения приемлемой трудоемкости

решения задач ОМП необходимо, чтобы

характеристики вектор-функции

![]() ,

области определения решения

G

и используемые бинарные отношения

,

области определения решения

G

и используемые бинарные отношения

![]() удовлетворяли некоторым специальным

требованиям. Так, конструктивные методы

анализа задач ОМП построены для случаев,

когда составляющие вектор-функции f(x)

— линейные или вогнутые функции,

G—

выпуклое множество, а бинарные

отношения g

— непрерывные, вогнутые, монотонные

и регулярные предпочтения. Такие модели

ОМП называют моделями обобщенного

выпуклого программирования (ОВП). Решение

задач ОМП

в настоящее время связывают с использованием

нейронных сетей и сред типа A-

life.

удовлетворяли некоторым специальным

требованиям. Так, конструктивные методы

анализа задач ОМП построены для случаев,

когда составляющие вектор-функции f(x)

— линейные или вогнутые функции,

G—

выпуклое множество, а бинарные

отношения g

— непрерывные, вогнутые, монотонные

и регулярные предпочтения. Такие модели

ОМП называют моделями обобщенного

выпуклого программирования (ОВП). Решение

задач ОМП

в настоящее время связывают с использованием

нейронных сетей и сред типа A-

life.

• Многошаговые задачи обобщенного математического программирования (МнОМП).

В предыдущем случае функция выбора (ФВ), определяемая предпочтениями ЛПР, была постоянна. Многошаговая схема обобщенного математического программирования может реализовывать произвольную ФВ на конечном множестве вариантов. Схема МнОМП предполагает некоторое расширение понятия "задача ОМП". Это расширение сводится к тому, что допустимое множество решений разрешается получать из множеств решений, выделяемых отдельными ограничениями задачи (xguj), не только их пересечением (уничтожение плохих особей в системе A-life), но и их объединением (скрещивание особей в системе A-life). К МнОМП можно прийти в задаче оптимизации управления эволюционно-генетического типа при изменяющихся предпочтениях ЛПР.

Схема МнОМП представляет собой множество задач ОМП, каждая из которых отвечает фиксированному предъявлению X. При этом решение исходной задачи ОМП может быть принято в качестве входа (предъявления) для другой задачи ОМГ1 и т. д. Таким образом, приходим к последовательной многошаговой схеме ОМП. Однако последовательная схема не реализует все ФВ. В частности, в рамках последовательной схемы не могут быть сформированы некоторые экстремальные задачи, например задача о минимаксе. Недостаток последовательной схемы можно устранить, если разрешить использование на шаге t результатов предыдущих шагов.

Для построения схемы МнОМП с большим числом шагов изменения ФВ с заданной точностью требуется чрезмерно много наблюдений за реализациями ФВ. Кроме того, вычислительная сложность решения задач МнОМП быстро растет с увеличением числа шагов. Поэтому возникает проблема аппроксимации ФВ функциями, реализуемыми более простыми механизмами, такими, например, как схема безусловной оптимизации по би- нарному отношению (уничтожение худшей из двух особей после скрещивания), одно-, двух- и т. д. шаговые схемы ОМГ1 (уничтожение худших после первого, второго и т. д. шагов эволюции). Однако использование современных систем типа A-life позволяет достичь определенного прогресса в решении задач МнОМП.

Таким образом, при формализации задач управления сложными динамическими системами последние целесообразно разбить на подсистемы, описываемые моделями разного уровня сложности и соответственно всю задачу разбить на ряд вложенных друг в друга подзадач, для решения каждой из которых могут быть использованы предназначенные для них методы и средства. При этом нечеткие задачи являются наиболее сложными, особенно в случае управления в человеко-машинных системах.

В настоящее время имеется определенное количество вычислительных методов принятия решения, применение которых в задачах оптимизации нечетких систем в совокупности с современными программными средствами искусственного интеллекта открывает новые возможности существенного повышения уровня автоматизации управления в сложных системах.

Рассмотренные вычислительные методы не исчерпывают все возможные методы решения задач оптимизации управления. Однако они являются наиболее продвинутыми в теоретическом плане и в части реализации с помощью интеллектуальных программных систем [1, 20]. Поэтому изложенные методы могут рассматриваться как конструктивная основа рационального выбора решений подобных задач. Кроме того, в зависимости от решаемого типа задачи можно с большим или меньшим успехом использовать готовые вычислительные алгоритмы и соответствующие инструментальные программные средства, среди которых в настоящее время широко применяются нейронные сети и программные системы A-life с генетическими алгоритмами.

Следует ожидать, что некоторое обобщение механизмов выбора позволит существенно расширить приложения теории принятия решений в области инженерии знаний, а точнее — методах синтеза знаний. По-видимому, целесообразно уточнить определение "база знаний", установив общие и гибкие структуры фиксации и накопления знаний на основе формализации обобщенной функции выбора.

УПРАВЛЯЮЩИЕ ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ

2.1 Обобщенное описание

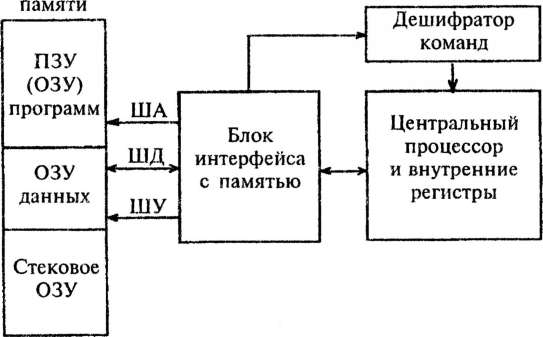

Структура ЭВМ, получившая имя Дж. фон Неймана, была описана им в "Первом наброске отчета по ЭДВАКу" (First Draft jf a Report on the ED VAC, 1945 г.). В нем приводится, ставшее впоследствии классическим, деление компьютера на арифметическо-логическое устройство, устройство управления и память. Здесь же высказана идея программы, хранимой в памяти.

Существенным недостатком машин фон Неймана является принципиально низкая производительность, обусловленная последовательным характером организации вычислительного процесса. Наличие одного процессора обусловливает и другой недостаток этих машин — низкую эффективность использования памяти. В самом деле, память однопроцессорных ЭВМ можно представить как длинную последовательность ячеек. Центральный процессор выбирает содержимое одной из них, дешифрирует, исполняет команду и, при необходимости, возвращает результат памяти в заранее обусловленную ячейку. Затем обращается к очередной ячейке для считывания следующей команды, и процесс повторяется до тех пор, пока не будет выбрана последняя команда исполняемой программы. Нетрудно заметить, что подавляющее большинство ячеек памяти бездействуют. Если ввести понятие коэффициента использования аппаратуры как отношение числа одновременно работающих элементов ЭВМ к общему числу этих элементов, то для машин фон Неймана этот коэффициент будет очень низким.

Почти все современные компьютеры основаны на этих идеях. Они содержат большую память и процессор, снабженный локальной памятью, ячейки которой называются регистрам»;. Процессор может загружать данные из памяти в регистры, выполнять арифметические и логические операции над содержимым регистров и отсылать значения регистров в память. Каждое устройство этой машины реализуется комплексом устройств, объединенных в вычислительную систему каналами связи и дисциплиной использования ресурсов ввода-вывода, памяти и времени, дисциплиной выполнения вычислений, дисциплиной управления выполнением программы и управления потоком программ.

Программа такой машины представляет собой последовательность команд выполнения перечисленных операций вместе с дополнительным множеством команд управления, влияющих на выбор очередной команды. Хотя компьютеры предназначены для использования людьми, возникающие при их создании трудности были столь значительны, что язык описания проблемы и инструкций для их решения на компьютере разрабатывался применительно к инженерным решениям, заложенным в конструкцию компьютера.

По мере преодоления технических проблем построения компьютеров накапливались проблемы, связанные с их использованием. Трудности сместились из области выполнения программ компьютера в область создания программ для компьютера. Начались поиски языков программирования, пригодных для человека. Начиная с языка, воспринимаемого компьютером (машинного языка), стали появляться более удобные формализмы и системы обозначений. И хотя степень абстракции языков возрастала, начиная с языка ассемблера и далее к Фортрану, Алголу, Паскалю, Аде и т.д., все они несут печать машины с архитектурой фон Неймана. Например, в однопроцессорной машине имеются процессор, оперативная память, внутренние часы (таймер), внешние часы, внешние устройства и шины: адресная, данных и управления. Таймер вырабатывает сигналы одинаковой временной протяженности, которые используются при управлении внутренним потоком информации. Внешние часы используются для измерения работы пользователя и измерения времени, которое занимает выполнение тех или иных операций. Через определенные промежутки времени таймер генерирует прерывание и процессор опрашивает все активные устройства, вырабатывающие запросы на обслуживание процессором (прерывания). Устройства обслуживаются в соответствии с установленными приоритетами прерываний, и после обслуживания процессор удаляет выставленное устройством прерывание. Приоритеты могут изменяться программно, и тогда изменяется порядок обслуживания. Таймер используется процессором и для разделения времени между программами (задачами). Дисциплина обслуживания может учитывать структуру оперативной памяти, количество поступивших на обслуживание программ и назначенные им приоритеты. Дисциплина разделения времени может изменяться, если при выполнении программ определяются характеристики, которые учитываются при их дальнейшем выполнении. В тех случаях, когда память организована постранично и программы, поступившие на обслуживание, могут быть все загружены в оперативную память, программам могут отводиться разные страницы, и прерывание выполнения текущей программы и переход к выполнению следующей программы происходят без выгрузки программы из оперативной памяти, иначе текущая программа выгружается из оперативной памяти и загружается следующая. Порядок выполнения программ определяется выбранным алгоритмом в соответствии с приоритетами и временем, уже затраченным на ее выполнение. Рассматривая сложные многопроцессорные машины для высокоскоростных вычислений, можно увидеть, что, несмотря на различную архитектуру, все управляющие вычислительные машины (УВМ) описываются с помощью обобщенной машины фон Неймана, в основе которой лежат различные автоматические системы дискретного действия для переработки информации и которые в кибернетике обычно называют "автоматами" или "конечными автоматами". Поэтому анализ и синтез указанных устройств основывается на теории систем дискретного действия, которая охватывает широкий круг вопросов, связанных с исследованием возможности автоматизации тех или иных процессов переработки информации, повышением производительности и надежности обработки информации и созданием эффективных методов их анализа и синтеза новой элементной базы.

В таких прикладных областях деятельности человека, как космология, молекулярная биология, гидрология, охрана окружающей среды, медицина, экономика и многих других, существуют проблемы, решение которых требует вычислительных машин, обладающих колоссальными ресурсами. Например, требуется быстродействие до 200 TFI.OPS, оперативная память до 200 Гбайт на процессор, дисковая память до 2Тбайт, пропускная способность устройств ввода — вывода (на один порт) не менее 1 Гбайт/с.

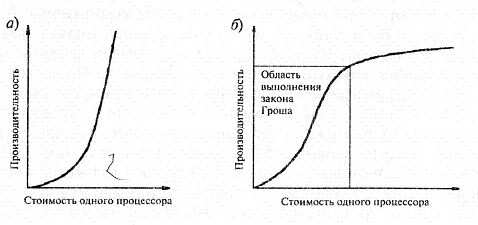

Сегодня схожие технические характеристики реализуются только с помощью дорогостоящих уникальных архитектур от CRAY, SCI, Fujitsu, Hitachi с несколькими тысячами процессоров. В настоящее время концептуально разработаны методы достижения высокого быстродействия, которые охватывают все уровни проектирования вычислительных систем. На самом нижнем уровне — это технология изготовления быстродействующей элементной базы и плат с высокой плотностью монтажа. Это наиболее простой путь к увеличению производительности ЭВМ за счет сокращения задержек при распространении сигналов, хотя, несмотря на успехи в создании элементной базы и методов монтажа, и удваивании в соответствии с законом Мура (рис. 2.1) плотности элементов на кристалле каждые 18 месяцев, увеличения производительности микропроцессоров N вдвое получить уже не удается. В настоящее время уже возможен выпуск процессоров со следующими характеристиками:1 млрд транзисторов на кристалле; тактовая частота 10 ГГц; производительность 2,5 тыс. MFLOPS (1 MFLOPS = 106 операций с плавающей точкой в 1 с). Дальнейшее увеличение эффективности процессора и его рабочей частоты возможно за счет совершенствования полупроводниковых технологий.

Рис. 2.1. Закон Гордона Мура N — число транзисторов в кристалле

При изготовлении процессорных чипов на пластине из кремния создается слой из окиси кремния, и далее, используя в литографическом процессе различные маски, при формировании структуры из него удаляются лишние участки. Затем добавляются необходимые примеси, что позволяет получить полупроводниковые структуры с необходимыми свойствами, затем прокладываются соединительные проводники, обычно из алюминия. Литографический процесс предусматривает засвечивание светочувствительных материалов через маски. Помимо чисто технических проблем совмещения масок при формировании структуры чипа с необходимой точностью, существуют физические ограничения, связанные с длиной волны излучения и минимальными размерами получаемого изображения. Тем не менее, в настоящий момент компании — производители чипов начали переход на нормы 65 нм (в 10 раз меньше длины волны красного света). Внедрение норм 65 нм позволяет интегрировать на кристалле площадью около 110 мм2 более полумиллиарда транзисторов. При этом удается уменьшить утечки в расчете на один транзистор (поскольку примерно вдвое уменьшилась его площадь), снизить на 20 % его балластную емкость и в конечном итоге повысить быстродействие. Утечки новых транзисторов 65 нм при том же рабочем токе уменьшены вчетверо, на чипе введены так называемые спящие транзисторы, которые отключают питание отдельных блоков памяти при их бездействии.

Переход на новые нормы обеспечивается преодолением сложнейших технических и технологических проблем. Решение проблемы совместимости материалов позволяет заменить алюминиевые соединений на медные, уменьшить сечение межкомпонентных соединений. Решение технологической проблемы нанесения дополнительных пленок кремния на изолятор, так называемая технология кремний на изоляторе (silicon-on- insulator, SOI), позволило уменьшить емкость МОП-структур и достаточно просто повысить их быстродействие.

Другим разрабатываемым компонентом является материал чипов. На скорости чипа в несколько гигагерц растут потери в кремнии. Возможное использование такого известного высокочастотного материала, как арсенида галлия, — дорого. Одним из предлагаемых решений стало использование в качестве материала для подложек соединения двух материалов — кремния с германием, SiGe. Результатом применения становится увеличение скорости чипов в 2—4 раза по сравнению с той, что может быть достигнута путем использования кремния. Во столько же раз снижается и их энергопотребление. Стоимость производства чипов при этом практически не возрастает. Их можно производить на тех же линиях, которые используются при производстве чипов на базе обычных кремниевых пластин, что исключает необходимость в дорогом переоснащении производственного оборудования.

Проводятся эксперименты и с различными нетрадиционными материалами. Например, сообщалось о создании фирмой Motorola опытных структур с использованием титаната стронция. Он превосходит по диэлектрическим свойствам диоксид кремния более чем на порядок. Это позволяет в три-четыре раза снизить толщину транзисторов по сравнению с использованием традиционного подхода, значительно снизить ток утечки, увеличить плотность транзисторов на чипе, одновременно уменьшая его энергопотребление.

При переходе к 45-нанометровому технологическому процессу, для создания затворов компания AMD предполагает использовать силицид никеля. Этот металлосодержащий материал обеспечивает лучшие характеристики по токам утечки по сравнению с традиционным кремнием. Отмечается, что подобный подход обеспечивает более чем двукратное увеличение быстродействия.

Компании Sony и Toshiba также начали новый совместный проект, направленный на разработку 45-нанометровых полупроводниковых структур. В рамках проекта компания Toshiba разработала технологию создания чипов, содержащих значительно большее количество слоев, чем используется сегодня. Речь идет о разработке девятислойных чипов, которые можно поместить в корпус высотой 1,4 мм. Сегодня производятся шестислойные чипы и мультичиповые компоненты.

К перспективным относятся планируемые фирмой Intel к применению с 2013 года технологии углеродных нанотрубок и кремниевых нанопроводников. Уже удалось интегрировать углеродные нанотрубки в кремний и создать полевой транзистор размерами всего 5 нм. Следующий шаг — создание транзисторов на полупроводниковых нанотрубках, диаметр которых составляет лишь 1,4 нм. По сообщениям Intel и японской фирмы NEC (владельца патента на коммерческое использование углеродных нанотрубок) с 2011-го по 2019 год чипы будут создаваться на основе нанотрубок из кремния и углерода.

Повышение производительности предполагает также исследования в области схемотехники процессоров. Увеличение быстродействия достигается при уменьшении числа логических уровней при реализации комбинационных схем. Создаются схемы с ограничениями по количеству вентилей и их коэффициентам соединений по входу и выходу. Быстродействие вычислительных систем может быть повышено за счет реализации специальными аппаратными средствами вычисления сложных функций, например корней, сложения, векторов, умножения матриц, быстрого преобразования Фурье. Указанные средства позволяют сократить число команд в программах и более эффективно использовать машинные ресурсы. Существует небольшое подмножество простых и часто используемых команд, которые можно оптимизировать, а сокращение времени обращения к памяти достигается за счет разбиения памяти на модули, обращение к которым может осуществляться одновременно, за счет применения кэш-памяти и увеличения числа внутренних регистров в процессоре.

Полная реализация потенциально высокого быстродействия системы поддерживается разработкой алгоритмов, которые приводили бы к простым комбинационным схемам с небольшим числом циклов для основных операций — сложения, умножения, деления, и с внутренним параллелизмом.

Совершенствование элементной базы — самый простой метод повышения производительности вычислительных систем, но он приводит к существенному удорожанию новых разработок. Поэтому наиболее приемлемым путем к созданию высокопроизводительных УВМ, оцениваемых по критерию "производительность/стоимость", может быть путь исследования и разработки новых методов логической организации систем, а также новых принципов организации вычислений. Основной способ повышения производительности с этой точки зрения — исполь-

зование параллелизма, который реализуется на верхнем уровне структурой алгоритма, по которому работает система. Он состоит в том, чтобы выполнять одновременно несколько команд. Этот подход отличается оттого, который реализован в обычной фон- неймановской машине, когда команды исполняются строго последовательно одна за другой. При такой обработке предусматривается одновременное выполнение программ или их отдельных частей на независимых устройствах.

Параллельный подход приводит к различным вариантам архитектуры в зависимости от способа, по которому осуществляется задание очередности следования команд и управление их исполнением. Распараллеливание позволяет значительно увеличить производительность систем при решении широкого класса прикладных задач.

Известны следующие базовые способы введения параллелизма в архитектуру УВМ:

конвейерная, или векторная (Parallel Vector Processor — PVP) организация. В основе ее работы лежит концепция конвейеризации, т. е. явного сегментирования арифметического устройства на отдельные части, каждая из которых выполняет свою подзадачу для пары операндов (рис. 2.2);

Рис. 2.2. Конвейерная вычислительная система

функциональная обработка — предоставление нескольким независимым устройствам возможности параллельного выполнения различных функций, таких, как операции логики, сложения, умножения, прирашения и т.д., и обеспечение взаимодействия с различными данными;

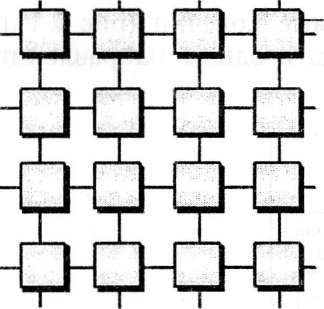

параллельная или матричная (массивная) (Massively Parallel Processor— МРР) организация, в основе которой лежит идея использования для решения одной задачи нескольких одновременно работающих процессорных элементов (ПЭ). Причем процессоры могут быть как скалярными, так и векторными, с общей системой управления, и организованных в виде матриц. Все процессоры выполняют одну и ту же операцию, но с различными данными, хранящимися в локальной памяти каждого процессора, т. е. выполняют жестко связанные пошаговые операции (рис. 2.3);

Рис. 2.3. Матричная вычислительная система (ПЭ — процессорные элементы, П — модули памяти)

мультипроцессорная обработка — осуществляется несколькими процессорами, каждый из которых имеет свои команды; взаимодействие процессоров осуществляется через общее поле памяти.

Естественно, что в отдельных проектах могут объединяться некоторые или все эти способы параллельной обработки.

Эти подходы позволяют достичь значительного ускорения по сравнению со скалярными машинами. Ускорение в системах матричного типа может быть больше, чем в конвейерных, поскольку увеличить число процессорных элементов проще, чем число ступеней в конвейерном устройстве.

Принцип векторной обработки обоснован существованием значительного класса задач, использующих операции над векторами. При этом под вектором понимаем одномерный массив, который образуется из многомерного массива, если один из индексов пробегает все значения в диапазоне его изменения. В некоторых задачах векторная форма параллелизма представлена естественным образом, например при перемножении матриц. Алгоритмы этих задач в соответствии с терминологией Флинна относятся к классу ОКМД (одиночный поток команд, множественный поток данных, см. далее).

Так как в векгорно-конвейерной системе один (или небольшое число) конвейерный процессор выполняет команды путем засылки элементов векторов в конвейер с интервалом, равным длительности прохождения одной стадии обработки, скорость вычислений зависит только от длительности стадии и не зависит от задержек в процессоре в целом.

Реализация операций обработки векторов на скалярных процессорах с помощью обычных циклов ограничивает скорость вычислений из-за их последовательного характера.

Работа векторных компьютеров опирается на последовательно-групповую алгоритмическую структуру вычислительных процедур. Процедуры внутри группы могут выполняться одновременно, а сами группы — последовательно. Векторные команды — это группы, составленные из идентичных операций, и векторные компьютеры манипулируют всем массивом сходных данных подобно тому, как скалярные машины обрабатывают отдельные элементы таких массивов. При векторной обработке задается одна и та же операция над всеми элементами одного или нескольких векторов. PVP-системы имеют специальные векторно-конвейерные процессоры, в которых предусмотрены команды однотипной обработки. Эти векторные центральные процессоры включают в себя векторные регистры и конвейерные АЛУ. Когда данные обрабатываются посредством векторных модулей, результаты выдаются за один рабочий цикл сразу для всего вектора. При работе в векторном режиме векторные процессоры обрабатывают данные практически параллельно, что делает их в несколько раз более быстрыми, чем при работе в скалярном режиме. Важной особенностью векторных конвейерных процессоров, используемой для ускорения вычислений, является механизм зацепления. Зацепление — такой способ вычислений, когда одновременно над векторами выполняется несколько операций. Например, можно одновременно производить выборку вектора из памяти, умножение векторов, суммирование элементов вектора

Существенной особенностью векторно-конвейерной архитектуры является то, что данные всех параллельно исполняемых операций выбираются и записываются в единую память. Как правило, несколько процессоров работают одновременно с общей памятью в рамках многопроцессорных конфигураций. Несколько таких узлов могут быть объединены с помощью коммутатора (аналогично МРР). Передача данных в векторном формате осуществляется намного быстрее, чем в скалярном. Проблема взаимодействия между потоками данных при распараллеливании становится несуществ. Архитектура векторной обработки в PVP системах позволяет использовать стандартные языки высокого уровня. Задача программирования на PVP-системах заключается в векторизации циклов и их распараллеливании, например за счет переведения задачи в матричную форму и разложении функций в ряд с числом членов, кратным числу процессов.

Существует ряд факторов, приводящих к тому, что при выполнении реальных программ производительность векторных ЭВМ оказывается значительно ниже максимально возможной. К ним относится невозможность построить реальную прикладную программу, состоящую только из векторных операций. Часть вычислений остается скалярной, в том числе команды для подготовки векторных команд и управления их прохождением. Эффективность конвейера определяется длиной векторов, поскольку существует непроизводительное время, затрачиваемое на начальном этапе (загрузка параметров, реконфигурация, ожидание первого результата). Наличие стартового времени приводит к тому, что векторная обработка оказывается эффективней скалярной, лишь начиная с некоторого порога длины векторов. Всегда существуют зависимости по данным между командами, т. е. одна команда не может исполняться до завершения другой, и нарушается условие одновременности исполнения нескольких команд. Аналогичная ситуация с условными переходами, когда не ясно, какая команда должна выполняться следующей, или векторная команда как единое целое не может быть выполнена в ситуациях, когда вид операции над элементами вектора зависит от условия. К неудобным операциям относятся рассылка и сбор элементов по памяти, которые имеются в задачах сортировки, быстрого преобразования Фурье, при обработке графов и списков.

Снижают быстродействие и ограничения, связанные с памятью. С целью достижения максимальной скорости работы в системах применяются сложные способы обращения к памяти. Поэтому любое отклонение от спецификации работы снижает производительность. К ним относятся и нахождение команд вне специального буфера команд, и изменения пропускной способности тракта обмена данными при обращении к памяти, или неполное ее использование, что связано с тем, что время доступа к памяти превышает длительность одной стадии обрабатывающего конвейера. При решении задач иногда массивы данных оказываются столь большими, что не могут уместиться в главной памяти, и существуют потери за счет подкачки и удаление информации в процессе счета. Соотношение объема памяти должно быть хорошо сбалансировано с производительностью системы. По эмпирическому правилу Амдала 1 бит памяти должен приходиться на 1 оп/с. Максимальная пропускная способность системы достигается только в том случае, когда все арифметические устройства используются полностью. Следовательно, реальная производительность зависит от состава операций в конкретной программе и использования всех арифметических устройств полностью. Например, поскольку деление плохо поддается конвейеризации, обычно оно выполняется в устройствах обратной аппроксимации и умножения посредством итерационной процедуры.

Система с матричной архитектурой (МРР) состоит из множества процессорных элементов, организованных таким образом, что они исполняют векторные команды, задаваемые общим для всех устройством управления. Причем каждый процессорный элемент работает с отдельным элементом вектора. Исполнение векторной команды включает чтение из памяти элементов векторов, распределение их по процессорам, выполнение заданной операции и засылку результатов обратно в память.

Существует архитектура, где система строится из отдельных модулей, содержащих процессор, локальный банк операционной памяти, два коммуникационных процессора (рутера) или сетевой адаптер, иногда — жесткие диски и/или другие устройства ввода/вывода. Один рутер используется для передачи команд, другой — для передачи данных. По сути, такие модули представляют собой полнофункциональные компьютеры. Доступ к банку операционной памяти из данного модуля имеют только процессоры из этого же модуля. Модули соединяются специальными коммуникационными каналами. Пользователь может определить логический номер процессора, к которому он подключен, и организовать обмен сообщениями с другими процессорами. Используются два варианта работы операционной системы (ОС) на машинах МРР архитектуры. В одном полноценная операционная система (ОС) работает только на управляющей машине (front-end), а на каждом отдельном модуле работает сильно урезанный вариант ОС, обеспечивающий работу только расположенной в нем ветви параллельного приложения.

Во втором варианте на каждом модуле работает полноценная UNIX- подобная ОС, устанавливаемая отдельно на каждом модуле.

Главным преимуществом систем с раздельной памятью является хорошая масштабируемость, так как в машинах с раздельной памятью каждый процессор имеет доступ только к своей локальной памяти, в связи с чем не возникает необходимости в потактовой синхронизации процессоров. К недостаткам, связанным с отсутствием общей памяти, относится снижение скорости межпроцессорного обмена, поскольку нет общей среды для хранения данных, и ограниченный объем локального банка памяти. Требуется специальное программирование для реализации обмена сообщениями между процессорами. Программирование параллельной работы нескольких сотен процессоров и при этом обеспечение минимума затрат счетного времени на обмен данными между ними определяют высокую цену программного обеспечения для матрично-параплельных систем с раздельной памятью. При работе с МРР-системами используют так называемую Massive Passing Programming Paradigm — парадигму программирования с передачей данных (MPI, PVM, BSPlib).

Н а

основе сопоставления фон-неймановской

ЭВМ и многопроцессорной системы были

сформулированы критерии оценки

производительности: закон Гроша и

гипотеза Минского.

а

основе сопоставления фон-неймановской

ЭВМ и многопроцессорной системы были

сформулированы критерии оценки

производительности: закон Гроша и

гипотеза Минского.

Рис. 2.4. Закон Гроша

Закон Гроша гласит, что производительность одного процессора увеличивается пропорционально квадрату его стоимости (см. рис. 2.4, а). На практике в верхней области графика

Рис. 2.5. Гипотеза Минского

зависимость имеет совершенно иной вид (см. рис. 2.4, о) и можно расходовать все больше средств, не получая при этом скорости вычислений, предсказываемой законом Гроша.

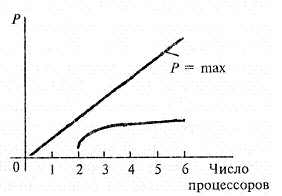

Гипотеза Минского утверждает, что в параллельной системе с п процессорами, производительность каждого из которых равна единице, общая производительность растет лишь как log2AJ (рис. 2.5) из-за необходимости обмена данными. Однако загруженность п процессоров может быть гораздо выше log2« за счет введения соответствующих механизмов управления.

Эффективность использования различных способов организации вычислительной системы (ВС) напрямую зависит от структур реализуемых алгоритмов. Параллелизм алгоритмов определяется иерархией, которая существует в том смысле, что возможно описание вычислительного процесса в виде последовательности более простых конструкций, которые, в свою очередь, могут быть описаны в виде алгоритмов, состоящих из еще более простых вычислительных конструкций. Детализацию называют мелкой, если вычислительные конструкции алгоритма являются примитивными (т. е. реализуемыми одной командой), и крупной, если эти конструкции являются сложными (т. е. реализуются с помощью другого алгоритма). В системах может использоваться комбинированная детализация. Для ее реализации должны использоваться специальные языки программирования, предоставляющие средства для явного описания параллелизма.

Даже из краткого описания принципов работы таких систем можно сделать вывод, что при выполнении реальных программ производительность систем с параллельной организацией вычислений определяется содержанием конкретных программ, учетом в них факторов, влияющих на производительность машины конкретной архитектуры. Поэтому попытки сравнения

производительности машин на контрольных прикладных задачах с определенным соотношением скалярных и векторных опе раций могут дать лишь грубые оценки. Одними из используемых для оценки машин контрольных задач являются так называемые ливерморские циклы, разработанные в Национальной лаборатории им. Лоуренса в г. Ливермор (США). Специфическое влиянии на производительность машин особенностей организации систем и качества используемого компилятора подтверждается тем, что даже для одного типа машин оценки производительности, полученные на разных циклах, отличаются друг от друга в десятки раз.

Чтобы получить более полное представление о многопроцессорных вычислительных системах, помимо такой их характеристики, как высокая производительность, необходимо отметить и другие отличительные особенности. Прежде всего — это необычные архитектурные решения, направленные на повышение производительности (работа с векторными операциями, организация быстрого обмена сообщениями между процессорами или организация глобальной памяти в многопроцессорных системах и др.). Понятие архитектуры высокопроизводительной системы является достаточно широким, поскольку под архитектурой можно понимать и способ обработки данных, используемый в системе, и организацию памяти, и топологию связи между процессорами, и способ исполнения системой арифметических операций. Попытки систематизировать все множество архитектур начались в конце 1960-х годов и продолжаются по сей день. В 1966 году М. Флинном (Flynn) был предложен подход к классификации архитектур вычислительных систем на основе понятий потока команд или данных, обрабатываемых процессором. Классификация описывает четыре архитектурных класса:

SISD = Single Instruction Single Data (ОКОД-одиночный поток команд и одиночный поток данных)

MISD = Multiple Instruction Single Оа1а(МКОД-множествен- ный поток команд и одиночный поток данных)

SIMD = Single Instruction Multiple Data (ОКМД-одиночный поток команд и множественный поток данных)

MIMD = Multiple Instruction Multiple Data (МКМД-множе- ственный поток команд и множественный поток данных)

К классу SISD относятся последовательные компьютерные системы, которые имеют один центральный процессор, способный обрабатывать только один поток последовательно исполняемых инструкций. В настоящее время практически все высокопроизводительные системы имеют более одного центрального процессора, однако каждый из них выполняют несвязанные потоки инструкций, что делает такие системы комплексами S1SD- систем, действующих на разных пространствах данных. Для увеличения скорости обработки команд и скорости выполнения арифметических операций может применяться конвейерная обработка.

Важное преимущество последовательного подхода, реализующего эту архитектуру, состоит в том, что для машин такого вида разработано большое число алгоритмов и пакетов прикладных программ, созданы обширные базы данных, накоплен богатый опыт программирования, разработаны фундаментальные языки и технологии программирования. Поэтому дальнейшее совершенствование организации ЭВМ (мэйнфреймов и микропроцессоров) шло таким образом, что последовательная структура сохранялась, а к ней добавлялись механизмы, позволяющие выполнять несколько команд одновременно. До последнего времени параллельная обработка на уровне команд (instruction- level-parallelism — ILP) принималась как единственный подход, позволяющий добиваться высокой производительности без изменения программного обеспечения.

В классе машин MISD множество инструкций должно выполняться над единственным потоком данных. До сих пор ни одной реальной машины, попадающей в данный класс, не было создано. Косвенный аналог работы таких машин — обработка базы данных одновременно несколькими потребителями.

Системы архитектуры SIMD обычно имеют большое количество процессоров — тысячи и десятки тысяч, которые могут выполнять одну и ту же инструкцию относительно разных данных в жесткой конфигурации. Единственная инструкция параллельно выполняется над многими элементами данных. Основные технические принципы организации компьютеров этого класса используются на разных уровнях архитектуры систем других классов.

Каждой архитектуре системы можно сопоставить свой вид алгоритмической структуры организации высокоскоростных вычислений (рис. 2.6).

Последовательная структура и соответствующая ей S1SD архитектура является простейшей. В последовательно-групповой алгоритмической структуре вычислительные процедуры объединены в группы, а отношение следования состоит в том, что процедуры внутри группы могут выполняться одновременно, а сами группы — последовательно. Вычислительные процедуры внутри одной группы могут быть одинаковыми или разными. Наиболее типичным является случай, когда одинаковые вычислительные процедуры образуют одиночный поток команд и множественный поток данных (SIMD).

Возможно ускорение вычислений за счет использования алгоритмов, структура которых представляет совокупность слабо связанных потоков команд (последовательных процессов). В этом случае программа может быть представлена как совокупность процессов, каждый из которых может выполняться на отдельном последовательном процессоре и при необходимости

Рис.

2.6. Алгоритмические структуры: а

—

последовательная;

б—

последовательно- групповая

в —

слабосвязанные потоки; г —■ параллельная

структура общего вида

Рис.

2.6. Алгоритмические структуры: а

—

последовательная;

б—

последовательно- групповая

в —

слабосвязанные потоки; г —■ параллельная

структура общего вида

осуществлять взаимодействие с другими процессорами. Вычислительные системы, отвечающие особенностям данной алгоритмической структуры, — это многопроцессорные системы архитектуры MIMD, особенностью которых является необходимость синхронизации взаимосвязи между процессами. Г1о этому принципу все архитектуры MIMD делятся на два класса: взаимодействующие через общую память (класс А) и путем обмена сообщениями (класс Б) (рис. 2.7). Класс архитектуры Б предназначен для систем с большим числом процессоров.

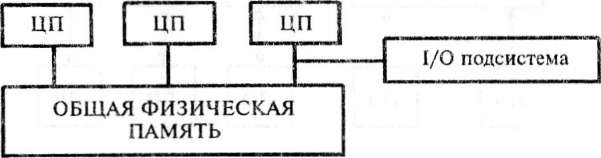

В архитектуре класса А, или SMP-архитектуре (symmetric multiprocessing) — симметричная многопроцессорная архитектура, физическая память является общей для всех ПЭ. Это означает, что здесь существуют задержки в коммутационном устройстве и при доступе в память. Таким образом, в таких системах требуется, чтобы коммутационное устройство имело высокое быстродействие, а при доступе в память количество конфликтов было минимальным.

П амять

является способом передачи сообщений

между процессорами, при этом все

вычислительные устройства при обращении

к ней имеют равные права и одну и ту же

адресацию для всех ячеек памяти. Поэтому

S MP-архитектура

называется симметричной. Последнее

обстоятельство позволяет очень

эффективно обмениваться данными с

другими вычислительными устройствами.

SMP-система строится на

основе высокоскоростной

амять

является способом передачи сообщений

между процессорами, при этом все

вычислительные устройства при обращении

к ней имеют равные права и одну и ту же

адресацию для всех ячеек памяти. Поэтому

S MP-архитектура

называется симметричной. Последнее

обстоятельство позволяет очень

эффективно обмениваться данными с

другими вычислительными устройствами.

SMP-система строится на

основе высокоскоростной

Рис. 2.7. Схема архитектуры MIMD — класс А и класс Б

системной шины (SGI PowerPath, Sun Gigaplane, DECTurboLaser), к слотам которой подключаются функциональные блоки трех типов: процессоры (ЦП), операционная система (ОП) и подсистема ввода/вывода (I/O) (рис. 2.8). Вся система работает под управлением единой ОС (обычно UNIX-подобной, но для Intel- платформ поддерживается Windows NT). ОС автоматически (в процессе работы) распределяет процессы по ЦП, но иногда возможна и явная привязка.

К преимуществам SMP-систем относится простота и универсальность для программирования. Архитектура SMP не накладывает ограничений на модель программирования, используемую при создании приложения: обычно используется модель параллельных ветвей, когда все процессоры работают абсолютно независимо друг от друга. Однако можно реализовать и модели, использующие межпроцессорный обмен. Использование общей памяти увеличивает скорость такого обмена, пользователь также имеет доступ сразу ко всему объему памяти. Для SMP- систем существуют сравнительно эффективные средства автоматического распараллеливания. Она легка в эксплуатации и относительно дешева.

К основным недостаткам SMP-систем относится плохая масштабируемость, связанная с тем, что в конкретный момент шина способна обрабатывать только одну транзакцию, и возникают проблемы разрешения конфликтов при одновременном обращении нескольких процессоров к одним и тем же областям общей физической памяти. Кроме того, системная шина имеет ограниченную (хоть и высокую) пропускную способность и ограниченное число слотов. В реальных системах используется не более 32 процессоров. При работе с SMP-системами используют

Рис.

2.8. Схематический вид SMP-архитектуры

Для построения масштабируемых систем на базе SMP-npo- цессоров используются кластерные или NUMA-архитектуры.

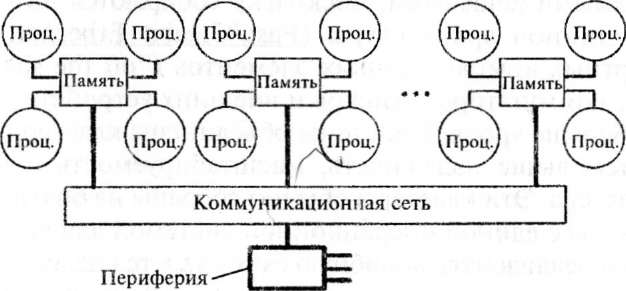

Гибридная архитектура NUiVlA (nonuniform memory access) (рис. 2.9) воплощает в себе удобства систем с общей памятью и относительную дешевизну систем с раздельной памятью. Главная особенность такой архитектуры — неоднородный доступ к памяти за счет такой организации, что память является физически распределенной по различным частям системы, но логически объединяемой, так что пользователь видит единое адресное пространство. Система состоит из однородных базовых модулей (плат), состоящих из небольшого числа процессоров и блока памяти. Модули объединены с помощью высокоскоростного коммутатора. Поддерживается единое адресное пространство, аппаратно поддерживается доступ к удаленной памяти, т. е. к памяти других модулей. При этом доступ к локальной памяти осуществляется в несколько раз быстрее, чем к удаленной.

По существу архитектура NUMA является МРР-архитекту- рой, где в качестве отдельных вычислительных элементов беруг- ся SMP (симметричная многопроцессорная архитектура) узлы. В такой структуре кэш-память принадлежит отдельному модулю, а не всей системе в целом, и данные в кэше одного модуля могут быть недоступны другому. Дальнейшим улучшением архитектуры

Рис. 2.9. Структурная схема компьютера с гибридной архитектурой: четыре процессора связываются между собой в рамках одного SMP-узла

NUMA является наличие когерентного кэша. Это так называемая архитектура cc-NUMA (Cache Coherent Non-Uniform Memory Access), в которой имеется "неоднородный доступ к памяти с обеспечением когерентности кэшей".

При когерентности кэшей все центральные процессоры получают одинаковые значения одних и тех же переменных в любой момент времени. Для обеспечения синхронизации кэшей используют механизм отслеживания шинных запросов (snoopy bus protocol) или выделяют специальную часть памяти, отвечающую за отслеживание достоверности всех используемых копий переменных.

На настоящий момент максимальное число процессоров в сс- NUMA-системах может превышать 1000. Обычно вся система работает под управлением единой ОС, как в SMP. Возможны также варианты динамического "подразделения" системы, когда отдельные "разделы" системы работают под управлением разных ОС.

В кластерной архитектуре кластеры, которые представляют собой два или больше компьютеров (часто называемых узлами), объединяются при помощи сетевых технологий на базе шинной архитектуры или коммутатора в единый информационно-вычислительный ресурс. В случае сбоя какого-либо узла другой узел кластера может взять на себя нагрузку неисправного узла, и пользователи не заметят прерывания в доступе. Возможности масштабируемости кластеров позволяют увеличивать производительность приложений. Такие суперкомпьютерные системы являются самыми дешевыми, поскольку собираются на базе стандартной шинной архитектуры (Fast/Gigabit Ethernet. Mvrinet) и стандартных комплектующих элементов ("off the shelf'): процессоров, коммутаторов, дисков и внешних устройств.

Чем больше уровней системы объединены кластерной технологией, тем выше надежность, масштабируемость и управляемость кластера. Эти кластеры обычно собраны из большого числа компьютеров с единой операционной системой для всего кластера. Однако реализовать подобную схему удается далеко не всегда, и обычно она применяется для не слишком больших систем.

Многопоточные системы используются для обеспечения единого интерфейса к ряду ресурсов, которые могут со временем произвольно наращиваться (или сокращаться) в размере.

Архитектура кластерной системы (способ соединения процессоров друг с другом) в большей степени определяет ее производительность, чем тип используемых в ней процессоров.

Одной из перспективных структур и протокола для построения больших систем является Scalable Coherent Interface /Local Area Multiprocessor/ (SCI/LAMP). Это расширяемый связной интерфейс (РСИ), представляющий собой комбинацию основных компьютерных шин, шин процессорной памяти, высокопроизводительных переключателей, местных и удаленных оптических связей, информационных систем, использующих связи точка- точка, обеспечивающих когерентное кэширование распределенной памяти и расширений. SCI/LAMP строится на интерфейсах общего применения, таких как PCI, УМЕ, Futurebus, Fastbus, и т.д., и I/O соединениях, таких как ATM или FibreChannel.

Структура и логический протокол РСИ позволяют обеспечить высокую эффективность сотен и тысяч процессоров, совместно работающих в больших системах.

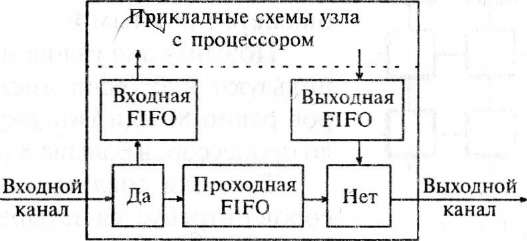

Узел РСИ (рис. 2.10) получает через входной канал пакеты символов, состоящих из двух байтов. В случае совпадения значения первого символа с присвоенным узлу адресом пакет через входную FIFO передается в прикладные схемы узла на обработку, например, процессором. При несовпадении пакет через проходную FIFO и ключ попадает в выходной канал. Ключ нужен для задержки проходящего пакета на время выдачи пакета обработанной информации через выходную FIFO.

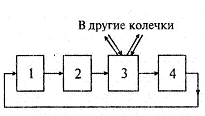

Узлы соединяются в так называемые колечки (рис 2.11), в которых пакеты продвигаются всегда в одном направлении

Рис.

2.10. Узел РСИ

Рис 2.11. Колечко РСИ

(на рисунке один из узлов выполнен в качестве переключателя на другие колечки). Переключатели позволяют образовать из колечек сети произвольной конфигурации, например регулярные структуры. В больших системах, при большом числе узлов с процессорами, одиночное колечко становится неэффективным вследствие того, что слишком большой получается длина структурного пути, выражаемая числом узлов, через которые проходят пакеты. Регулярные структуры позволяют существенно сократить путь. Колечки с & узлами РСИ соединены переключателями в я-мерные структуры, которые содержат: Уг = кп — геометрических узлов.При к > 2 образуются регулярные структуры, удобные для применения на практике, причем для больших систем ценны кубы и гиперкубы. Критическим параметром, влияющим на величину производительности такой системы, является расстояние (количество связей) между процессорами.

Рис.

2.12. Схема соединения процессоров в виде

плоской решетки

Поэтому для узловой системы используют куб (если число процессоров равно 8) или гиперкуб, если число процессоров больше 8 (см. рис. 2.13).

Так, для соединения 16 процессоров потребуется четырехмерный гиперкуб, который получается за счет сдвига обычного куба.

4-мерный

гиперкуб

Рис.

2.13. Пример гиперкуба

Используются и другие топологии сетей связи: трехмерный тор, "кольцо", "звезда" и другие (рис. 2.14).

Наиболее эффективной является архитектура с топологией "толстого дерева" (fat-tree). Архитектура "fat-tree" (hypertree) предложена Лейзерсоном (Charles Е. Leiserson) в 1985 году.

Процессоры локализованы в листьях дерева, в то время как внутренние узлы дерева скомпонованы во внутреннюю сеть. Поддеревья могут общаться меж^у собой, не затрагивая более высоких уровней сети (рис. 2.15).

В кластерах, как правило, используются операционные системы, стандартные для рабочих станций, чаще всего свободно распространяемые — Linux, FreeBSD, вместе со специальными средствами поддержки параллельного программирования и балансировки нагрузки. При работе с кластерами, так же как и с МРР-системами, используют Massive Passing Programming Paradigm — парадигму программирования с передачей данных (чаще всего — МР1).

В последнее время все более широкое распространение получают транспьютеры, из которых строят системы класса Б. Транспьютер является однокристалльной системой, содержащей процессор и оперативную память. Для объединения транспьютеров в систему используют механизмы связи (линки), являющиеся встроенными специальными средствами обмена сообщениями. Поскольку линки различных транспьютеров совместимы, то через коммутационную матрицу можно конфигурировать системы различной мощности.

Действие ряда отрицательных факторов снижает реальный коэффициент ускорения вычислений за счет выполнения параллельных операций. К этим факторам относятся:

недостаточный параллелизм алгоритма, т. е. отсутствие полной загрузки процессоров. Известно не так много алгоритмов, в которых при их выполнении число параллельных ветвей сохранялось бы достаточно большим. Поэтому для эффективного использования ресурсов в таких системах целесообразно одновременно выполнять несколько разных программ)

конфликты и задержки при обращениях к общей памяти. При назначении каждому процессору локальной памяти снижается коэффициент использования памяти;

большие расходы по организации синхронизации между взаимодействующими потоками.

Дальнейшее развитие архитектур MIMD связывается с комбинированием различных принципов вычислений. Наиболее эффективным является объединение архитектур MIMD и PVP. Другим примером является архитектура НЕР-1 (Heterogenerolis Element Processor} фирмы Denelcor. Особенностью НЕР-1 является организация мультипроцессора как нелинейной системы, состоящей из группы процессоров команд, каждый из которых генерирует "свой" процесс (поток команд). Обработка множества формируемых таким образом процессов осуществляется на одном и том же арифметическом устройстве конвейерного типа в режиме разделения времени без использования коммутационной сети, что значительно снижает стоимость системы, поскольку на реализацию АЛУ обычно приходится до 60 % аппаратных ресурсов центрального процессора.

Основным недостатком MIMD-архитектур является отсутствие возможности составления программ на стандартных языках последовательного типа, в отличие от векторных суперЭВМ. Для эффективного программирования таких систем потребовалось введение совершенно новых языков параллельного программирования, таких, как Parallel Pascal, Modula-2, Occam, Ада, Val, Sisal и др., и создание новых прикладных пакетов программ.

Реализация алгоритмической структуры сильно связанных потоков требует организации принципа вычислений, отличного от фон-неймановского (управление потоком команд) и определяется как управление потоком данных (Data Flow). Этот принцип формулируется следующим образом: все команды выполняются только при наличии всех операндов (данных), необходимых для их выполнения. Поэтому в программах, используемых для потоковой обработки, описывается не поток команд, а поток данных. Отметим следующие особенности управления потоком данных, характерные для Data Flow:

команду со всеми операндами (с доставленными операндами) можно выполнять независимо от состояния других команд, т. е. появляется возможность одновременного выполнения множества команд (первый уровень параллелизма);

отсутствует понятие адреса памяти, так как обмен данными происходит непосредственно между командами;

обмен данными между командами четко определен, поэтому отношение зависимости между ними обнаруживается легко (функциональная обработка);

поскольку управление командами осуществляется посредством передачи данных между ними, то нет необходимости в управлении последовательностью выполнения программы, т. е. имеет место не централизованная, а распределенная обработка.

Таким образом, параллелизм в таких системах может быть реализован на двух уровнях:

на уровне команд, одновременно готовых к выполнению и доступных для параллельной обработки многими процессорами (при наличии соответствующих операндов);

на уровне транспортировки команд и результатов их выполнения через тракты передачи информации (реализуемые в виде сетей).

Достоинством машин потоков данных является высокая степень однородности логической структуры и трактов передачи информации, что позволяет легко наращивать вычислительную мощность.

Для рассмотренной архитектуры существует ряд факторов, снижающих максимальную производительность:

в случае, когда число команд, готовых к выполнению, меньше числа процессоров, имеет место недогрузка обрабатывающих элементов;

перегрузка в сетях передачи информации; из соображений стоимости максимальная пропускная способность сетей достигается только для ограниченного числа вариантов взаимодействия между командами, что приводит к временным задержкам.

Существенный недостаток Data Flow-машин заключается в том, что достижение сверхвысокой производительности целиком возлагается на компилятор, осуществляющий распараллеливание вычислительного процесса, и операционную систему, координирующую функционирование процессоров и трактов передачи информации. Необходима разработка соответствующих языков программирования высокого уровня и подготовка пакетов приложений для решения реальных задач.

Необходимо упомянуть, что существуют и другие классификации вычислительных систем, преследующие следующие цели:

облегчать понимание того, что достигнуто на сегодняшний день в области архитектур вычислительных систем, и какие архитектуры имеют лучшие перспективы в будущем;

подсказывать новые пути организации архитектур — речь идет о тех классах, которые в настоящее время по разным причинам пусты;

показывать, за счет каких структурных особенностей достигается увеличение производительности различных вычислительных систем; классификация может служить моделью для анализа производительности.

Скилликорн в 1989 году разработал подход, призванный преодолеть недостатки классификации Флинна. Предлагается рассматривать архитектуру любого компьютера как абстрактную структуру, состоящую из четырех компонент:

процессор команд (IP) — функциональное устройство — интерпретатор команд;

процессор данных (DP) — функциональное устройство — преобразователь данных, иерархия памяти (IM,DM)— запоминающее устройство, переключатель—абстрактное устройство связи между процессорами и памятью.

Далее рассматриваются обобщенные функции каждой компоненты в компьютере в целом, в терминах операций, связей и переключателей, что позволяет построить архитектуру машины. Так, все матричные процессоры имеют переключатель типа 1-я для связи единственного процессора команд со всеми процессорами данных. Если каждый процессор данных имеет свою локальную память, связь будет описываться как п-п. Если каждый процессор команд может связаться с любым другим процессором, связь будет описана как п-п.

Классификация Д. Скилликорна состоит из двух уровней. На первом уровне она проводится на основе восьми характеристик:

количество процессоров команд (IP);

число запоминающих устройств (модулей памяти) команд (IM);

тип переключателя между IP и IM;

количество процессоров данных (DP);

число запоминающих устройств (модулей памяти) данных (DM);

тип переключателя между DP и DM;

тип переключателя между IP и DP;

тип переключателя между DP и DP.

Например, для машин с сильно связанными мультипроцессорами, соединенными с модулями памяти с помощью динамического переключателя, при одинаковой задержке при доступе любого процессора к любому модулю памяти описание в данной классификации выглядит так:

(n, п, п-п, п, n, пхп, п-п, нет), а архитектура — так, как показано на рис. 2.16:

Используя введенные характеристики и предполагая, что рассмотрение количественных характеристик можно ограничить только тремя возможными вариантами значений: 0, 1 и я, можно получить 28 классов архитектур.

В классах 1—5 находятся компьютеры типа dataflow и reduction, не имеющие процессоров команд в обычном понимании этого слова. Класс 6 — это классическая фон-неймановская последовательная машина. Все разновидности матричных процессоров содержатся в классах 7—10. Классы 11 и 12 отвечают компьютерам типа MISD-классификации Флинна и на настоящий момент, по мнению автора, пусты. Классы с 13-го по 28-й занимают всесозможные варианты мультипроцессоров, причем в 13—20-м классах находятся машины с достаточно привычной архитектурой, в то время как архитектура классов 21—28 пока выглядит экзотично.

На втором уровне классификации уточняется описание, сделанное на первом уровне, с добавлением возможности конвейерной обработки в процессорах команд и данных.

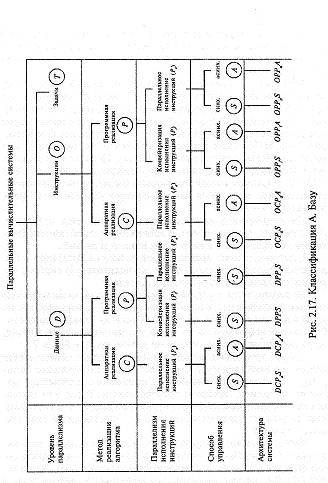

В классификации, предложенной А. Базу (A.Basu) (рис. 2.17), делается попытка описать любую вычислительную систему через последовательность проектных решений.

На первом этапе определяется уровень параллелизма на уровне данных (обозначается буквой D на рис. 2.17 ), параллелизм на уровне команд обозначается буква О, если же компьютер способен одновременно выполнять целые последовательности команд, то рассматривается параллелизм на уровне задач — буква Т.

Второй уровень в классификационном дереве соответствует методу реализации алгоритма. Системам, использующим аппаратную (при помощи микросхем) реализацию алгоритмов целиком, например, быстрого преобразование Фурье или произведения матриц, соответствует буква Сна рис. 2.17, а системам, использующим традиционный способ программной реализации, — буква Р.

Третий

уровень конкретизирует тип параллелизма,

используемого для обработки инструкций