Опис лічильника у вигляді кінцевого автомата

Опис лічильника у вигляді кінцевого автомата звільняє розроблювача від необхідності конкретизувати зв'язки, що існують між елементами пристрої, зводячи опис до запису бажаного алгоритму функціонування.

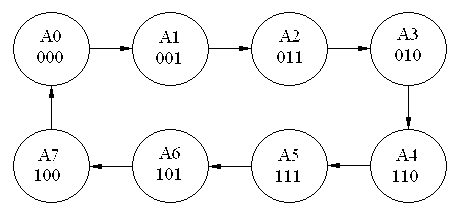

Проілюструємо сказане на прикладі лічильника, що формує на виході код Грея. Граф переходів такого лічильника наведений на рис. 18.

Нижче наведене текстовий опис трирозрядного лічильника, що формує на виході код Грея. Лічильник постачений входами асинхронного скидання й дозволу роботи.

Рис. 18.

SUBDESIGN COUNT_MACHINE

(

CLK, RESET, ENABLE : INPUT;

Q[2..0] : OUTPUT;

)

VARIABLE

AA : MACHINE OF BITS (Q[2..0]) WITH STATES

(

A0 = B"000",

A1 = B"001",

A2 = B"011",

A3 = B"010",

A4 = B"110",

A5 = B"111",

A6 = B"101",

A7 = B"100"

);

BEGIN

AA.(CLK,RESET,ENA) = (CLK, !RESET, ENABLE);

CASE AA IS

WHEN A0 =>AA = A1;

WHEN A1 =>AA = A2;

WHEN A2 =>AA = A3;

WHEN A3 =>AA = A4;

WHEN A4 =>AA = A5;

WHEN A5 =>AA = A6;

WHEN A6 =>AA = A7;

WHEN A7 =>AA = A0;

END CASE;

END;

Нижче наведений розділ рівнянь, запозичений з файлу звіту (report file), що містить відомості про функції алгебри логіки, синтезованих програмою для реалізації заданого алгоритму роботи. Тут же зазначено, що для реалізації пристрою компілятор використав D-тригер із входом дозволу роботи.(DFFE).

** EQUATIONS **

CLK : INPUT;

ENABLE : INPUT;

RESET : INPUT;

-- Node name is 'Q0~' from file "count_machine.tdf" line 7, column 24

-- Equation name is 'Q0~', location is LC1_B17, type is buried.

Q0~ = DFFE( _EQ001, GLOBAL( CLK), GLOBAL( RESET), VCC, ENABLE);

_EQ001 = Q1~ & Q2~

# !Q1~ & !Q2~;

-- Node name is 'Q0' from file "count_machine.tdf" line 4, column 2

-- Equation name is 'Q0', type is output

Q0 = Q0~;

-- Node name is 'Q1~' from file "count_machine.tdf" line 7, column 24

-- Equation name is 'Q1~', location is LC7_B17, type is buried.

Q1~ = DFFE( _EQ002, GLOBAL( CLK), GLOBAL( RESET), VCC, ENABLE);

_EQ002 = Q1~ & !Q2~

# !Q0~ & Q1~

# Q0~ & !Q2~;

-- Node name is 'Q1' from file "count_machine.tdf" line 4, column 2

-- Equation name is 'Q1', type is output

Q1 = Q1~;

-- Node name is 'Q2~' from file "count_machine.tdf" line 7, column 24

-- Equation name is 'Q2~', location is LC3_B17, type is buried.

Q2~ = DFFE( _EQ003, GLOBAL( CLK), GLOBAL( RESET), VCC, ENABLE);

_EQ003 = Q0~ & Q2~

# !Q0~ & Q1~;

-- Node name is 'Q2' from file "count_machine.tdf" line 4, column 2

-- Equation name is 'Q2', type is output

Q2 = Q2~;

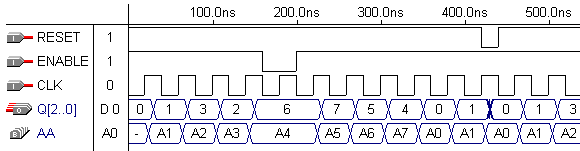

Часові діаграми, що пояснюють роботу лічильника, наведені на рис. 19.

Рис.19.

Опис на вентильному рівні

Представлені вище варіанти опису лічильників припускають автоматичну реалізацію процедури синтезу в рамках пакета MAX+plus II.

Однак лічильник можна описати й на вентильному рівні, здійснивши процедуру синтезу вручну. Нижче наведено текстовий опис чотирирозрядного двійкового лічильника, реалізованого на Т - тригерах, що має входи асинхронного скидання (RESET) і установки (SET), вхід дозволу роботи (ENABLE), вхід, що визначає напрямок лічби (IN/DEC), і вхід, що змінює момент зміни вихідного коду (CLK_MOMENT).

-- Чотирирозрядний Реверсний лічильник, описаний на вентильному рівні.

-- Якщо сигнал зміни напрямку лічби IN_DEC не використовується, лічильник

-- працює як підсумовуючий. Залежно від сигналу CLK_MOMENT можлива

-- робота лічильник як по фронті,так і по зрізі імпульсу генератора,що задає.

SUBDESIGN COUNT_CHIP

(

CLK, RESET, ENABLE, SET : INPUT = VCC;

IN_DEC, CLK_MOMENT : INPUT = GND;

Q[3..0] : OUTPUT;

)

VARIABLE

TR[3..0] : TFFE;

BEGIN

TR[].(CLRN, PRN, ENA) = (RESET, SET, ENABLE);

TR[0].T = VCC;

IF CLK_MOMENT THEN

TR[].CLK = CLK;

IF USED (IN_DEC) GENERATE

IF IN_DEC THEN

TR[1].T = TR[0].Q;

TR[2].T = TR[1].Q & TR[0].Q;

TR[3].T = TR[2].Q & TR[1].Q & TR[0].Q;

ELSE

TR[1].T = !TR[0].Q;

TR[2].T = !TR[1].Q & !TR[0].Q;

TR[3].T = !TR[2].Q & !TR[1].Q & !TR[0].Q;

END IF;

ELSE GENERATE

TR[1].T = TR[0].Q;

TR[2].T = TR[1].Q & TR[0].Q;

TR[3].T = TR[2].Q & TR[1].Q & TR[0].Q;

END GENERATE;

ELSE

TR[].CLK = !CLK;

IF USED (IN_DEC) GENERATE

IF IN_DEC THEN

TR[1].T = TR[0].Q;

TR[2].T = TR[1].Q & TR[0].Q;

TR[3].T = TR[2].Q & TR[1].Q & TR[0].Q;

ELSE

TR[1].T = !TR[0].Q;

TR[2].T = !TR[1].Q & !TR[0].Q;

TR[3].T = !TR[2].Q & !TR[1].Q & !TR[0].Q;

END IF;

ELSE GENERATE

TR[1].T = TR[0].Q;

TR[2].T = TR[1].Q & TR[0].Q;

TR[3].T = TR[2].Q & TR[1].Q & TR[0].Q;

END GENERATE;

END IF;

Q[] = TR[].Q;

END;

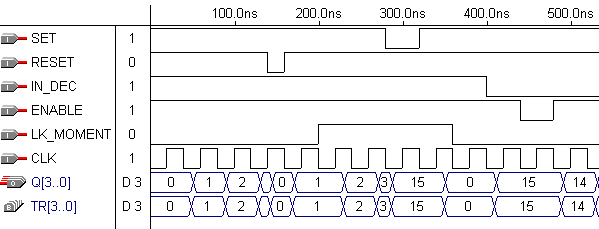

Часові діаграми, що пояснюють роботу лічильника, наведені на рис. 20.

Рис. 20.

Федеральне агентство по утворенню

___________________________________________________________

«МАТІ» - Російський державний технологічний університет

їм. К.Е. Ціолковського

_____________________________________________________________________

КАФЕДРА « ЕЛЕКТРОНІКИ Й ІНФОРМАТИКИ»